重温FPGA开发20

开发 20 FPGA 重温

2023-09-14 09:09:12 时间

基于verilog系统函数语法的按键消抖

讲解实用的TB编写语法

随机函数:

random

优化 testbench文件

`timescale 1ns/1ns

module key_filter_tb();

reg clk;

reg reset;

reg key;

wire key_p_flag;

wire key_r_flag;

// 例化

key_filter key_filter(

clk,

reset,

key,

key_p_flag,

key_r_flag

);

initial clk = 1;

always#10 clk = ~clk;

initial begin

reset = 0;

key = 0;

#201

reset = 1;

#3000;

press_key(2); // 调用这个task

end

reg [31:0] rand;

initial begin

rand = $random(200) % 10000000;

#rand key= ~key;

end

task press_key();

input [3:0] seed;

begin

key = 1;

#20000000;

repeat(5) begin

rand = {$random(seed)} % 10000000;

#rand key= ~key;

end

key = 0;

#40000000;

// 释放按键

repeat(5) begin

rand = {$random(seed)} % 10000000;

#rand key= ~key;

end

key = 1;

#40000000;

end

endtask

endmodule

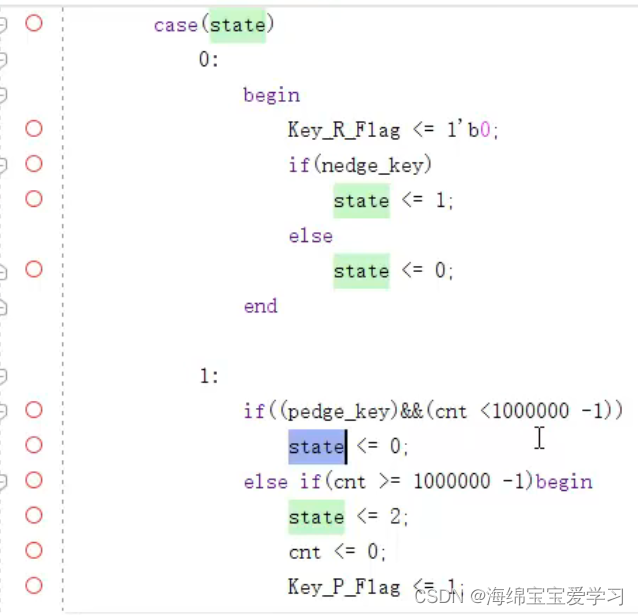

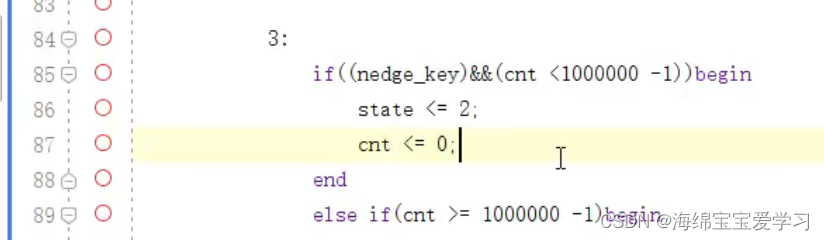

发现有个问题是,key flag的时间不对,分析结果,看子模块的信号,cnt在下一次的信号的时候,没有清零,在回到idle的状态的时候没有清零。

cnt 没有清零

相关文章

- 【Linux】嵌入式开发,在Linux中使用C语言对标准I/O库文件的替换Copy

- Delphi XE之路(13)开发数据库三层应用的DataSnap

- Mobile Web开发 处理设备的横竖屏

- 高并发 Nginx+Lua OpenResty系列(4)——Lua 模块开发

- 【斗医】【2】Web应用开发20天

- 【斗医】【1】Web应用开发20天

- 【斗医】【12】Web应用开发20天

- 【斗医】【10】Web应用开发20天

- 【斗医】【7】Web应用开发20天

- 【斗医】【6】Web应用开发20天

- 【斗医】【4】Web应用开发20天

- 【斗医】【3】Web应用开发20天

- 【斗医】【14】Web应用开发20天

- 【斗医】【13】Web应用开发20天

- Qt音视频开发20-海康sdk本地播放

- SAP UI5 应用开发教程之六十六 - 基于 OData V4 的 SAP UI5 表格控件如何实现删除功能试读版

- iOS音视频开发十:视频解封装,从 MP4 解出 H.264/H.265

- [转载]VB网络聊天程序的开发(5)_彭世瑜_新浪博客

- 【Android 逆向】Android 逆向通用工具开发 ( PC 端工具 hacktool 启动 main 函数分析 | hacktool 工程中的核心类 HackCommand 分析 )

- 20出头的应届生(软件测试),如何进阶自动化、测试开发?

- ZYNQ - 嵌入式Linux开发 -04- petalinux和Xilinx_SDK2018.3安装