16 verilog基础语法-设计层次描述

基础 设计 语法 16 Verilog 描述 层次

2023-09-14 09:16:17 时间

虚拟机:VMware-workstation-full-14.0.0.24051

环 境:ubuntu 18.04.1

应用工具:VCS(verilog compiled simulator,编译型代码仿真器)

一、学习内容

二、设计层次描述

(1)门级描述

- 最直观的描述电路结构

- 最底层的电路描述

- 门声明语句:

【例 1】门级描述2选1

【例 1】门级描述2选1

module MUX2x1(z, d0, d1, s);

output z;

input d0, d1, s;

and u0 (t0, d0, sbar) ,

u1(t1, d1, s);

not u2 (sbar, s);

or u3 (z, t0, t1);

endmodule

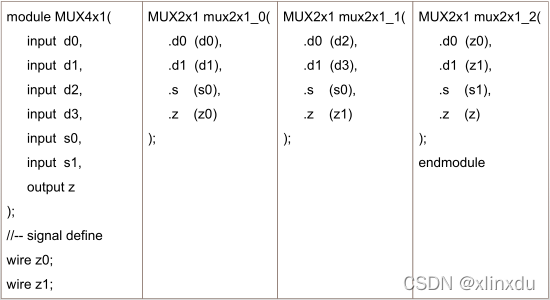

- 有已有模块构成更层次的模块

MUX2x1 mux2x1_0(z0,d0,d1,s0);

MUX2x1 mux2x1_0(

.d0 (d0),

.d1 (d1),

.s (s0),

.z (z0)

);

(2)行为级描述

- 其抽象程度远高于结构描述,相当于高级编程语言

- 描述设计实体时,无需知道电路结构,只需知道输入与输出信号的行为

module sample_ff(clk, rstn, din, dout);

input clk, rstn;

input [3:0] din;

output [3:0] dout;

reg [3:0] data;

assign dout = data;

always @(posedge clk or negedge rstn) begin

if(!rstn) begin

data <= 4’b0;

end

else begin

data <= din;

end

end

endmodule

(3)混合层次描述

- 以上各种层次描述方式可以 任 意 混 合使用

- 一个复杂电路的完整Verilog HDL模型是由 若 干 个Verilog HDL模块构成的,每一个模块又可以由 若 干 个 子 模 块构成。这些模块可以分别用不同抽 象 级 别的Verilog HDL描述,在一个模块中也可以有多种级别的描述

- 利用Verilog HDL语言结构所提供的这种功能就可以构造模块间的清晰层次结构来描述极其复杂的大型设计。

三、思考和小结

(1)思考

- Verilog HDL中都有哪些设计层次描述?

- 半加器Verilog:用门级描述。

- 两个半加器verilog实现一个全加器

(2)小结

作者:xlinxdu

版权:本文版权归作者所有

转载:未经作者允许,禁止转载,转载必须保留此段声明,必须在文章中给出原文连接。

相关文章

- Java ClassLoader基础及加载不同依赖 Jar 中的公共类

- Go语言基础之接口

- LoadRunner基础入门教程

- vue框架-基础5-vue-使用第三方ui组件快速开发页面,vuetify

- c语言基础

- mongodb基础整理篇————设计[四]

- 【基础入门题030】《孙子算经》之鸡兔同笼

- C语言/C++基础之万有引力定律

- Atiti 高并发程序设计 艾提拉著 目录 1. 第—部分 基础知识2 1.1. 第1章 并行计算机的硬件基础 1.1 并行计算机的组成 1.2 共享存储器多处理器系统 1.3 消

- Flutter学习 — 设计基础

- 第21篇 基础 (二十一)可视化UI设计—实现编辑框字体颜色格式的变化

- [译]Vulkan教程(15)图形管道基础之RenderPass

- 007-多线程-基础-ThreadLocal原理分析-线程变量副本

- TensorFlowX.Y核心基础与AI模型设计10:基于tf.estimator.DNNClassifier模型、自定义模型

- TensorFlowX.Y核心基础与AI模型设计07:模型构建实战

- TensorFlowX.Y核心基础与AI模型设计06:TF2模型的输入输出思想、模型保存为单文件多文件、加载模型输入参数

- 6.1 jmeter基础-元件的作用域

- Appium基础 — 元素定位(一)

- 【java基础】LinkedList源码解析

- 一起学时序分析之基础时序参数