【CDC 设计】FPGA 跨时钟域设计方法

目录

跨时钟域介绍

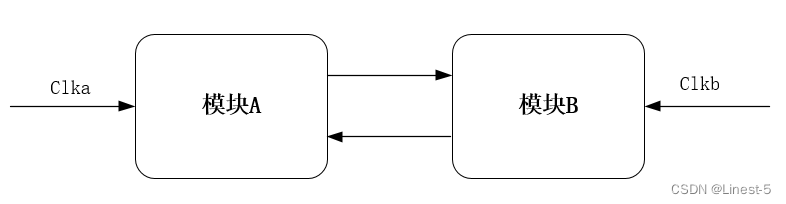

当模块 A 以时钟 Clka 和模块 B 以时钟Clkb,进行数据交互时,两模块的数据时钟不同,如果直接相互传递数据,很可能会导致数据据再传输过程中出现错误:比如数据错误、遗漏、重复等。这时候就需要跨时钟域处理,让数据准确传递。

建立时间和保持时间

建立时间

Setup Time:时钟信号上升沿到来之前,输入信号数据需要维持一定时间的稳定状态,这个“一定时间”就是建立时间。

保持时间

Hold Time:时钟信号上升沿到来之后,输入信号数据也需要保持一定时间的不变,这个“一定时间”就是保持时间。

局部同步设计概念

跨时钟域的问题

- 亚稳态

- 同步失败

同步化

- 同步器

- 保持寄存器和握手

- 异步 FIFO 设计

多时钟域设计的分类

全同步设计

- 只有一个时钟

全异步设计

- 没有时钟

全局异步,局部同步设计

- 多个独立时钟域,同一时钟域内同步

- 这是我们关心的多时钟域设计

- 不可避免,单一时钟不能满足设计的需求

亚稳态

- 什么是亚稳态

- 引起亚稳态的原因

- 亚稳态对系统可靠性的危害

- 如何减少亚稳态的风险

什么是亚稳态

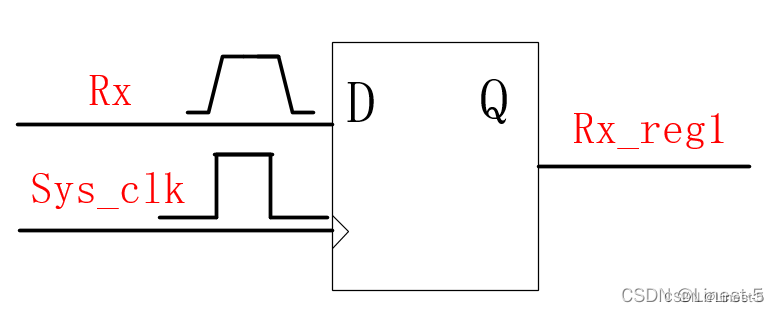

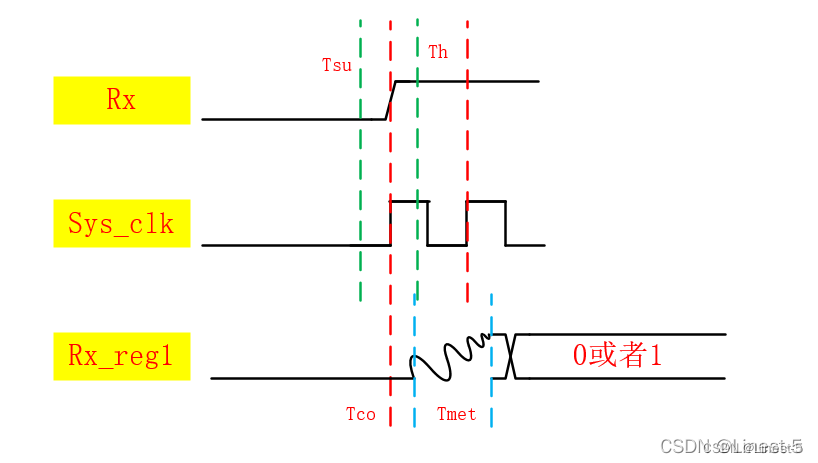

如图所示,当sys_clk时钟信号上升沿踩到Rx信号的变化间隙时,此时输出的Rx_reg1信号就会出现亚稳态,其输出信号就会出现震荡、毛刺或者固定在某一电压值,而不是等于D端输入的值,经过震荡之后,Q端会输出0或者1。这就会产生亚稳态。

引起亚稳态的原因

再数据跳变期间采样,建立时间或保持时间不满足

- 跨时钟域的信号和同步时钟之间的关系不能确定

- 单一时钟域内工具确保建立时间、保持时间,不出现亚稳态

亚稳态对系统可靠性的危害

同步失败、系统失败,按概率出现:发生概率可能达到可靠性要求无法接受的程度。

如何减少亚稳态的风险

单一时钟域内信号

- 工具检查每个触发器的建立时间、保持时间,确保其不出现亚稳态

跨时钟域的信号

- 没有工具可以保证其可靠性

- 静态时序分析其应该设置 False Path 约束

- 只能靠逻辑设计来保证:同步化设计

同步化技术

根据跨时钟域信号的特点来选择同步化方法:

- 同步器:控制信号

- 保持寄存器和握手:地址或数据总线信号

- 异步 FIFO 设计:数据总线信号

同步器

为什么使用两级寄存器(接收时钟域)

因为两级寄存是一级寄存概率的平方,两级并不能完全消除亚稳态危害,但是提高了可靠性,减少亚稳态发生的概率

一级寄存大概率无法改善亚稳态,三级寄存相对于二级寄存改善不大,所以二级寄存是最好的选择

同步器的分类

- 电平同步器

- 边沿检测同步器

- 脉冲同步器

电平同步器

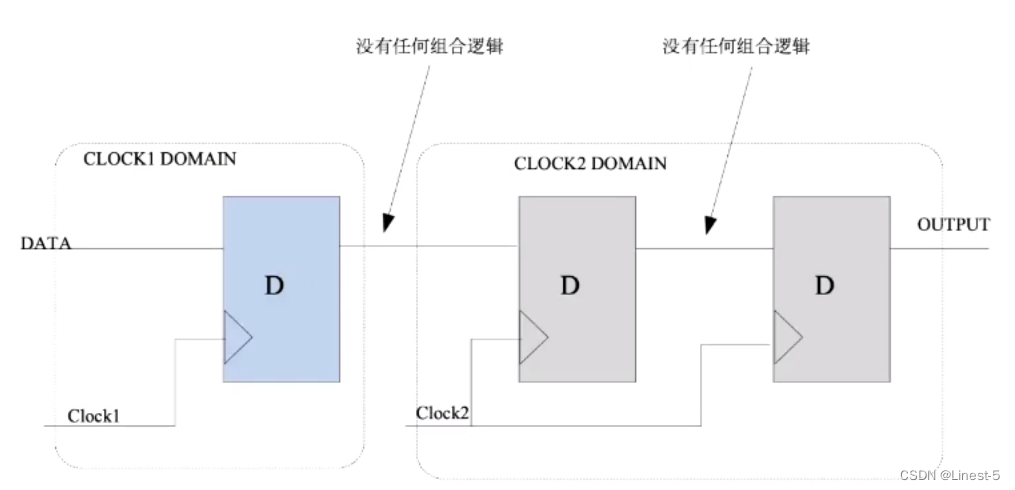

下图是电平同步器的原理图,可以看到对于两个时钟 clk1、clk2,再处理两个时钟的直接按的数据传输时,使用了两级寄存器进行数据同步,但是电平同步器只能对两个频率相同、相位不同的时钟之间进行处理,对于频率不同的时钟就无法处理。

边沿检测同步器

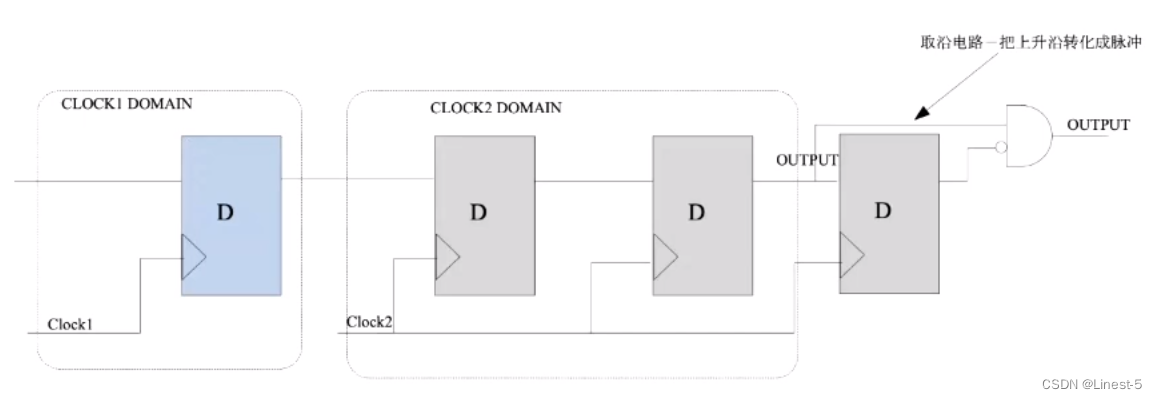

下图是边沿检测同步器,用于慢时钟域(clk1)到快时钟域(clk2)的同步处理。慢到快可能会使数据重复采集。解决办法:取沿电路:把上升沿即数据的变化转化成脉冲,然后让输出与寄存的输出取反相与,这样就可以检测出上升沿并将上升沿转换成脉冲。

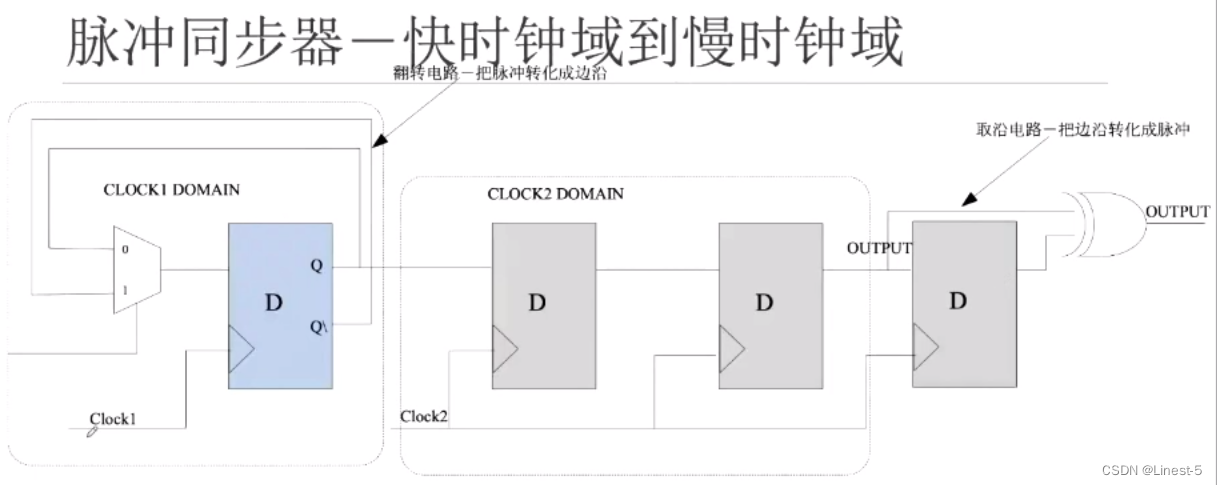

脉冲同步器

下图是脉冲同步器,用于快时钟域(clk1)到慢时钟域(clk2)的同步处理,快到慢可能会使数据出现遗漏采集,和边沿检测同步器有着相类似的原理。

同步器设计推荐的做法

- 同步器单独成模块,引入两个独立时钟

- 其他模块都设计为单一时钟模块,完全同步模块

- 以时钟域作为信号命名的前缀

- 静态时序分析的时候,对同步器模块异步输入信号的谁当false path:用通配符

使用同步器需要注意的问题

- 原时钟域的寄存器和新时钟域的两个寄存器之间都不能有组合逻辑

- 快时钟域到慢时钟域

- 多位控制信号跨时钟域

- 总线信号跨时钟域

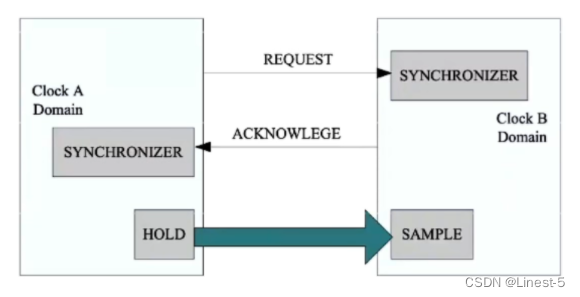

总线信号跨时钟域

如果直接使用同步器会带来某些问题

正确方法

- 保持寄存器加握手信号

- 异步 FIFO 设计

以上两种方法都要使用同步器

保持寄存器和握手

FIFO

同步 FIFO:写时钟和读时钟为同一个时钟

异步 FIFO:写时钟和读时钟为独立时钟

跨时钟域的数据信号需要用到异步 FIFO,隔离时钟域,匹配读写速度

FIFO 写满和读空标志的产生

读写指针比较产生

- 同步 FIFO 直接把读写时钟比较或运算产生

- 异步 FIFO 由于读写指针不同时钟域,比较前指针必须同步化

- 由于二进制的指针会出现多位同时跳变,直接由同步器进行同步化会有问题

异步 FIFO 设计

根据 full 和 empty 产生方法分为:

- Binary Code 结合保持握手

- 二进制寻址,二进制同步化后比较产生空满标志

- Gary Code 结合同步器

- 二进制寻址,Gary码同步化后,比较产生空满标志

- Gary码制寻址,Gary码同步化后,比较产生空满标志

总结

多时钟域设计不可避免

减少亚稳态的风险

工具不能保证,只能靠设计来保证

同步化技术的选用要结合具体的情况

- 同步器

- 保持和握手

- 异步 FIFO

相关文章

- 标准低功耗设计方法(二)

- 低功耗设计方法--电源门控示例(二)

- 《软件方法》自测题解析-002设计为了应变

- 《软件方法》自测题解析007:设计工作流,有彩蛋

- 《软件方法》自测题解析-005:哪个混淆了需求和设计的区别

- 常用的测试用例设计方法有那些类型_测试用例设计

- 3D建筑设计软件首选软件Vectorworks 2023|更快的工作流和更好的设计方法

- 台积电公布将模拟设计迁移到3nm的方法

- 2022最新windows上传ipa文件到app store的方法

- 【Android 应用开发】Android UI 设计之 TextView EditText 组件属性方法最详细解析

- 字体设计|从历史中汲取字体设计的方法

- 【软件测试系列三】《测试用例编写原则与设计方法》

- 对比损失思想设计loss function的方法

- 智能路灯杆网关如何定制 智慧杆网关设计方法

- Linux下ping命令的使用方法(linux下怎么ping)

- JSP application.getRealPath()方法:获取虚拟路径的真实路径

- Linux 下简单取文件后缀名的方法(linux取文件后缀名)

- 处理Java处理Redis中过期数据的有效方法(redisjava过期)

- 10个方法帮你搞定Web设计风格指南

- MySQL数据库不支持中文字符的原因和解决方法(mysql不能有中文)

- js中设计一段程序,让它能够打印自己的方法收集藏

- XStream使用方法总结附实例代码

- asp.net中文字符串提交乱码的解决方法

- DotNetOnPreRender(EventArgse)事件常用的方法

- .net框架(framework)版本不匹配的解决方法

- 基于Linux系统调用--getrlimit()与setrlimit()函数的方法