【LED灯屏控制器】AG10K 烧录程序(2)

一、预装软件介绍

对于我的电脑,需要预装:

- Quartus II 13.0 版本(64位)

- 安装参考《Quartus II 13.0安装指导书.pdf》

- Cyclone IV 器件库(AG10KSDE176 对标 EP4CE10F17C8【属于Cyclone IV 系列】)

- 安装参考《Quartus II 13.0安装指导书.pdf》

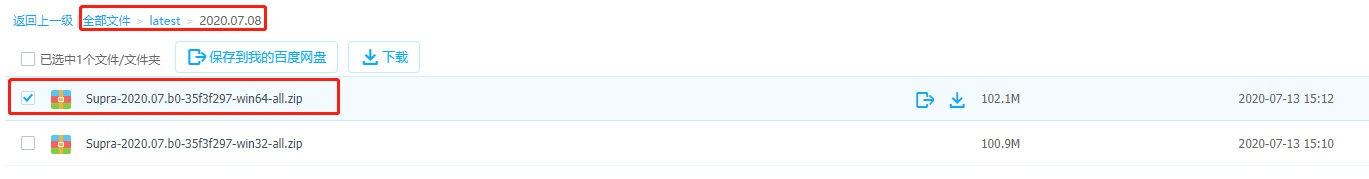

- Supra-2020.07.b0-35f3f297-win64-all

- 安装参考下文

二、Supra安装

安装包见链接:http://pan.baidu.com/s/1eQxc6XG 提取密码—

q59e

选择适合自己系统的版本进行解压即可,这个软件是免安装的!

三、软件开发流程(Compatible 模式)

Compatible 模式是Supra中的一个可选模式,可选模式一共有三个,分别是:COmpatible、Synplicity、Native。

3.1、使用 Qurtus II 13.0 创建工程

参考小梅哥《02_【学习教材】FPGA系统设计与验证实战指南_V2.6.pdf》的2.2.1和2.2.2小节。

用 Quartus II 13.0 基于 Cyclone IV EP4CE10F17 完成原始设计。

注意:创建完工程并设计好源文件后,需要进行一次全编译!特别提醒,先不要进行管脚分配!

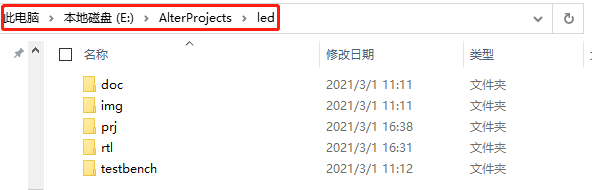

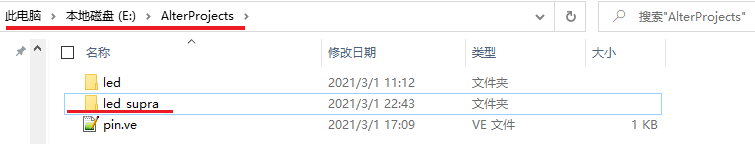

这里我为工程名字取名为led,工程目录结构如下图所示。

我的rtl设计文件led.v内容如下:

功能:持续点亮LED,该LED低电平点亮!

module led(

output OUT

);

assign OUT = 1'b0;

endmodule

3.2、管脚分配

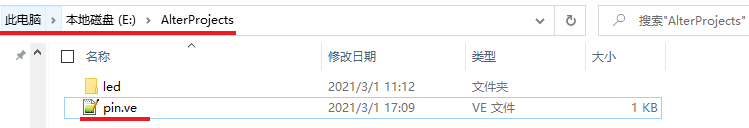

新建一个文本格式的管脚分配文件,命名为<design>.ve(例如:pin.ve),并将其存放在与Quartus工程同级的目录下,如下图所示。

编辑 ve 文件加入 FPGA 的 IO 管脚绑定,管脚名称参考MANUAL_AG10KSDE176.pdf中的管脚说明表格, ve 文件格式如下(管脚设计名称+空格+封装管脚名称):

//网表参考格式如下

rst PIN_89

clk PIN_23

led[0] PIN_157

led[1] PIN_158

……

my_SDRAM_CS SDRAM_CS

my_SDRAM_CLK SDRAM_CLK

my_SDRAM_A0 SDRAM_A0

……

我的pin.ve文件内容如下:

OUT PIN_157

对应原理图,为图中的第一个LED,LED原理图如下图所示:

Supra 会在后面的编译中按照

ve文件分配到 176 封装的 AG10K 具体管脚。 如原Quartus II 13.0工程中有管脚分配信息,需先删除再执行TCL。

3.3、使用 Supra 转换(Migrate)工程

- 1、首先新建一名为

led_supra的目录,作为AG10K的项目目录,该目录与Quartus工程目录同级!层级如下图所示:

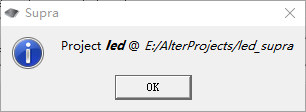

- 2、接着打开

Supra,新建工程(File->Project->New Project),设置工程目录和工程名称。

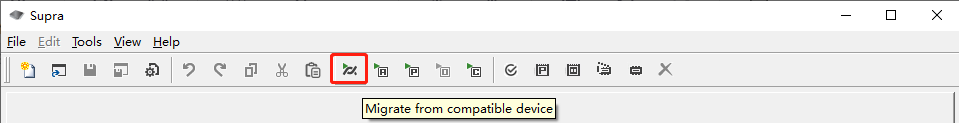

- 3、选择菜单 ”

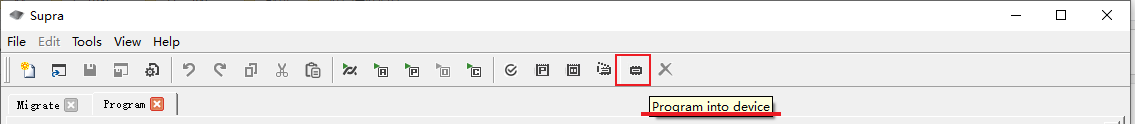

Tools -> Migrate”,或者点击下图所示按钮,进行工程转换!

-

4、在 Migrate 界面依次填入信息为:

- 目标运行目录

<run_dir>(AGM工程目录) - 原始项目目录

<from_dir>(需要精确到.qpf所在文件夹) - 选择设计名称(应自动从

<from_dir>中找到,请点选) - 选择 AGM 器件型号:

AG10KSDE176 - 非管脚兼容器件需要添加

VE文件,即3.2节创建的pin.ve文件 - (了解)非兼容 IP,通过 Supra 产生 IP 文件后再添加

Backward Compatible选项,如果使用老版本Quartus II(无Cyclone IV device)可以选上

- 目标运行目录

填入信息参考,如下图所示:

注意,若窗口过小会隐藏掉一些信息,这时滚轮下拨即可!

- 5、接着点击“

Next”按钮,界面如下图所示:

- 若未创建

AGM的工程目录,可根据输入目录的名称自动产生,选择“Yes”后Supra在AGM的工程目录中自动生成所需文件。

正确运行后会生成af_prepare.tcl等文件。

log 信息如下:

af.exe -B --setup --mode QUARTUS --design led --device AG10KSDE176 --migrate E:/AlterProjects/led/prj --ve E:/AlterProjects/pin.ve -X "set DEVICE_FAMILY 1"

Total IO : 432

Total Pin : 187/12

Top array is built.

Loading architect libraries...

## CPU time: 0:0:0, REAL time: 0:0:0

## Memory Usage: 43MB (43MB)

Warn: Can not find ASF file ./led.asf, create a empty one.

Info: Can not find ASF file ./led.pre.asf, create a empty one.

Info: Can not find ASF file ./led.post.asf, create a empty one.

Setup done...

Next, compile with quartus using one of following 2 approaches:

1) Command line base, run 'quartus_sh -t af_quartus.tcl'

2) GUI base, start quartus GUI, open project led,

select Tools->Tcl Scripts..., load af_quartus.tcl and run

Then, run 'af_run' to generate led bit-stream files

Total 0 fatals, 0 errors, 1 warnings, 2 infos.

Setup migration project from E:/AlterProjects/led/prj done with code 0

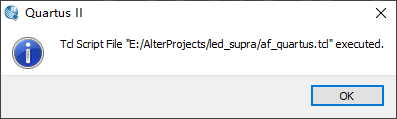

3.4、加载 af_quartus.tcl 文件,综合网表文件

使用 Qurtus II 13.0 打开 supra 工程中的 led.qpf。选择菜单: “Tools -> Tcl Scripts...”,调用工程里的 af_quartus.tcl,运行点击“Run”按钮。

运行

af_prepare.tcl脚本文件,会把ve的内容导入到EP4CE10对应的管脚分配。

Qurtus II 13.0 成功执行 Tcl 后,会综合出 Supra 需要的网表文件(vo)。

接着退出工程,回到 Supra 软件。

点击“Next”按钮。

3.5、Supra工程编译

如下图所示,点击”Finish”按钮, Supra 开始编译工程,可在 Console 界面查看编译信息

耐心等待 x min…

log 信息如下:

af.exe -B --batch --mode QUARTUS -X "set QUARTUS_SDC true" -X "set FITTING timing_more" -X "set FITTER hybrid" -X "set EFFORT highest" -X "set HOLDX default" -X "set SKEW basic"

Mon Mar 01 23:01:01 2021

Using pre-ASF file led.pre.asf.

Total IO : 432

Total Pin : 187/12

Top array is built.

Loading architect libraries...

## CPU time: 0:0:0, REAL time: 0:0:0

## Memory Usage: 43MB (43MB)

Loading route table...

## CPU time: 0:0:12, REAL time: 0:0:13

## Memory Usage: 425MB (425MB)

Using design verilog file E:/AlterProjects/led/prj/simulation/modelsim/led.vo.

Preparing design...

## CPU time: 0:0:0, REAL time: 0:0:0

## Memory Usage: 425MB (425MB)

Pseudo pack design...

Using location file E:/AlterProjects/pin.ve

Packing Statistics

Total Logics : 0/10960 ( 0%)

Total LUTs : 0/10960 ( 0%)

Total Registers : 0/10960 ( 0%)

Total Block Rams : 0/ 46 ( 0%)

Total Multipliers : 0/ 23 ( 0%)

Total PLLs : 0/ 2 ( 0%)

Total Pins : 1/ 187 ( 0%)

Global Signals : 0/ 10 ( 0%)

Total Lonely Datain : 0

Total Lonely Register : 0

Total LUT-FF Pairs : 0

Total Register Packings : 0

Registers with synchronous reset : 0

Registers with asynchronous reset : 0

Registers with sync and async reset : 0

## CPU time: 0:0:0, REAL time: 0:0:0

## Memory Usage: 425MB (425MB)

Filter verilog...

## CPU time: 0:0:0, REAL time: 0:0:0

## Memory Usage: 425MB (425MB)

Read DB design...

## CPU time: 0:0:0, REAL time: 0:0:1

## Memory Usage: 433MB (433MB)

Process design...

## CPU time: 0:0:0, REAL time: 0:0:0

## Memory Usage: 434MB (434MB)

Using design SDC file ./led.sdc.

Using AQF file ./alta_db/alta.aqf.

Using ASF file led.asf.

Placement Statistics

Total Logic Tiles : 0/685 (0.0%)

Total Valid Nets : 0 (0+0)

Total Valid Fanouts : 0 (0+0)

Total Tile Fanouts : 0

Tile Zip Fanins : 0 (-1:-1)

Tile Zip Fanouts : 0 (-1:-1)

Total Ignored Nets : 0

Total Valid Blocks : 0 (0/0)

Total Ignored Blocks : 1

Total Zip Complexities : 0/0 0.00/0.00

Avg Zip Bottleneck : nan nan

Avg Net Bottleneck : nan nan

Total wire cost after placement: 0:0:0(0:0) 0(0)+0(0)+0 0(0)+0

*** Post Placement Timing Report ***

=== User constraints ===

=== Auto constraints ===

Coverage report

User constraints covered 0 connections out of 0 total, coverage: 100.0%

Auto constraints covered 0 connections out of 0 total, coverage: 100.0%

*** End Timing Report ***

route_design -dump ./alta_db/route.tx -replace ./alta_db/replace.tx

Route Design Statistics

Total Routing Nets : 0

Logic Slices : 0/10960 (0.0%)

*** Post Routing Timing Report ***

=== User constraints ===

=== Auto constraints ===

Coverage report

User constraints covered 0 connections out of 0 total, coverage: 100.0%

Auto constraints covered 0 connections out of 0 total, coverage: 100.0%

*** End Timing Report ***

Mon Mar 01 23:01:24 2021

Using post-ASF file led.post.asf.

Mon Mar 01 23:01:27 2021

Total 0 fatals, 0 errors, 0 warnings, 0 infos.

Compile design led done with code 0

编译成功后, Supra 生成用于器件烧写的led.prg 等烧写文件。

转换和编译时产生的 log 文件,保存在工程的 alta_logs 目录下;编译的时序报告,保存在 alta_db 目录下,包括 setup 和 hold 时序的 rpt.gz 压缩文件中。

3.6、器件烧写

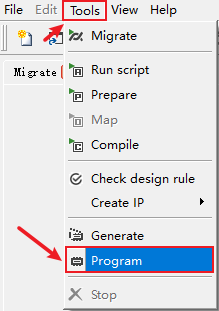

- 1、选择菜单: “

Tools -> Program”,打开Program选项卡,下图所示:

或者点击下图所示按钮打开

Program选项卡:

- 2、连接

USB-Blaster到AG10K评估板的JTAG接口,如下图所示:

- 3、选择拨码开关MSEL1到合适的档位

AG10K 配置说明:

AG10K 配置方式支持 JTAG, AS(Master) 和 PS(Slave) 方式, 可通过 MSEL[2..0]选择。其中 MSEL2 和 MSEL0 已在封装内接到 GND,仅需把外部管脚 MSEL1 按照下表设置,选择不同配置模式。 AS 方式也是通过 JTAG 口直接烧写配置 FLASH。

| 配置方式 | MSEL1 |

|---|---|

| AS | 1 |

| PS | 0 |

| JTAG | 0/1 |

MSEL1部分原理图如下所示:

①、MSEL1 接至GND,即PS方式,下载程序到FPGA的SRAM里,掉电即丢失!

②、MSEL1 接至GND,即AS方式,下载程序到FLASH中,FPGA进行主动配置,掉电仍可保存程序!

这里PS AS 的称呼准确吗???

这里我选择AS方式,即MSEL1 接至GND

- 4、接着选择要烧写的程序,然后点击

Program!

①、AS方式对应的烧写程序名为:led_master.prg

②、PS方式对应的烧写程序名为:led_sram.prg

这里我们当然选择led_master.prg了!

log 信息如下:

af.exe -B -X "set blaster_id 0" -X "source -progress 1000 E:/AlterProjects/led_supra/led_master.prg"

Usb driver connected on device 0

JTAG device ID: 0x01000001

...1000

...2000

...3000

...4000

...5000

...6000

...7000

Usb driver disconnected

Total 0 fatals, 0 errors, 0 warnings, 0 infos.

Program device with led_master.prg done with code 0

3.7、实验现象验证

如下图所示LED常亮!

3.8、补充内容

3.8.1、修改源设计后

如需修改原设计,由于 af_prepare.tcl 已把管脚设置改好, 不用重新执行 tcl, 在 Qurtus II 13.0 中直接编译即可。然后在 Supra 中 Compile 界面进行最后编译。

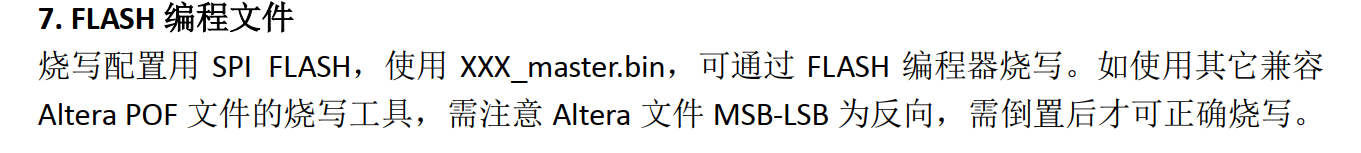

3.8.2、烧写文件类型

<design>_sram. prg文件为片内sram写入,通过JTAG烧写, 掉电即失效,可用于设计调试;<design>_master.prg文件为Master(AS)配置方式下,通过JTAG烧写FLASH的文件;<design>_master.bin为Master(AS)配置方式下,FLASH的通用烧写文件;<design>.bin或 rbf 文件为Slave(PS)配置方式所需文件,rbf文件的字节高低位反向。

Q & A

Q:改动什么需要重新TCL?

- A:当改动引脚绑定后。

其他

参考

- AGM-FPGA-spura软件使用手册.pdf

- AG10K_guide.pdf

- Quartus II 13.0安装指导书.pdf

- AG10K_E176_SDRAM_PCB.pdf【即 AG10K 评估板原理图】

- MANUAL_AG10KSDE176.pdf

- USB Blaster使用指南

- FPGA在AS模式下,程序下载成功,重启后配置失败

- FPGA的AS模式下载成功,不能自动配置运行!

相关文章

- 小程序wxss进阶

- c#实例化继承类,必须对被继承类的程序集做引用 .net core Redis分布式缓存客户端实现逻辑分析及示例demo 数据库笔记之索引和事务 centos 7下安装python 3.6笔记 你大波哥~ C#开源框架(转载) JSON C# Class Generator ---由json字符串生成C#实体类的工具

- 模糊控制器设计源码程序

- 04 C++ - 入门程序

- Aleo隐私智能合约编程__第一章__Aleo SDK的Hello World程序

- 漏洞防范:搭建漏洞靶场DVWA,DVWA之SQL注入漏洞,利用sqlmap把复杂的程序自动化

- 《C语言编程——零基础初学者指南(第3版)》一第2章 编写第一个C程序2.1 概述

- 小程序模板-评分星星

- 微信小程序-从零开始制作一个跑步微信小程序

- 一、微信小程序支付

- VS2012程序打包部署详解

- Java高手速成│编写你第一个数据库程序

- C程序演示产生僵死进程的过程

- Eclipse中运行程序,提示ADB server didn't ACK failed to start daemon

- c#中怎样判断一个程序是否正在运行?

- 学习旧岛小程序 (1) flex 布局