不重叠序列检测

序列 检测 重叠

2023-09-14 09:10:03 时间

不重叠序列检测

题目描述

请编写一个序列检测模块,检测输入信号(a)是否满足011100序列, 要求以每六个输入为一组,不检测重复序列,例如第一位数据不符合,则不考虑后五位。一直到第七位数据即下一组信号的第一位开始检测。当信号满足该序列,给出指示信号match。当不满足时给出指示信号not_match。

模块的接口信号图如下:

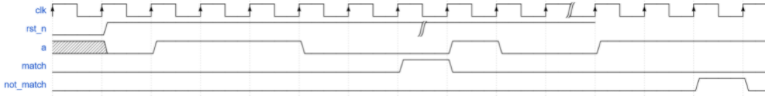

模块的时序图如下:

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input data,

output reg match,

output reg not_match

);

reg [0:2] cnt;//六个时钟的计数

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 3'b0;

else if ( cnt == 3'd5)

cnt <= 3'b0;

else

cnt <= cnt + 1'b1;

end

reg [5:0] data_reg;

always@(*)

begin

case(cnt)

3'd0:data_reg[5] = data;

3'd1:data_reg[4] = data;

3'd2:data_reg[3] = data;

3'd3:data_reg[2] = data;

3'd4:data_reg[1] = data;

3'd5:data_reg[0] = data;

default:data_reg = 6'b0;

endcase

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

match = 1'b0;

else if(data_reg == 6'b011100 && cnt == 3'd5)

match = 1'b1;

else

match = 1'b0;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

not_match = 1'b0;

else if(data_reg != 6'b011100 && cnt == 3'd5)

not_match = 1'b1;

else

not_match = 1'b0;

end

endmodule

知识点

移位寄存器不仅能寄存数据,而且能在时钟信号的作用下使其中的数据依次左移或右移。

相关文章

- Java实现 LeetCode 673 最长递增子序列的个数(递推)

- java实现第五届蓝桥杯扑克序列

- Java实现 蓝桥杯VIP 算法提高 最长公共子序列

- 华为OD机试 - 最长连续子序列(Java & JS & Python)

- QuantitativeFinance:量化金融之金融时间序列分析之ES/ETS/GARCH模型的简介、Box-Jenkins方法-AR/MA/ARMA/ARIMA模型的简介及其建模四大步骤之详细攻略

- Python编程:利用python编程实现对基于时间序列的数据(dataframe格式)按照指定时间范围进行单方向关联,不存在的日期补充为默认的NaN

- 基于时空RBF-NN的混沌时间序列预测(Matlab代码实现)

- 时间序列预测某加密货币

- Python实现Prophet时间序列数据建模与异常值检测(Prophet算法)项目实战

- 【数字信号处理】序列表示与运算 ( 序列乘以常数 | 序列相加 | 序列移位 | 序列尺度变换 )

- VL36-状态机-重叠序列检测;设计一个状态机,用来检测序列1011.

- VL27-不重叠序列检测,检测信号是否满足011100序列,六个一组,连续不断,如果数据中断,则继续第七个开始,又是6个数据一组。

- VL26-含有无关项的序列检测(移位寄存器法采用数组)+检测序列是011_xxx_110,满足条件,match=1。仿真验证正确!

- VL25-输入序列连续的序列检测(采用移位寄存器方法)+亲测正确! 检测输入信号是01110001。指示信号match是1。

- 【数字IC/FPGA】检测最后一个匹配序列的位置

- 【Leetcode刷题Python】674. 最长连续递增序列

- Verilog | 序列检测

- 【Pytorch Lighting】第 5 章:时间序列模型