重温FPGA开发13

串口发送数据任务

使用上一节课设计的串口发送模块,设计一个数据发送器,每10ms以115200的波特率发送一个数据,每次发送的数据比前一个数据大1 (计数器)

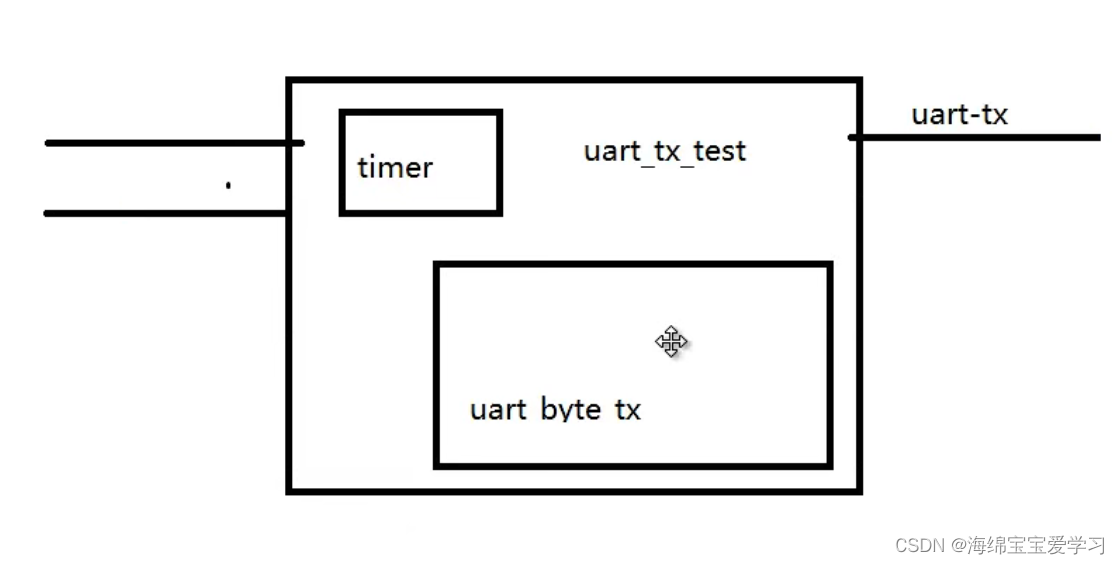

uart_tx_test.v

// 把被测的模块例化进来

module uart_tx_test(

clk,

reset,

uart_tx,

);

input clk;

input reset;

output uart_tx;

reg send_en;

reg [7:0]data;

uart_byte_tx uart_byte_tx(

.clk(clk),

.resnet(resnet),

.data(data),

.send_en(send_en),

.baud_set(3'd4),

.uart_tx(uart_tx),

.tx_done(tx_done)

);

reg [18:0] counter;

always@(posedge clk or negedge reset)

if(!reset)

counter <= 0;

else if(counter == 499999)

counter <= 0;

else

counter <= counter + 1;

always@(posedge clk or negedge reset)

if(!reset)

counter <= 0;

else if(counter == 1)

send <= 1;

else if(tx_done)

send_en <= 0;

always@(posedge clk or negedge reset)

if(!reset)

data <= 0;

else if(tx_done)

data <= data +1'b1;

endmodule

uart_tx_test_tb.v

module uart_tx_test_tb

.usrt_tx_test(

.clk(clk),

.reset(reset),

.uart_tx(uart_tx)

)

initial clk = 1;

always #10 clk = ~clk;

initial begin

reset = 0;

#201;

reset = 1;

#50000000

end

endmodule

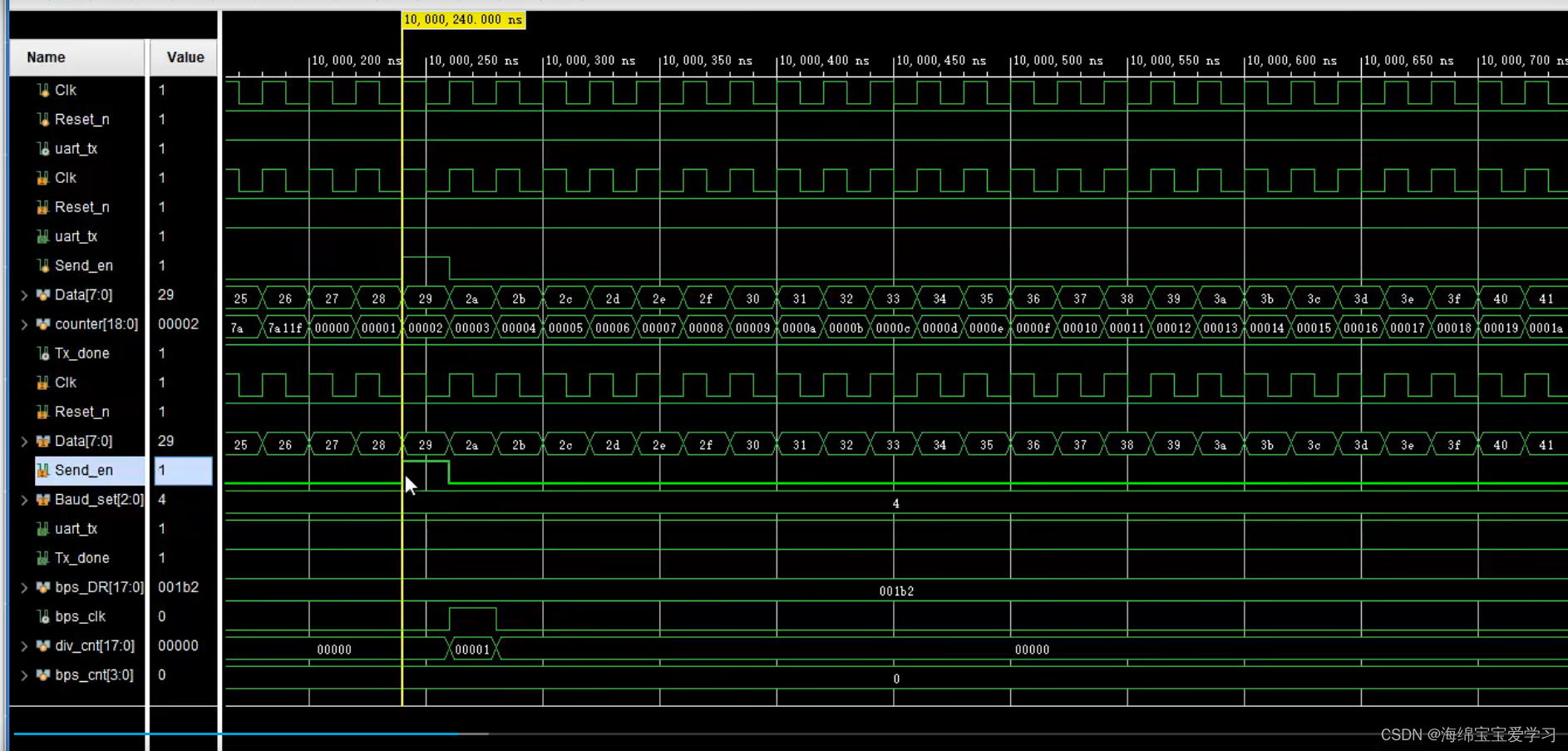

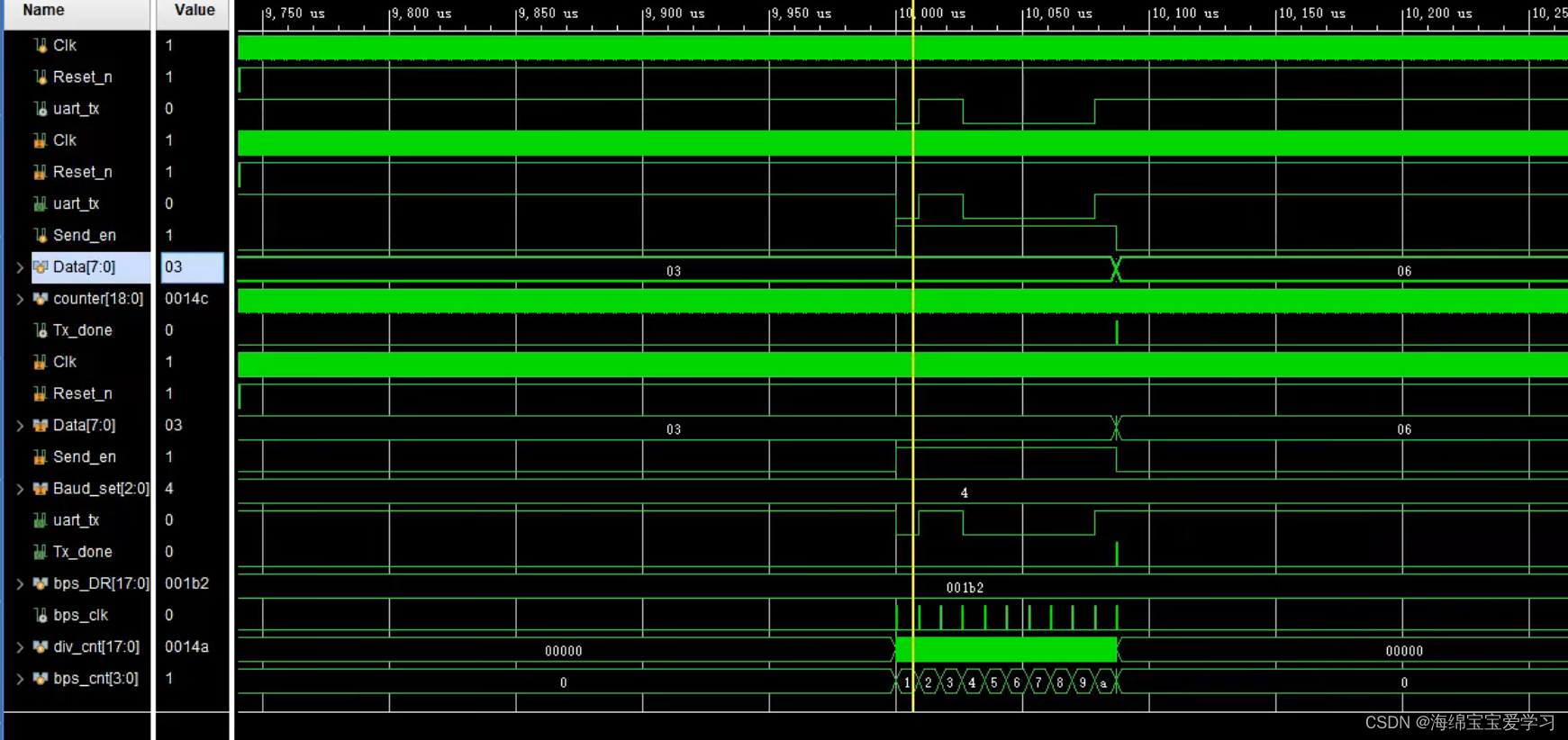

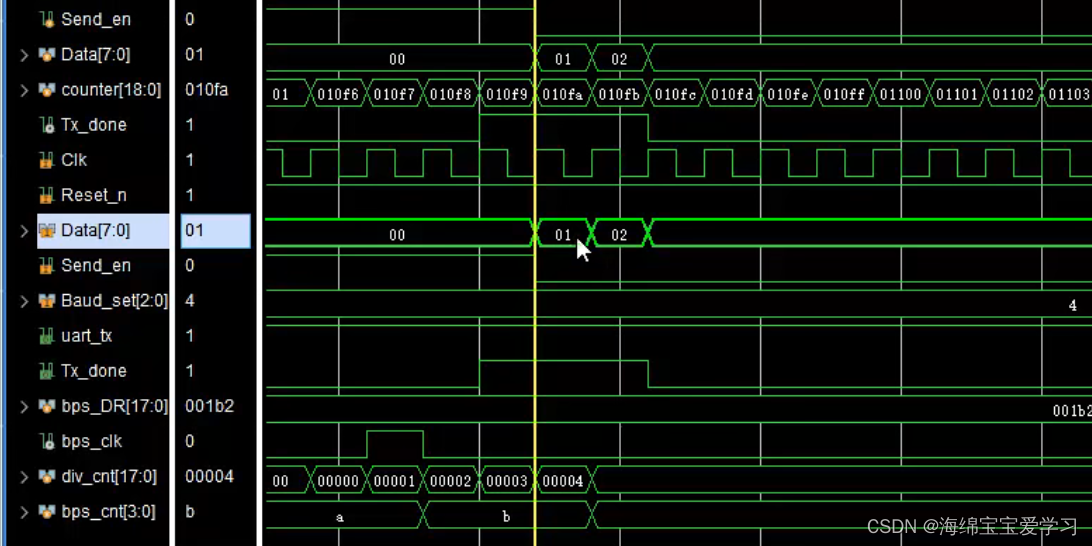

run 一把试试,发现波形不对

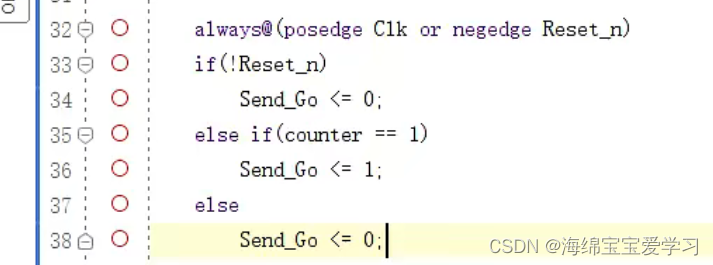

先找 send en只有一个高电平,看看 send en怎么产生的,counter= 1 的时候 send en拉高,那为什么后面又被拉低了呢?现在怀疑 tx_done的信号?为什么 tx done 一直为高呢?什么时候 tx done拉低呢?所以有个bug存在,没有counter 的case 没有1 的情况。锁以tx done永远不能拉低。改为

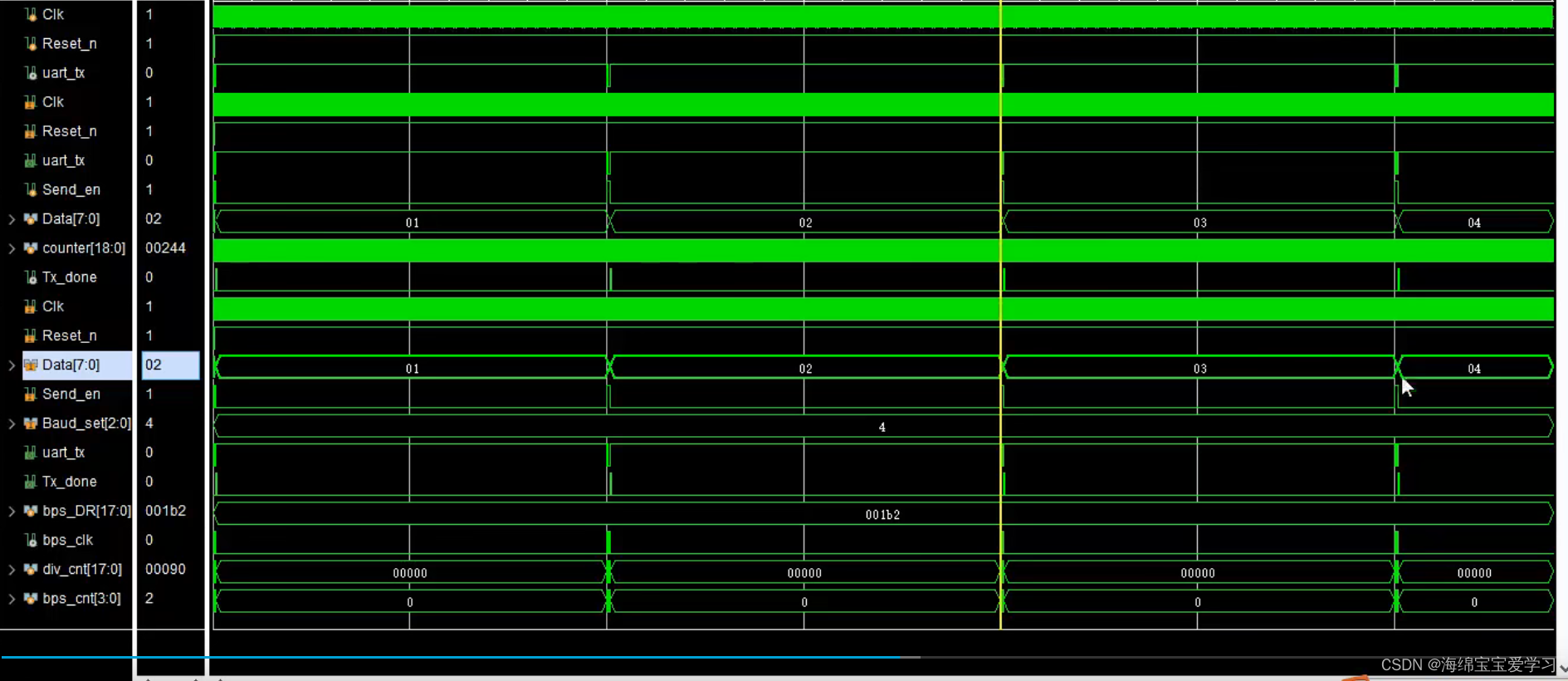

这时候又有bug:data为什么是3 而不是1

data在这里为什么连续加了3次

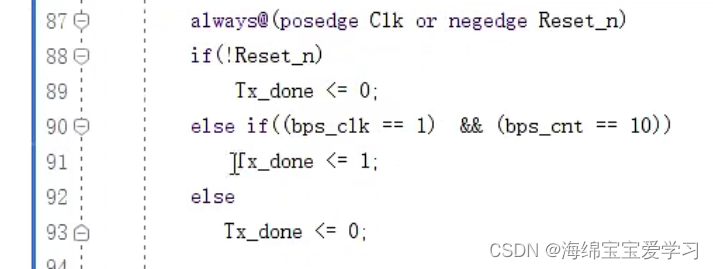

因为检测到tx done 脉冲宽度很重要,应该是一个时钟周期的脉冲,但是现在是3个时钟周期。这时候我们应该确保tx done 每次发送完为一个时钟周期。

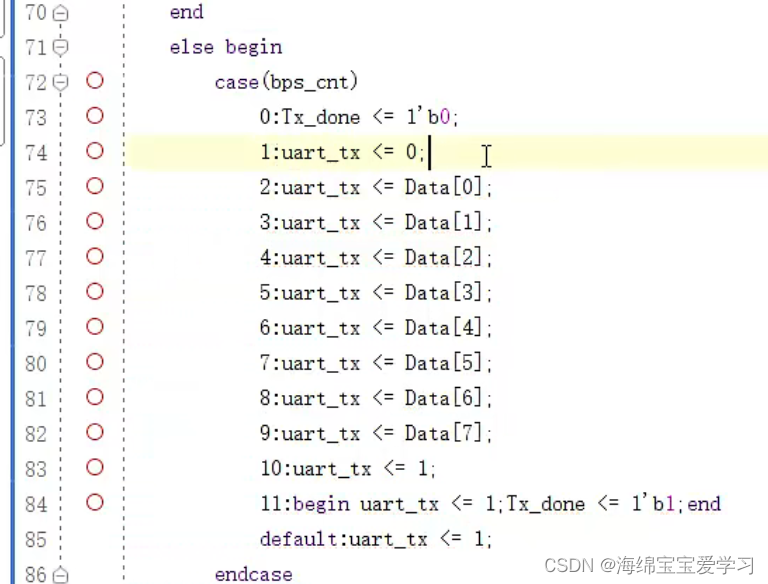

让11 只保持一个时钟周期,当dev count产生 bps clk这个脉冲,然后就为11,但后产生 tx done的信号,检测到 tx done 之后,让send en拉低

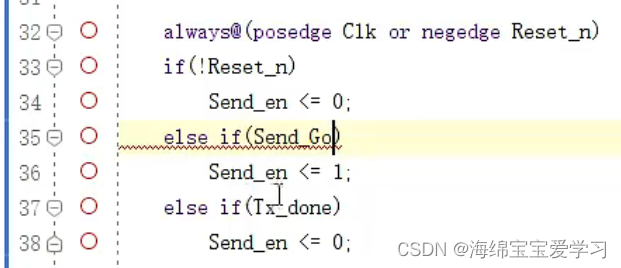

修改为:

tx done 单独拿出来赋值

在这个里面send en完全是主动的视角

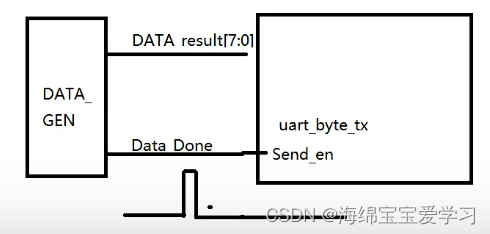

假设有个数据采集模块:

修改一下:

把send en放到uart_byte_tx 内部来完成,添加一个input接口。

只要顶层给我一个 send go信号,我就使能send en信号

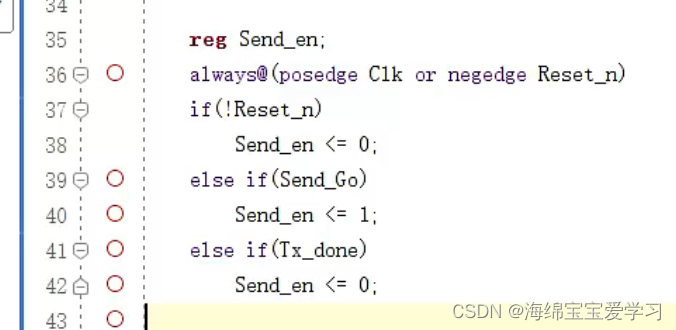

内部的代码:

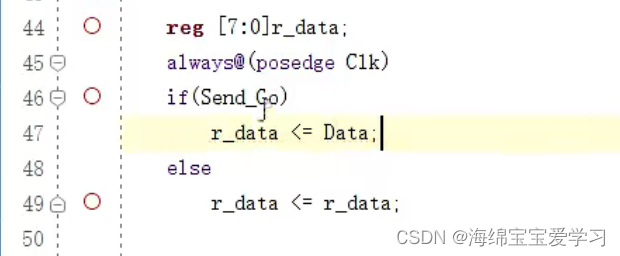

data在直连过来的时候,会不会一直不变?如果在发生的过程中串口的数据忽然变了,一旦外部发送过来,我就立马存下来。内部定义一个寄存器来保存data,每次只要send go的时候 rdata = data:

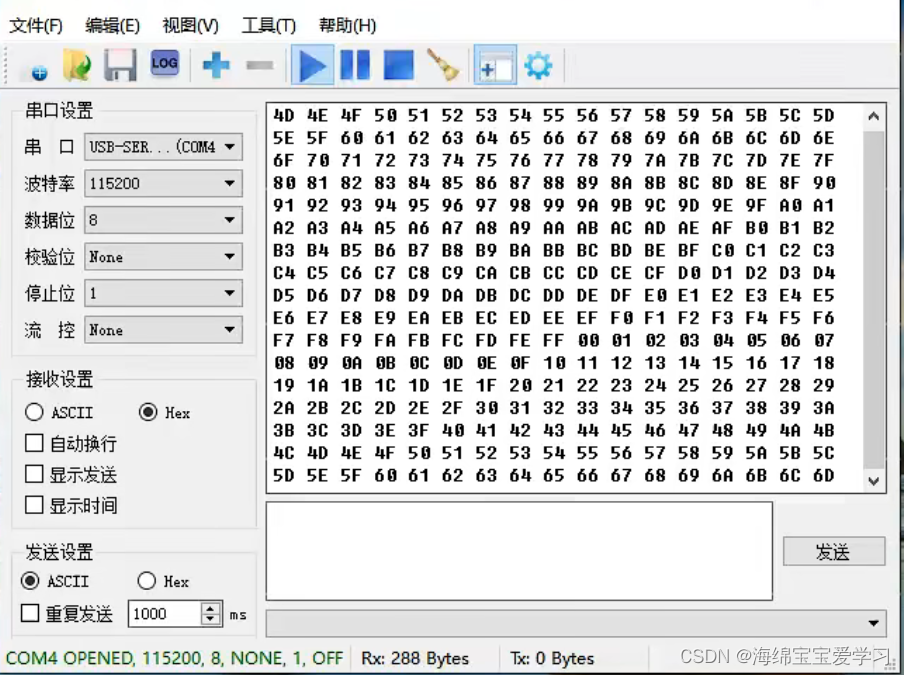

最后 板级验证!

相关文章

- USB设备驱动程序开发框架[通俗易懂]

- NFT链游经济模型系统开发搭建(应用详情)

- 这些免费API帮你快速开发,工作效率杠杠滴

- 又是一个开发效率神器

- Nginx 1.1.13 开发版本发布

- [TMLR | 论文简读] GemNet-OC:开发用于大型和多样化的分子模拟数据集的图神经网络

- Android常见问题及开发经验总结(二)

- 网站在线客服系统实时语音视频聊天实战开发,判断MediaStream对象是视频流还是音频流

- JProfiler 13 for Mac(Java开发分析工具)

- JProfiler 13 for Mac(Java开发分析工具)

- 【Android 系统开发】使用 Source InSight 阅读 Android 源码

- JProfiler 13 for Mac(Java开发分析优化工具)

- 使用jqMobi开发app基础:Side Menu详解手机开发

- android开发中使用到的一些设计者模式详解手机开发

- MySQL 开发技能培训:创建强大应用(mysql开发培训)

- Linux上的PHP扩展开发(php扩展linux)

- PHP Linux调试:提高开发效率的必备技能(phplinux调试)

- 谷歌开发独立式 VR 头显,支持眼球追踪技术

- 基于Android开发支持表情的实现详解