verilog中的3种for循环的写法

循环 for 写法 Verilog

2023-09-27 14:27:11 时间

直接进入正题,对于for循环的三种循环做以下介绍:

for循环用于例化多个模块

注意点:

(1)例化模块在for循环内部

(2)for循环需加名字

(3)genvar 定义在generate外面,可以全局使用(不推荐使用,最好一个generate for,对应一个循环变量)

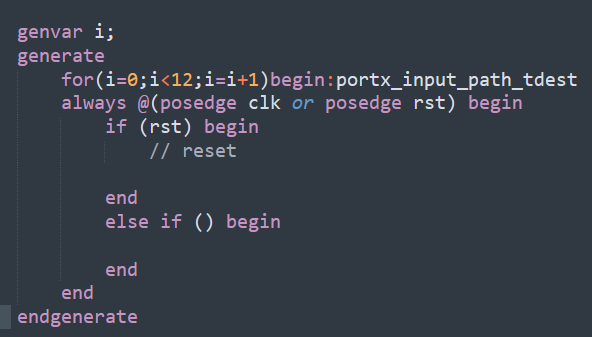

for循环写多个always块或者写多个assign语句4

注意点:

(1)always块在for循环内部

(2)for循环需加名字

(3)genvar 定义在generate外面,可以全局使用(不推荐使用,最好一个generate for,对应一个循环变量)

其实这个for循环类似第一个。

for循环在一个always块中对写多条类似语句

注意点:

(1)循环变量类型为integer

(2)always块需要加名字,for不用加名字。

小贴士:

generate for中支持data[3i+8:3i],但是单纯for循环,即第三种不支持这种写法,可改为data[3i+:8]。

相关文章

- Python循环语句代码详解:while、for、break

- bash shell for循环

- 反思JavaScript:论for循环的死亡

- python-day7 for语句循环遍历各种数据类型的场景

- 01 v-for循环绑定类名 v-bind 结合三目运算 动态添加类

- python FOR循环

- 【深入浅出.Net IL】1.一个For循环引发的IL

- dataframe添加元素指定为列表,不同for循环命名空间下的变量重复问题

- Fortran使用隐形DO循环和reshape给一维和多维数组赋初值

- 【GoLang】GoLang for 中有多个循环变量怎么处理?

- js的15种循环遍历,你掌握了几种【转】

- 【Python】循环结构:for-in循环(亦即for循环)

- 【极简python】第六章 for循环与while循环

- java-基础-foreach与正常for循环效率对比

- Lua 循环

- 循环链表的实现与操作(C语言实现)

- shell中for循环

- C++007-C++循环结构

- js语句(循环、switch)

- C++11的for循环,以及范围Range类的实现

- 【ybt高效进阶 21164 / 150B】【nowcoder 1103A】循环数组 / 复读数组(思维?)

- 李洪强漫谈iOS开发[C语言-052]-for循环

- 2019-8-31-C#-循环的判断会进来几次

- Shell脚本之七 选择、循环结构

- 【linux】shell中使用for循环