《逻辑与计算机设计基础(原书第5版)》——2.7 门的传播延迟

2.7 门的传播延迟

正如第2.1节所指出的那样,逻辑门的一个重要特性是传播延迟(propagation delay)。传播延迟是信号的变化从输入传播到输出所需要的时间。电路运行的速度与电路中经过门的最长传播延迟成反比关系。电路运行速度通常是电路设计的关键约束,在很多情况下,运行速度可能是最重要的设计约束。

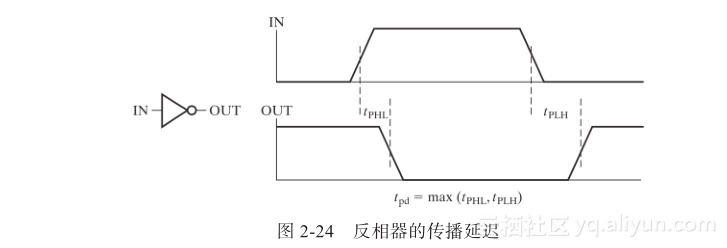

图2-24举例说明了传播延迟,它定义了三个传播延迟参数。高到低的传播时间(high- to-low propagation time)tPHL是指输出从高(H)变为低(L)时,从输入IN的参考电压到输出OUT的参考电压两者间的时间差。在此使用的参考电压是指电压信号最大值与最小值之间的中间值,即50%处。可以用其他的参考电压,这依赖于使用的逻辑系列。低到高的传播时间(low-to-high propagation time)tPLH是指输出电压从低(L)变为高(H)时,从输入IN的参考电压到输出OUT的参考电压间的时间差。传播延迟(propagation delay)tpd取这两个传播时间的最大值。选择最大值是因为我们最关心的是一个信号从输入传输到输出的最长时间。否则,tpd的定义可能不一致,这取决于如何使用数据。制造商通常在他们的产品中给出了tPLH和tPHL或者tpd的最大值与典型值。

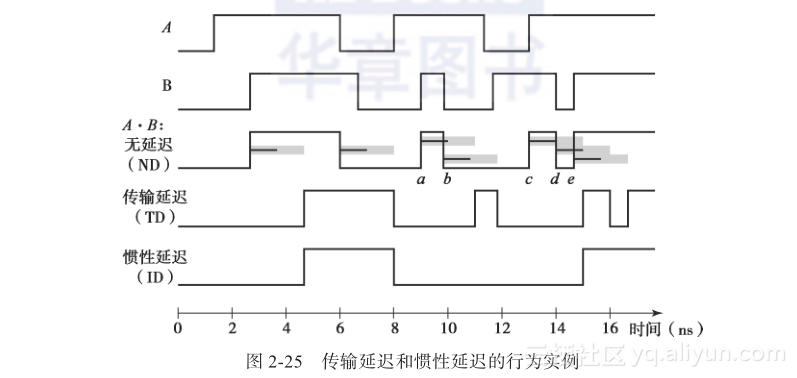

在模拟过程中对门建模时,往往使用传输延迟和惯性延迟。传输延迟(transport delay)是指输出响应输入的变化,在指定的传播延迟之后发生改变。惯性延迟(inertial delay)类似于传输延迟,但如果输入变化使输出在一个小于拒绝时间(rejection time)的间隔内发生两次变化,那么两次变化中的第一次将不会发生。这个拒绝时间是一个确定的值,它不大于传播延迟,通常等于传播延迟。图2-25是对与门采用传输延迟和惯性延迟进行模拟的情况。为了形象地理解延迟行为,图中还给出了不带延迟的与门输出情况。波形上的灰色条表示每次输入变化后的2 ns传播延迟时间,另一个较小的黑色条表示1 ns的拒绝时间。用传输延迟建模的输出与没有延迟的输出波形相同,只是右移了2 ns。而对于惯性延迟,波形同样右移。为了确定延迟输出的波形,波形中的每个变化称为一个边沿(edge)。为了确定特定的边沿是否会出现在惯性延迟的输出中,就必须判定该边沿的第二个边沿在无延迟输出中是否发生在拒绝时间结束之前,这个边沿是否会在惯性延迟输出中产生变化。例如,对于无延迟输出中的边沿a,边沿b发生在拒绝时间结束之前,故边沿a没有出现在惯性延迟输出中。同时由于边沿b不会改变惯性延迟的状态,所以该边沿也被忽略。在无延迟输出中,边沿c后的边沿d正好发生在拒绝时间,故边沿c出现。然而边沿d后的边沿e发生在拒绝时间中,故边沿d不会出现。因为边沿c出现,而边沿d不出现,故边沿e不能引起变化。

接下来,我们进一步考虑在实际电路环境中形成门延迟的各种组成成分。门本身存在固定的固有延迟,它表示为所驱动的电容。然而门的实际扇出也影响门的传播延迟,实际扇出可以根据标准负载计算得到,我们将在第5章进行讨论。门的总体延迟取决于连接到其输出的逻辑门输入负载,该值可能明显大于固有延迟。因此,传播延迟的简单表达式可以用公式或表给出,它们是固定延迟加上单个标准负载延迟乘以所驱动的标准负载数,如以下实例所示。

例2-15 基于扇出的门延迟估算

一个4输入与非门的输出连接下面这些门的输入,现用标准负载数表示它们的输入:4输入或非门—0.80标准负载,3输入与非门—1.00标准负载,反相器—1.00标准负载。

4输入与非门的延迟公式为

tpd=0.07+0.021×SL ns

这里的SL指门驱动的标准负载数。

忽略布线延迟,与非门的延迟估计为

tpd=0.07+0.021×(0.80+1.00+1.00)=0.129 ns

在现代高速电路中,由布线电容引入的门延迟部分通常也很可观。忽略这些延迟是不明智的,但是估算它们很困难,因为这取决于集成电路的布线。不过我们没有信息或者办法来很好地估算这方面的延迟,在此,我们忽略这部分延迟。 ■

基础逻辑门 Verilog HDL 设计语言支持3种设计风格: 门级,数据流级和行为级。 门级和数据流级设计风格通常用于设计组合逻辑电路,而行为级设计风格既可以用于设计组合逻辑电路又可以设计时序逻辑电路。本次实验通过使用Vivado 2015.1软件工具,以Basys3和Nexys4 DDR开发板为目标板,设计简单的组合逻辑电路来展示3种设计风格的用法。请参考Vivado手册了解如何使用Vivado工具创建工程并验证数字电路。

带你读《PDN设计之电源完整性: 高速数字产品的鲁棒和高效设计》之二:PDN阻抗设计基本原理 基于本书关注的重点,作者阐述了瞬时电流和PDN电压噪声之间的关系。作者引入了瞬时电流的概念,并讨论了该电流对电压响应的影响,并提供几个特定情况下的瞬时电流波形来加以说明和验证。这些知识能够帮助读者理解PDN的阻抗曲线,以及与特定电流模型之间的相互作用,并可以获得其相应的电压响应。

中国科大实现两类不同量子资源间的相互循环转化 中国科学家提出量子相干性与量子关联之间的循环转化方法,并在光子系统中实验验证了该方案,相关研究成果在线发表在《物理评论快报》上。

量子计算机之所以能成为量子计算机,更在于其对于量子比特的特殊计算操作。那么这里就需要引入量子逻辑门(Quantum Logic Gates)的概念。每一个 Quantum Logic Gate 都对应了一个数学上面的一个酉矩阵(Unitary Matrix)。

《逻辑与计算机设计基础(原书第5版)》——2.1 二值逻辑和逻辑门 本节书摘来自华章计算机《逻辑与计算机设计基础(原书第5版)》一书中的第2章,第2.1节,作者:(美)M.莫里斯·马诺(M. Morris Mano)著, 更多章节内容可以访问云栖社区“华章计算机”公众号查看。

《数字逻辑设计与计算机组成》一2.7 其他逻辑门 本节书摘来自华章出版社《数字逻辑设计与计算机组成》一 书中的第2章,第2.7节,作者:[美]尼克罗斯·法拉菲,更多章节内容可以访问云栖社区“华章计算机”公众号查看。

相关文章

- Linux下逻辑卷LVM的管理和RAID磁盘阵列

- 自动化测试工程师的学习方法和逻辑

- SpringBoot2.0 基础案例(15):配置MongoDB数据库,实现增删改查逻辑

- 单元测试本质:面向逻辑块

- 动态菜单/RBAC标准完整权限管理系统的实现,通用角色权限控制系统五张表逻辑关联设计实现

- 10.逻辑语句

- 关于Linux内核中RTL网络模组的支持逻辑

- 数据库建模 : 概念模型 , 逻辑模型和物理模型

- 逻辑代数基础

- mysqldump 逻辑备份的正确姿势

- Python机器学习零基础理解逻辑回归分析

- 使用枚举实现状态机来优雅你的状态变更逻辑

- 算法的逻辑复杂性

- 算法是用逻辑语言描述的问题求解步骤

- MySQL基础之 逻辑运算符

- JMeter学习-013-JMeter 逻辑控制器之-如果(If)控制器

- 大数据的商业化:从数据、模型到业务逻辑

- 【Verilog基础】2选1MUX实现基础逻辑功能(包括:反相器/与门/或门/与非门/或非门/异或门/同或门)(常考面试题:最少MUX实现异或门/同或门)

- 【Verilog基础】逻辑综合(6)Synopsys TCL语言

- 【Verilog基础】逻辑综合(5)优化电路的常用方法

- C++ 基础入门 之 算数运算符+-x/%++/赋值运算符=/比较运算符><=/逻辑运算符!&&||

- 对线性回归、逻辑回归、各种回归的概念学习

- sklearn实现逻辑回归

- LVM 逻辑卷管理(实战篇)