硬件架构的艺术 学习笔记(1)

第一章 亚稳态的世界

1.1 亚稳态产生的原因:

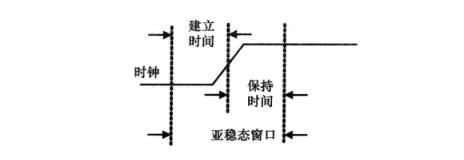

亚稳态是由于违背了触发器的建立时间和保持时间而产生的。设计中任何一个触发器都有特定的建立和保持时间,在时钟上升沿前后的这段时间窗口内,数据输入信号必须保持稳定。如果信号在这段时期发生了变化,那么输出将是未知的或者称为“亚稳态的”。这种有害状态的传播就叫做亚稳态。触发器的输出会因此产生毛刺,或者暂时保持在不稳定状态而且需要较长时间才能回到稳定状态。

1.2 亚稳态窗口

亚稳态窗口(Metastability Window)具有特定的时间长度,在这段时间的输入信号和时钟都应该保持不变。建立时间和保持时间共同决定亚稳态窗口的宽度。

1.3 MTBF 平均无故障时间

c2是器件相关的常数,器件的建立时间和保持时间越小,C2越小,MTBF就越大。所以可以通过选择更快的触发器,来减少亚稳态发生的概率。

MTBF越大,发生概率越小。

1.4 避免亚稳态

解决方法

1.4.1 使用多级同步器

如图所示,bclk的第一级FF输出发生亚稳态,亚稳态维持了一个周期,并在下一个时钟上升沿稳定,被识别为高,这样第二级的FF就能正确的将adat采样到了bq2_dat。

1.4.2 同步器的输入:源时钟寄存

采用同步器还有另外一个要求:通常,需要跨时钟的信号,需要在源时钟域先经过一级FF进行寄存输出。也就是说,跨时钟信号必须是寄存器的输出,中间不能有组合逻辑。还是刚才的电路,如果输入不是寄存器的输出,而是组合逻辑的输出那么情况会是怎样的呢?如下图所示:

可以看到,adat是组合逻辑的输出,变化的频率更快了,根据MTBF公式:

数据变化太快,会减小MTBF,增加亚稳态发生的概率。如果adat是FF的输出,那么根据FF的特性,输出在一个时钟周期内是不会改变的,数据的变化频率不会超过时钟频率,这样就能降低跨时钟信号变化的频率,减小亚稳态发生的概率,如下图所示:

所以,在使用同步器同步信号时,要求输入信号必须是源时钟域的寄存输出。

这里引用了该博客 芯片设计进阶之路-亚稳态和同步器

1.4.3 使用时钟倍频电路的多级同步器

1.5 亚稳态测试电路

总结

相关文章

- Nios II自学笔记一:Nios II软硬件架构介绍

- 学习笔记5:《大型网站技术架构 核心原理与案例分析》之 瞬时响应:网站的高性能架构

- 附022.Kubernetes_v1.18.3高可用部署架构一

- 分享一个Mvc的多层架构,欢迎大家拍砖斧正

- ****微信小程序架构解析

- OSI七层与TCP/IP五层网络架构详解

- 大型网站技术架构(一)--大型网站架构演化

- Docker:架构分解

- 优秀架构师必须掌握的架构思维

- 你不能错过的【Python爬虫】测试(完整源代码+架构+结果)

- HDFS架构原理与启动关闭操作

- 架构漫谈(八):从架构的角度看如何写好代码

- 课程报名丨揭秘 ClickHouse 在京东智联云的大规模应用和架构改良

- ODI学习笔记2--ODI产品架构

- 解读:架构云存储的TCS和LCA两大架构

- 优秀开源项目之三:高性能、高并发、高扩展性和可读性的网络服务器架构State Threads

- 可扩展Web架构与分布式系统

- 李洪强iOS开发之 - 项目架构