序列产生器

2023-09-27 14:20:42 时间

序列信号产生器

顾名思义,就是周期性的产生某段序列信号,这里介绍几种方法。

**第一种方法,**最容易想到的方法,设置一个长度和序列长度一样长的信号,在复位时,赋值为该段序列,接下来循环移位即可。

例 :设计一个序列信号发生器电路,能在CLK信号作用下周期性输出“1010110111”的序列信号。

module sequence_generator(

input clk ,

input rst_n ,

output out_sequence //可以根据题目要求加输出使能,读者自行扩展

);

reg [9:0] sequence ;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

sequence <= 10'b1010110111 ;//可以替换成其他序列

end

else begin

sequence <= {sequence[8:0],sequence[9]} ;//循环移位,先输出高位

end

end

assign out_sequence = sequence[9] ;

endmodule

在这种方法中,**优点是代码简洁,通熟易懂,但是也有个缺陷,就是需要花费的寄存器数量较多。

**

下面介绍第二种方法。

注意到这里序列为10’b1010110111 ,长度为10,也就是共10种状态,需要至少4个寄存器(2^4=16),

假如这里我们只使用四个寄存器,我们观察一下移位状态。

注意 移位方向为左移,移入的数据为多少是怎么判断的呢?

以这个为例,首先第一个状态的数据为从高位取寄存器数量的长度,假如这里使用五个触发器,则第一个状态为10101,则下一个数据移入为什么呢?答案是移入的为10101后面一个数据,依次移入后面五个数据,当后面五个数据移入完后在回到高位继续依次移入五个数据完成闭环。

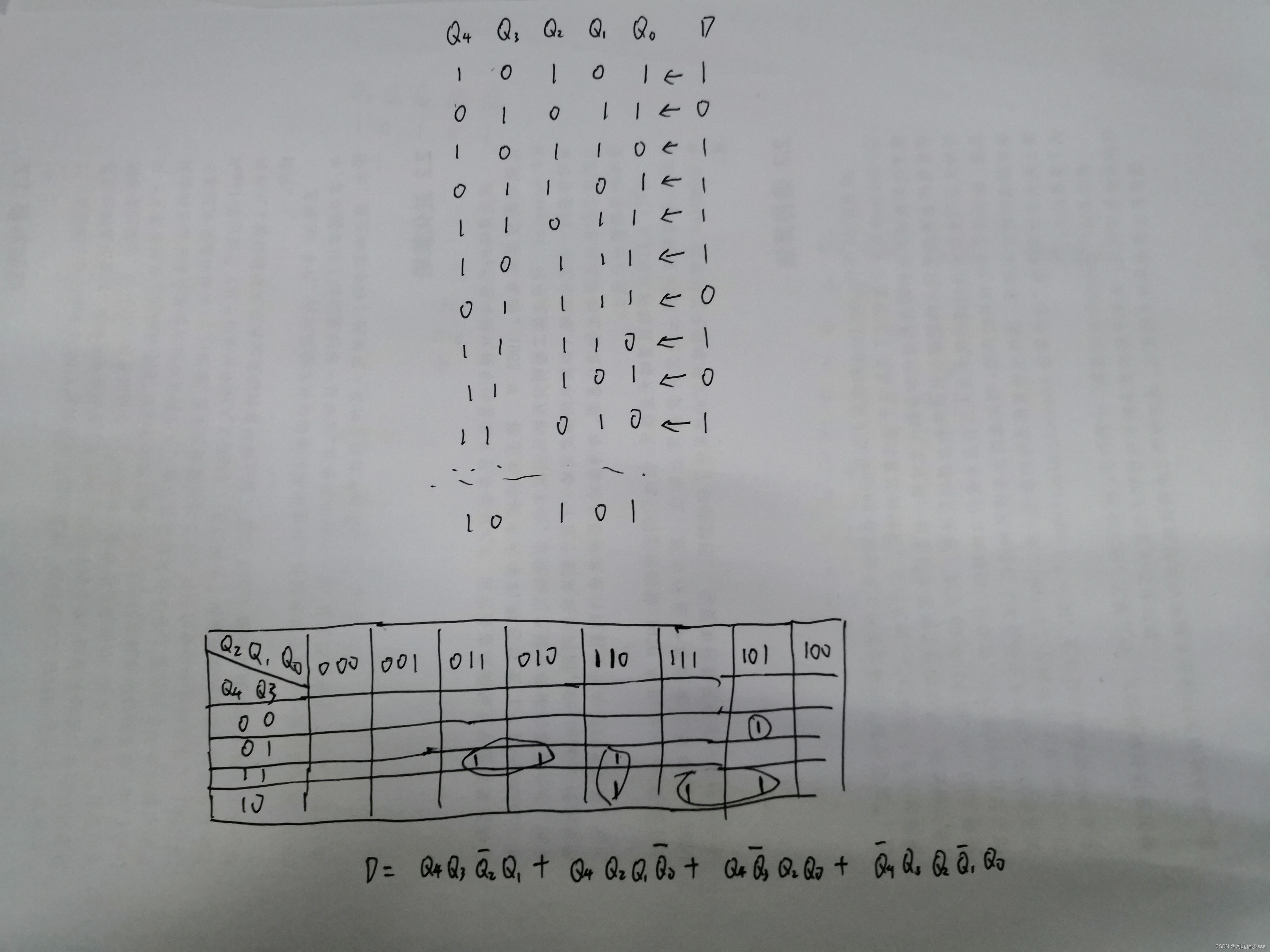

具体也可参考我画的状态转移表

1010–0101–1011–0110–1101–1011·····状态有重复,不可以,因为寄存器的输入和当前状态有关,不允许相同的状态出现两个不同的输出。

再看五个寄存器;

10101—01011–10110–01101–11011-10111–01111–11110—11101–11010 ··· 10101,没有重复,再回到了10101的循环。

因此我们列出状态转移表

卡诺图及其化简都已写出,具体的rtl代码大家就自己写啦。

下面还有两种方法,一种为状态机,另一种为计数器,给出一篇文章:序列信号发生器

相关文章

- NLP-分类模型-2018-多标签分类:SGM(SeqGenerateModel)【将多标签分类任务视为序列生成问题】【Seq2Seq+Attention+GlobalEmbeddi】

- AI-蛋白质-结构预测-2020:AlphaFold【输入:氨基酸序列】【输出:结构的性质(氨基酸之间两两的距离分布,氨基酸链的夹角分布)】【根据预测的性质构建约束,从而求解出拓扑结构】

- 56拓扑序列

- 基于MATALB编程的最小二乘SVM的时间序列预测,lssvm回归分析

- LeetCode·每日一题·940.不同的子序列 || · 动态规划

- LeetCode·每日一题·1403.非递增顺序的最小子序列·贪心

- NLP自然语言处理系列-算法基础-K 个一组翻转链表 验证二叉搜索树 从前序与中序遍历序列构造二叉树

- 递归算法:求序列的全排列

- 4275. Dijkstra序列

- 从fasta中提取或者过滤掉多个序列

- 819.递增序列

- 【ybt高效进阶4-1-2】【luogu P1631】序列合并

- [LeetCode] 300. Longest Increasing Subsequence 最长递增子序列

- leetcode 105 从前序与中序遍历序列构造二叉树