nios自学笔记二:一个简易的Qsys系统的开发流程

目录

2.2 使用Qsys软件创建带Nios II处理器的Qsys系统

2.3使用Nios II SBT Eclipse建立用户程序

提示:以下是本篇文章正文内容,下面案例可供参考

一、Qsys的开发流程

Qsys开发流程主要有以下三个步骤:

(1)利用Qsys集成开发工具搭建SOPC系统模块,包括Nios II处理器以及相应的外设;

(2)将搭建的Qsys例化到Quartus II工程中;

(3)利用Nios II SBT for Eclipse编写与Qsys系统相配套的software工程。

二、搭建qsys工程的详细流程

以一个实际项目中的小例子,介绍下nios II开发的流程,主要功能为项目中的一个RS485接口的外设,轮询其寄存器并将查询到的内容写到双口onship_memory中供RTL端读取。

软件版本:Quartus II 16.1

FPGA芯片型号:EP4CGX22CF19C8

2.1 新建quartus II工程

略

2.2 使用Qsys软件创建带Nios II处理器的Qsys系统

2.2.1 新建QSYS platform

Quartus II菜单栏选择[Tool]->[Qsys]选项来新建Qsys。并保存到合适的路径。

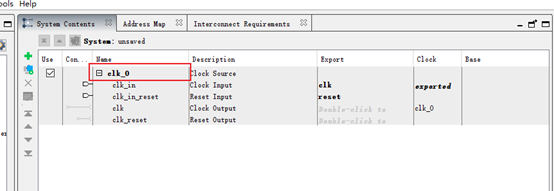

在System Contents页点击clk_0,在弹出的Parameters页设置时钟频率与时钟模块输出频率一致。

2.2.2 添加ROM和RAM

Nios处理器一样需要连接ROM和RAM,ROM用于存储程序文件,RAM用于程序运行。

一般情况下ROM可使用板上外接的ROM(比如Flash);RAM可使用FPGA的onchip-memory搭建RAM或者是外接SDRAM芯片。我这里使用FPGA烧写程序的EPCS_flash作为niosII用于存放程序文件;由于程序功能简单,故利用onchip-ram搭建程序运行的RAM。

添加EPCS控制器IP

EPCS控制器包含一个片上用于存储Bootloader程序的ROM存储器,IP核配置如下图,我们不需要任何设置,只需要将EPCS IP添加到Qsys软件中就可以使用。

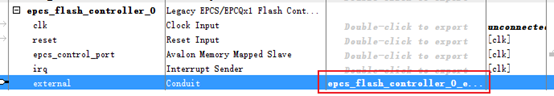

之后需要双击将EPCS IP的external引脚(flash控制)output到qsys外部,连接到FPGA对应的EPCS_flash器件对应的引脚

添加On-Chip Memory IP

在IP Catalog页双击On-Chip Memory (RAM or ROM) Intel FPGA IP, 在弹出的配置窗口作如下配置(type选择为RAM,memory size设置为20000 bytes(具体大小根据实际需求设置))

2.2.3 添加nios II CPU模块

在Platform Designer窗口的IP Catalog页(与Quartus的IP Catalog页内容不同)双击Nios II Processor。

在弹出的配置窗口的Main页中选择Nios II/f

在Vectors页中将Reset Vector Memory选择之前设置的EPCS,将Exception Vector Memory选择onchip ram

在Caches and Memory Interface页,选择设置Data Cache的Size为None

注:Data Cache相当于CPU内的数据高速缓冲,用于保证数据传输速度,而将部分数据打包进行传输。如果处理数据量较少并且需要突发处理,使用Data Cache可能导致数据在缓冲中保存而不会完成传输,在这种情况下可以设置Size为None,或者使用most-significant address位置1的方式将寄存器的最高位设置为1,使用该寄存器的数据传输不经过Data Cache。且Cache虽然可以改善系统整体性能,但是它会使得程序装载和存储指令或者数据的执行实际变得不可预测,所以这里未设置data Cache

其他如Tightly-coupled Memory以及MMU和MPU的添加和相关设置按需进行,我这里没用到。

2.2.4 添加System ID模块

用于自动校验的一个只读模块,用于确保软件程序与Nios的硬件配置相匹配。由Platform Designer的IP Catalog页查找并且添加System ID Peripheral IP,保持默认参数。

2.2.5 添加JTAG UART模块

JTAG UART模块可以通过JTAG实现PC与Nios的串口通信。由Platform Designer的IP Catalog页查找并且添加JTAG UART Intel FPGA IP,保持默认参数。

2.2.6 添加UART模块

由Platform Designer的IP Catalog页查找并且添加UART(RS-232 Serial Port) IP,设置相应的UART参数。

2.2.7 添加双口RAM模块

由Platform Designer的IP Catalog页查找并且添加on-chip Memory IP,设置type为RAM,勾选Dual-port access,设置Block type为M9K,选择对应的size信息。

我这块利用这个双口RAM,在nios中将轮询所得到的信息写在RAM中,然后另一端让RTL去读取。

2.2.8 添加PIO模块

由Platform Designer的IP Catalog页查找并且添加PIO(parallel I/O)IP,设置好对应的width和direction。我这里添加了几个output用于做flag的输出。

2.2.9 连接各模块信号

空心圆圈表示信号可连接但是未连接,鼠标点击空心圆圈后变成实心圆圈,表示建立连接。将各个模块的时钟连接到clk模块上,nios的总线连接到各个外设上,各reset可以手动连接也可以让软件一键连接,操作如下:

注:总线连接规则:数据主端口(data_master)连接存储器和外设元件,指令主端口(instruction)只连接存储器元件。

2.2.10 分配基地址和中断号

选择System菜单的Assign Base Addresses和Assign interrupt Numbers

2.2.11 生成 HDL

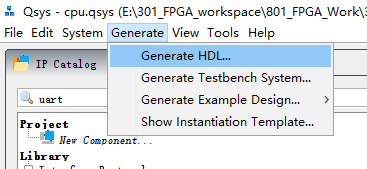

在Qsys的Generate菜单选择Generate HDL

2.2.12 例化qsys平台到quartus工程中

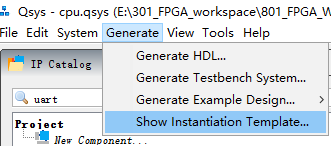

例化qsys跟模块例化相同,在Qsys的Generate菜单选择Show Instantiation Template

在弹出的界面中显示了对应语言的例化example例子,点击copy复制后在quartus工程中例化。

例化工程同时将模块外设对外引脚分配到对应的管脚上。这里要注意下,epcs_flash_controller对应的引脚(dclk,sce,sdo,data0)接到fpga对应的配置flash的引脚,需要设置一下对应的dual-purpose pins为use as regular I/O,操作方法如下:

设置:assignments>device>device and pin options>dual-purpose pins里面把epcs对应的四个引脚设置成use as regular i/o就可以了。

分配好pin和其他约束之后,编译工程文件,生成对应的sof文件,至此,nios硬件开发的工作就完成,后面进行软件开发。

2.3使用Nios II SBT Eclipse建立用户程序

2.3.1 新建software工程

Quartus菜单的[Tool]->[Nios II SBT for Eclipse],打开后设置Workspace的路径

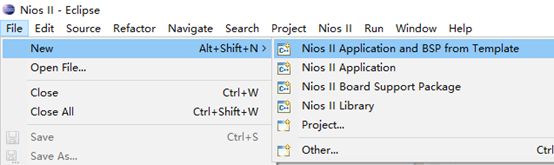

点击file->new->nios II Application and BSP from Template。新建nios software的Application和BSP包。

选择对应的SOPC info文件和工程名,点击finish生成software工程。

software工程中各文件的主要功能:

2.3.2 编写C代码实现功能

根据实际功能需求编写C代码进行功能开发,这里不细讲。

2.3.3 编译工程

右键工程,选择[Build Project]或者ctrl+B进行工程编译。

注:一般原始工程编译之后空间很大,之前设置的ROM和RAM空间不一定够用,可以设置下优化:在菜单栏中选择[Nios II]->[BSP Editor],出现如下界面

(1)enable_c_plus_plus:这个是针对C++语言支持的,如果没用到C++可以将勾选去掉。

(2)enable_clean_exit:该选项选中时,系统库在main()返回时调用exit(),调用exit()时,首先清I/O的缓冲区,然后调用_exit()。当该选项不选中时,系统库紧调用_exit(),能节省程序空间。对于嵌入式系统程序来说,一般都不从main()返回,所以该选项也可以不选中。

(3)enable_reduced_device_drivers:HAL为处理器的外设提供了两种驱动库:一种是执行速度快,但是代码量大的版本;另一种是小封装版本。默认情况下,HAL系统使用的是代码量大的版本,可以勾选该选项选择小代码版本的驱动库。

(4)enable_small_c_library:完整的ANSI C标准库通常不适用于嵌入式系统,HAL提供了一系列经过裁剪的新的ANSI C标准库,占用非常小的代码,我们可以通过选择这一项来选择小的标准库。

2.4 板级测试

首先需要将之前的硬件sof文件下载到板卡中,接着可以通过nios ii的eclipse软件进行debug和RUN,debug和run时选择Nios II Hardware。

2.5 将程序烧录到FPGA中

当代码debug OK之后,可以将nios的ELF文件和quartus的SOF文件一起烧写到EPCS中,能够上电自启,不会断电消失。

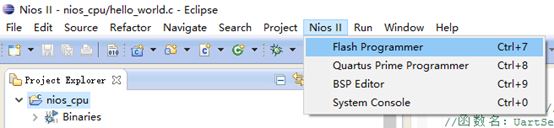

单击Nios II SBT for Eclipse软件菜单栏中的[Nios II]->[Flash Programmer]

弹出Nios II Flash Programmer框中的菜单栏中选择[File]->[new],之后在弹出的框种选择Get flash programmer system detail from BSP或者是SOPC。之后添加上对应的文件,点击OK

之后单机ADD,添加上ELF文件和SOF文件,然后单机start进行flash下载。

以此完成了整个nios搭建流程。

参考资料

1.《Hello FPGA》——软核演练篇

2.博客 https://blog.csdn.net/botao_li/article/details/84403894

相关文章

- 【Pytorch学习笔记】2.动手生成计算图——将Tensor间的计算流程和梯度传递可视化,使用torchviz生成计算图

- 流程项目点水笔记

- Android ANR分析(trace文件的产生流程)

- MTK平台的启动流程(secureboot)

- Vsphere笔记06 Vcenter 部署流程 1

- Rasa对话机器人连载三 第121课:Rasa对话机器人Debugging项目实战之电商零售对话机器人运行流程调试全程演示-3...

- 计算机视觉系列-轻松掌握 MMDetection 中 Head 流程-学习笔记 三

- BPM.NET设计器,流程控制的能力-SEO狼术

- Kafka Broker 工作流程

- shell入门之流程控制语句 分类: 学习笔记 linux ubuntu 2015-07-10 16:38 89人阅读 评论(0) 收藏

- GitFlow工作流常用操作流程

- Redis Cluster流程原理

- JBPM流程部署之流程定义实体对象分析

- 【Android 应用开发】UI绘制流程 ( 生命周期机制 | 布局加载机制 | UI 绘制流程 | 布局测量 | 布局摆放 | 组件绘制 | 瀑布流布局案例 )