嵌入式典型ARM处理器介绍以及分类

笔者电子信息专业硕士毕业,获得过多次电子设计大赛、大学生智能车、数学建模国奖,现就职于南京某半导体芯片公司,从事硬件研发,电路设计研究。对于学电子的小伙伴,深知入门的不易,特开次博客交流分享经验,共同互勉!全套资料领取扫描文末二维码!

温馨提示:学而不思则罔,思而不学则殆。实践是检验真理的唯一标准!

一、处理器和处理器核

(1)处理器核

“处理器核”特指实现某种版本ARM指令集架构、具有取指令和执行指令功能的组件。

(2)处理器

以处理器核为中心,再把存储管理部件MMU、中断控制器、浮点运算器、总线接口等组件进行集成就构成“ARM处理器”。

ARM处理器中一定包含有一个或几个处理器核,而单纯的处理器核也可以作为处理器使用。因此,一些资料中“处理器核”和“处理器”经常会混淆使用。

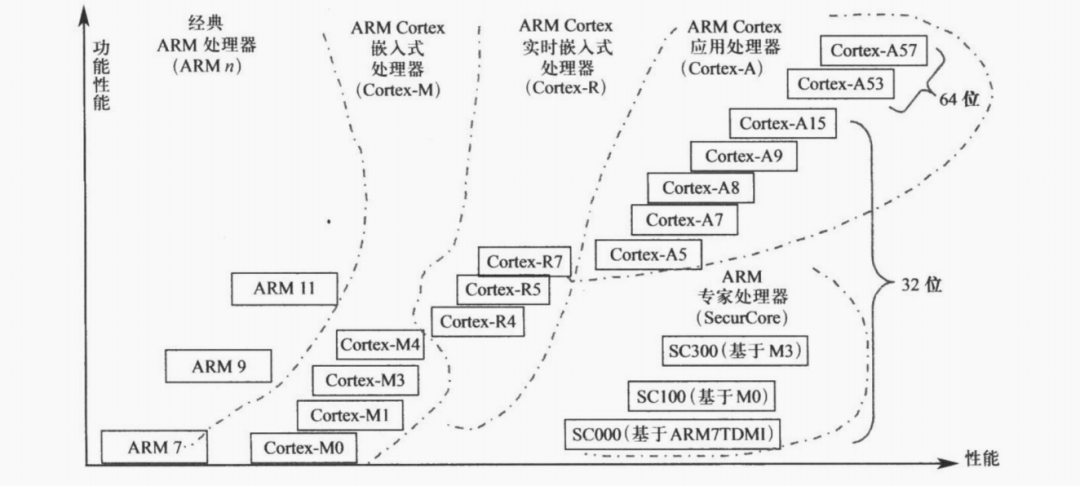

二、ARM处理器的分类

ARM处理器分为五类:经典ARM处理器、ARM Cortex嵌入式处理器、ARM Cortex实时嵌入式处理器、ARM Cortex应用处理器以及ARM专家处理器

ARM Cortex处理器包括:

(1) Cortex-A (A=Application) 系列是面向高端应用的处理器,它的工作频率高、性能好、功耗合理。A5~A15为32位,而A53-A57为64位版本。这类被称为ARMCortex应用处理器,简称应用处理器。

(2) Cortex-R ( R=Real Time)系列是面向实时控制应用的处理器,响应速度快、性能合理、功耗低。这类被称为ARMCortex实时嵌入式处理器,简称实时嵌入式处理器。

(3) Cortex-M ( M=Microcontroller)系列是面向微控制器的处理器,性价比极高、成本很低、功耗极小。这类被称为ARM Cortex嵌入式处理器,简称嵌入式处理器。

笼统地把-R系列和-M系列称为嵌入式Cortex处理器,简称嵌入式处理器。把专用于智能卡应用、侧重安全可靠的处理器称为安全专家处理器或专家处理器SecurCore,它有三个系列,分别是基于ARM7TDMI的SC000系列、基于Cortex-M0的SC100系列以及基于Cortex-M3的SC300系列。

三、经典ARM处理器

经典ARM处理器目前主要有ARM7、ARM9和ARM11三个系列,包含多种不同的处理器,它们大多是按照ARMv4T、ARMv5TE或ARMv6架构设计的。

(1) ARM7系列

ARM7系列的ARM7TDMI ( ARM7TDMS-S)是市场上销量最高的32位处理器内核,它采用ARMv4T架构,支持ARM/Thumb指令集,使用冯氏存储结构,由3级指令流水线实现,曾用于诺基亚6110手机。其命名中数字表示系列编号,T表示支持Thumb指令集,D表示支持片上调试,M表示具有快速的64位乘法,I表示提供片内在线仿真(ICE),-S 表示该处理器( 或处理器核)以IP软核的形式提供授权,让客户根据自己的半导体工艺进行再开发。(现在T、D、M、I这4项基本功能成了任何新产品的标配,因而不再使用这些后缀。)

(2) ARM9系列

ARM9系列处理器,它为微控制器、DSP和Java应用提供了单处理器解决方案,非常适合需要有数字信号处理功能的微控制器应用领域。

ARM920T处理器使用的核是ARM9TDMI,它基于ARMv4T架构设计,支持ARM/Thumb指令集,具有快速乘法器;采用程序与数据分离的哈佛存储结构,指令Cache和数据Cache各16 KB,还可通过总线外接Cache和SRAM存储器;支持协处理器;含有内嵌的在线仿真模块ICE、支持片,上调试;采用5级流水线以提高处理器性能,每一条指令的执行分为5个步骤:①取指令,②指令译码,③执行指令运算,④Cache/存储器访问,⑤结果写回寄存器。

图2-5是ARM920T处理器的框图。从图中可以看出,除了ARM9 TDMI处理器核之外,它还包括存储器管理部件MMU (实现虚拟存储器)、16 KB的指令Cache和16 KB的数据Cache、 数据写回RAM、AMBA总线接口、外部协处理器接口以及跟踪调试接口等。

图2-5 ARM920T内部结构框图

四、ARM Cortex嵌入式处理器

(1) Cortex-M的介绍

Cortex-M系列目前包括Cortex-M0/M0+/M1/M3/M4共5款处理器。它们保持向上兼容,具有高能效、易使用的特点,能以低成本提供丰富的功能,适用于对成本和功耗敏感的微控制器(MCU)和终端应用。

Cortex-M处理器都是32位的RISC处理器,采用流水线技术,它只支持Thumb-2指令集的子集。CM0和CM0+成本低、简单易用,适合成本控制要求高的中低端应用; CM3性能高,通用性好,适合工业控制及中高端应用;CM4具有有效的数字信号控制功能,适合数字信号处理要求高的应用。

(2) Cortex-M0 (CM0)

①Cortex-M0 (CM0)的特点

ARM Cortex-M0处理器是现有的体积最小、能耗最低的ARM处理器。它使用的门电路数量很少,用户能以8位处理器的价格获得32位处理器的性能,促进了智能、低功耗微控制器的面市,并为物联网中大量无线设备提供了高效连接、管理和维护的支持。

CM0的处理器核基于ARMv6M架构(是ARMv7M架构的子集),它仅有56条Thumb-2指令,用户很容易掌握,开发比较简单。它采用冯氏存储结构、3级流水线技术,可配置硬件乘法器,确定的指令执行时间和中断计时使得很容易计算出事件响应时间。

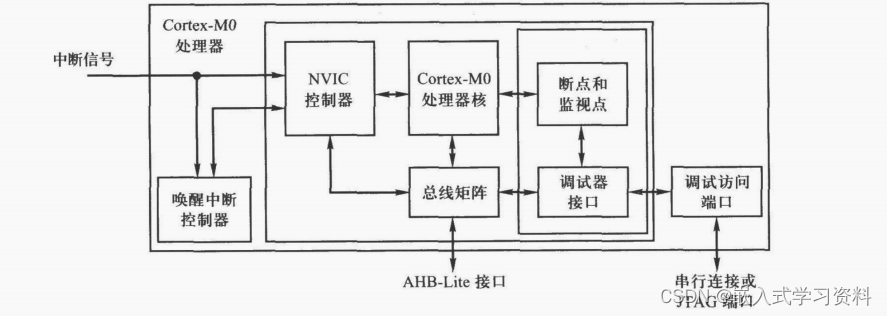

②Cortex-M0 (CM0)的结构

CM0处理器的结构如图2-6所示。其中,WIC( Wake-up Interrupt Controller )为唤醒中断控制器, NVIC( NestedVector Interrupt Controller)为嵌套向量中断控制器。32 位的AMBA-3AHB-Lite系统总线提供了与外部组件和存储器的简单接口。

图2-6 Cortex-M0 处理器的结构

(3) Cortex-M3 (CM3)

①CM3的结构

CM3处理器系列的低功耗、低成本和易于使用的优点相结合。Cortex-M3 处理器的结构如图2-7所示。它采用的处理器核是基于ARMy7-M架构,使用哈佛存储结构和3级流水线实现,支持Thumb-2指令集的子集,有硬件除法指令。

图2-7 Codex-M3 处理器的结构

a.总线矩阵和嵌套向量中断控制器

与处理器核集成在-起的是总线矩阵和嵌套向量中断控制器(NVIC), 前者提供了3条AHB-Lite总线,分别用于连接指令存储器、数据存储器和作为系统总线。

嵌套向量中断控制器(NVIC)最多能提供240个物理中断、1个不可屏蔽中断(NMI)和各种系统异常,每一个中断都分配一个中断优先级(共256个优先级),可动态调整。NVIC可支持嵌套中断,处理中断时,程序计数器、程序状态寄存器、链接寄存器和通用寄存器自动压入堆栈,中断处理完成后再由硬件自动恢复这些寄存器的内容,无须任何软件干预。

b.M3的外围组件

Cortex-M3处理器还有一些系统外围组件是可选的,如存储器保护单元(MemoryProtectionUnit,MPU)、唤醒中断控制器(WIC)、 AHB总线加速端口、Flash 修补及断点单元(Flash Patch Breakpoint, FPB)、 数据观察点及跟踪单元(Data Watch point and Trace, DWT)、 跟踪端口接口单元(Trace Port Interface Unit, TPIU)、 仪表化跟踪宏单元( Instrumentation Trace Macrocell, ITM)、 嵌入式跟踪宏单元( Embedded Trace Macrocell, ETM、 串行或JTAG调试接口等。

②M3的特点

Cortex-M3处理器集成度高、芯片空间使用合理、低成本、低功耗,是专业嵌入式应用很好的选择。

③CM4和CM3的区别

CM4比CM3多-一个VFP可选部件,具有数字信号处理能力。

五、ARM Cortex实时嵌入式处理器

(1) Cortex-R的介绍。

Cortex-R属于中档处理器,它提供的性能比Cortex-M系列高得多,而Cortex-A系列则性能更高,专用于需要运行复杂操作系统的面向用户的应用。

Cortex-R处理器系列有Cortex _R4、Cortex-R5 和Cortex-R7等品种,适用于计算复杂、实时性要求苛刻的领域。

(2) Cortex-R 的主要特点

①高性能

采用多级流水线结构,时钟频率较高,具有高性能DSP和硬件SIMD,可快速执行复杂代码和数字信号处理功能。

②实时处理

中断响应快,片内紧耦合存储器(Tightly Coupled Memory, TCM)能快速存取代码/数据,给实时系统的响应速度和高吞吐量的操作提供了保障。

③安全

内存保护单元(MPU)支持用户模式和授权软件模式,存储器和总线采用错误检测与纠正( Error Correcting Code,ECC) 技术,可双内核冗余配置,保证系统运行可靠。

④低成本

通过配置/排除某些功能使能效和芯片面积/成本效益最佳,调试断点和检测点可进行快速开发和测试,加快上市速度和可定制功能。

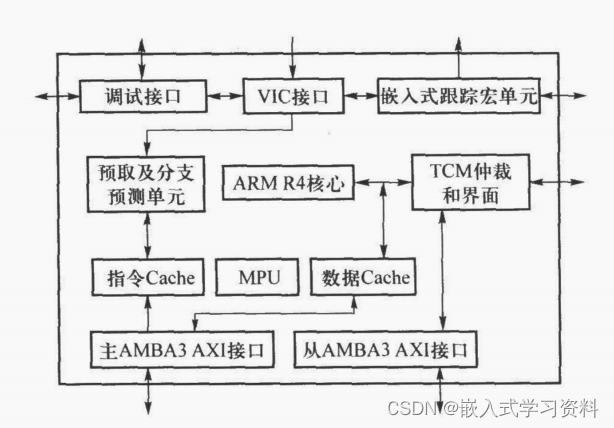

(3) Cortex-R 的结构

以Codex-R4为例,其结构如图2-8 所示。其核心是采用ARMv7-R 架构的处理器核ARMR4,它支持ARM/Thumb-2指令集,代码密度高;使用硬件实现单指令多数据(Single Instruction Multiple Data, SIMD) 的DSP指令;具有可选的浮点运算器(处理器型号为Cortex- R4F);使用8级流水线技术实现。

图2-8 Cortex-R4 处理器结构

Cortex-R4处理器以ARMR4核为中心,配置了指令Cache和数据Cache (4 KB~64 KB)、指令预取和分支预测部件、存储器保护单元(MPU)、片内紧耦合存储器(TCM)、向量中断控制器、跟踪调试电路以及高性能可扩展的AMBA3 AXI 64位总线接口。

六、ARM Cortex应用处理器

(1) Cortex-A的应用领域

Cortex-A处理器系列适用于有高计算要求、需运行功能丰富的操作系统以及要求提供交互媒体和图形显示的应用领域。

(2) Cortex-A处理器的架构

Cortex-A处理器除了A50 系列为64位字长,采用ARMV8A架构外,其他均为32位字长,包括

Cortex-A17/A 15/A 12/A9/A8/A7/A5处理器,它们使用基于ARMv7A架构的处理器核,支持传统的ARM、Thumb指令集和高性能紧凑型Thumb-2EE指令集,具有完全的应用兼容性;提供Java字节码加速执行的Jazelle技术;提供可信计算的Trust Zone安全扩展;采用最多可达13级的深度流水线技术,处理器时钟频率可达2 GHz左右。Codex-A处理器中都集成了浮点运算器VFP,提供了高性能的单精度和双精度浮点运算;集成了多媒体处理引擎NEON,提供了对于高级SIMD指令的支持;包含有分开的指令Cache和数据Cache(有些还包含二级Cache),实现了哈佛存储结构。有些处理器还支持ARMv7A架构的扩展,支持更大的物理地址访问、硬件虚拟化和128位的AMBA4 ACE总线。

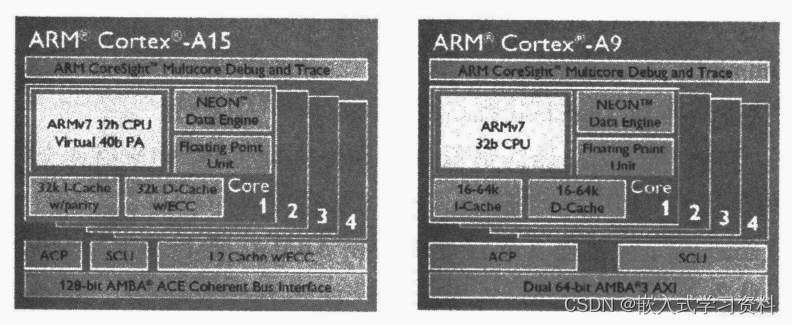

(3) Cortex-A 处理器的多核技术支持

除Cortex-A8处理器外,其他Cortex-A处理器都支持多核技术(称为ARM MPCore技术),最多可以集成4个处理器- -起运行,并保持集成的Cache - .致性。它还通过加速的一致性端口( Accelerator Coherency Port, ACP)将一致性扩展到SoC芯片中的其余组件,共享处理器的Cache存储器。侦测控制器(SnoopControlUnit,SCU)负责4个数据Cache的一致性,启动并仲裁对二级Cache的访问,对ACP进行管理,以很少的软件开销达到很高的整体性能。图2-9是Cortex-A15处理器和Cortex-A9处理器的组成框图。它们的处理器核采用超标量、可变长、乱序执行的指令流水线,使处理器的时钟频率能达到1~2 GHz。Cortex-A15的2 个一级Cache分别具有奇偶检测和错误检测与纠正(ECC)的功能,并配置有容量可达4MB的二级Cache,它采用128位的AMBA4ACE一致性总线接口,与其他组件的连接更加高效。Cortex-A9的一级Cache容量可以选择16、32 或64 KB,没有二级Cache,采用64位的AMBA3 AXI总线接口,性能比Conex-A15略低。

图2-9 Cortex-A15 和Cortex-A9处理器

(4) Cortex-A 处理器的运行平台

Cortex-A处理器可以运行的操作系统和软件平台有: Android、Adobe Flash、Java SE、Java FX、Linux、Microsoft Windows Embedded、Symbian 和Ubuntu等。

回复【更多资料】海量嵌入式资料赠送

笔者电子信息专业硕士毕业,获得过多次电子设计大赛、大学生智能车、数学建模国奖,现就职于南京某半导体芯片公司,从事硬件研发,电路设计研究。对于学电子的小伙伴,深知入门的不易,特开次博客交流分享经验,共同互勉!

相关文章

- FPGA的嵌入式乘法器

- 给嵌入式ARM+Linux的初学者

- 《安富莱嵌入式周报》第309期:开源脑机接口套件,三相多电平逆变器,开源电位仪,单片机并行计算,蓝牙市场分析报告,AI密码破解,nRF54H2发布,Z-Wave

- 《安富莱嵌入式周报》第281期:Keil Studio发布VSCode插件,微软嵌入式IDE升级,开源穿戴手表,CAN XL汽车单片机,USB4 V2.0规范,

- 《安富莱嵌入式周报》第259期:2022.03.28--2022.04.03

- 嵌入式新闻早班车-第28期

- 《安富莱嵌入式周报》第216期:2021.06.07--2021.06.13

- 嵌入式linux开发,Qt,.pro文件中进行宏定义,以区分不同平台引用的三方库

- 嵌入式linux开发,交叉编译qt4.8.5报错:make[2]: arm-linux-ar: Command not found

- 嵌入式Linux开发,Qt开发界面中,不能满屏显示,四周无法使用,不能从屏有右上角(0,0坐标)开始显示

- 嵌入式linux开发,C/C++交叉编译报错:-bash: /.../bin/arm-none-linux-gnueabi-gcc: No such file or directory

- 使用Visual Studio进行嵌入式系统开发

- 周立功arm linux教程,极速搭建周立功IMX287A ARM Linux开发环境

- 嵌入式linux开发,开机从TFTP服务器加载linux内核

- 嵌入式linux开发,bftpd移植

- 蓝桥杯嵌入式第六课--串口收发

- 学习嵌入式开发是需要忍耐