altera和xilinx的fifo对比

本文主要讲述altera和xilinx的fifo部分特性对比:

一、show_ahead

1、intel

在本来是一个空的fifo中,输出数据是多少拍才出现的呢?

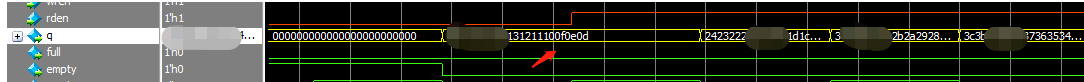

如图所示:在rden一直为低电平的情况下,当wren写入第一个数据之后,fifo在第三拍的时候把放在端口Q输出。并不是马上就放在端口Q上。

转载地址:https://blog.csdn.net/weixin_36590806/article/details/111059070

2、xilinx

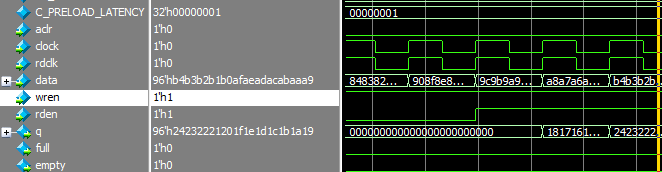

C_PRELOAD_LATENCY=0时,就相当于intel的show_ahead模式:

。

。

在本来是一个空的fifo中,输出数据是多少拍才出现的呢?

empty信号:在wren有效的第九个时钟,empty才高电平变成低电平。

此时就多讲一下C_PRELOAD_LATENCY等于其他值的时候,xilinx的FIFO特性吧

C_PRELOAD_LATENCY =1时,数据比rden晚1拍有效

C_PRELOAD_LATENCY =2时,数据比rden晚2拍有效。

二、当输入输出位宽不一致的情况下intel和xilinx的fifo特性

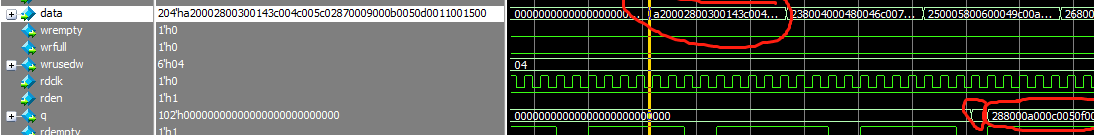

1、输入少位宽,输出多位宽 intel的fifo

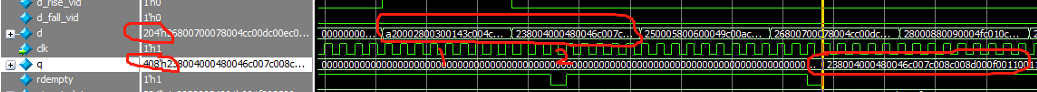

如图所示:输入时204位数据宽度的数据,输出是408位的数据宽度,在这种情况下,可以看到先输入的放在低位,后输入的放在高位,这样的排列方式,这个和xilinx是不一样的。

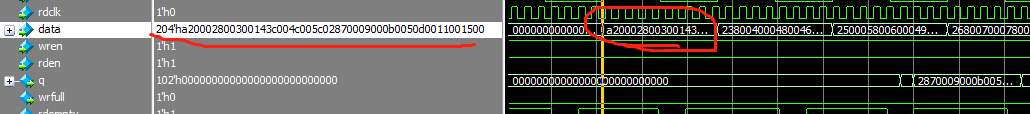

2、输入少位宽,输出多位宽 xilinx的fifo

如图所示:输入时204位数据宽度的数据,输出是408位的数据宽度,在这种情况下,可以看到先输入的放在高位,后输入的放在低位,这样的排列方式,这个和Intel是不一样的。

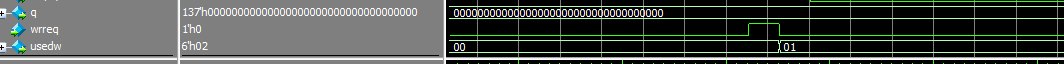

3、输入多位宽,输出少位宽 intel的fifo

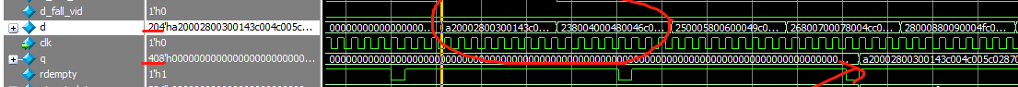

如图所示:在输入204位数据宽度的时候,输出102位宽,先输出输入数据的低102位,后输出输入数据的高102位。

4、输入多位宽,输出少位宽 xilinx的fifo

如图所示:在输入204位数据宽度的时候,输出102位宽,先输出输入数据的高102位,后输出输入数据的低102位。这个和Intel是不一样的。

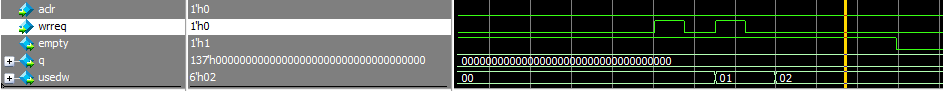

三、wr_data_count的参数在intel和xilinx的区别

1、intel的FIFO特性

在wr_en有效后,wr_data_count立马会更新。

2、xilinx的fifo特性

在wr_en有效后,等一个时钟,wr_data_count才会更新。这个和intel是不一样的。

相关文章

- Zookeeper 与 nginx 作负载均衡对比

- SpringBoot2 集成测试组件,七种测试手段对比

- 代码对比软件——Meld

- 与二值化阈值处理相关的OpenCV函数、方法汇总,便于对比和拿来使用

- H3C新华三/华为/思科交换机配置命令对比表

- 认识react, 并简单与vue对比

- InfluxDB和MySQL的读写对比测试

- 浅析setup sugar:使用与不使用 script setup 的繁杂性对比、具体如何使用 script setup、setup存在的限制(配置项缺失的处理)

- 浅析Collections.synchronizedList实现原理及如何做到线程安全、实现线程安全2种方式CopyOnWriteArrayList与Collections.synchronizedList的读写性能对比

- 浅析为什么推荐使用SLF4J、及SLF4J使用和与Log4J对比

- 试题 基础练习 字符串对比

- C# 之 静态方法和非静态方法对比

- 事件溯源与流处理的对比