数字电路设计: FPGA实现倍频

实现 设计 FPGA

2023-09-11 14:20:40 时间

Verilog实现倍频

这篇博客讲怎么用D触发器和异或门组成的倍频器,并用Verilog实现验证;

1. 原理:

- CLK时钟要想实现倍频,那么CLK每变化一次,对应的CLK_out就必须变化两次;因此采用D触发器,且CLK的上升沿,下降沿均有效,且均会引起CLK_out两次的变化;因此,需要在加入一个组合逻辑电路,CLK变化时,时序逻辑引起CLK_out从0->1,时序逻辑部分的输出作为输入,通过组合逻辑使CLK_out从1->0, 这样每次CLK变化时,CLK_out都会出现一个短时间的脉冲变化,从而达到倍频效果。

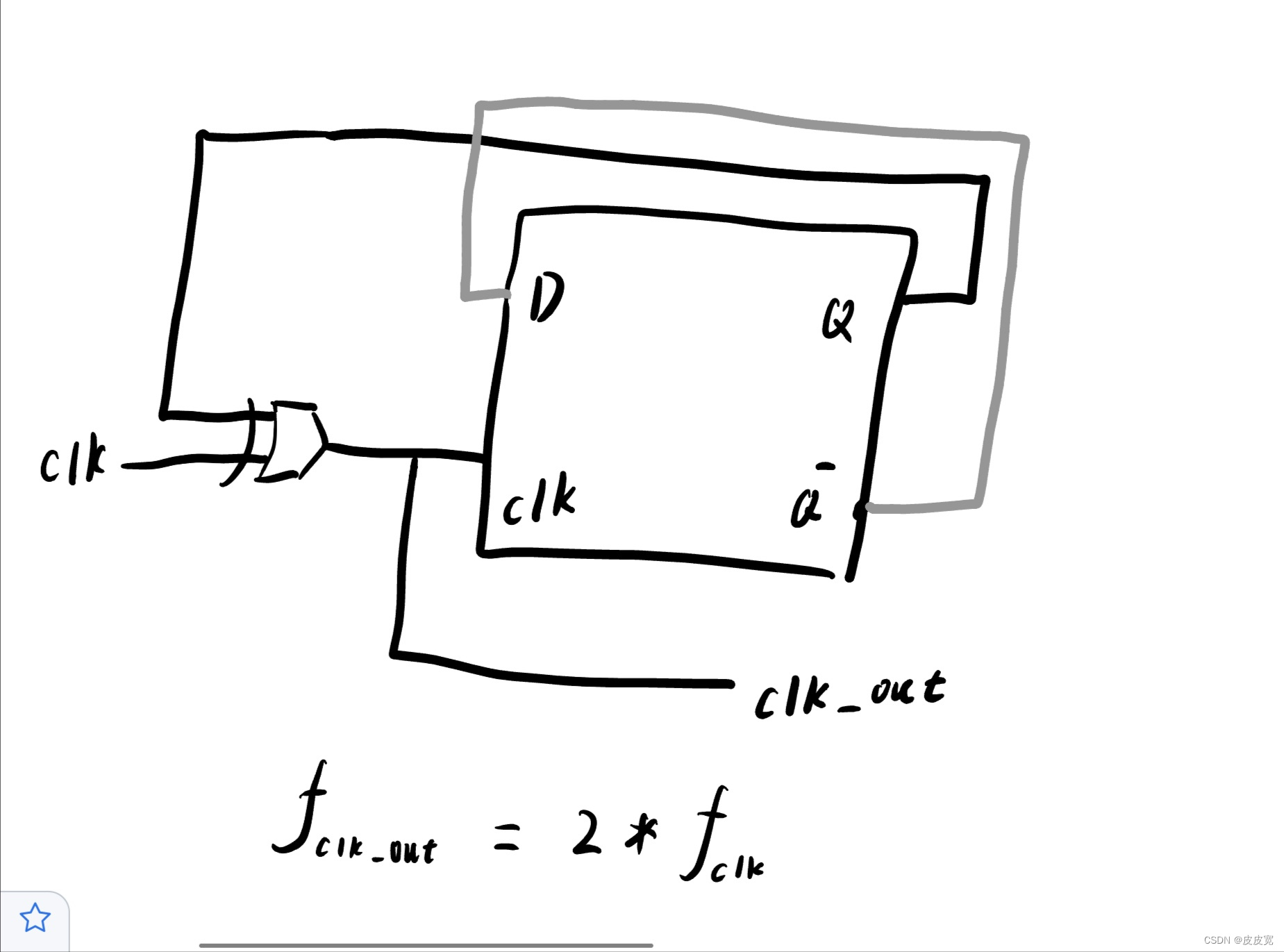

- 如图,手画了一下,我们将~Q与D相连,那么每次输入时钟信号时, Q都会翻转, Q和CLK通过一个异或门,输出到D触发器的时钟信号上,那么此时CLK的每次变化,都会使D触发器收到一个上升沿,而 Q翻转后又会将异或门的输出变回0,导致CLK每次变化都会在异或门的输出端产生一个脉冲信号,该脉冲信号是CLK的两倍。(也不知道这种电路设计出自哪儿,没找到出处)

2. 代码实现

module double_f(

input clk,

input rst,

output clk_out

);

reg Q;

wire NOR_clk;

always@(posedge NOR_clk or negedge rst)

begin

if(!rst)

Q <= 0;

else

Q <= ~Q; // #0.3 Q <= ~Q,通过加延时可以显示出来波形

end

assign NOR_clk = Q^clk;

assign clk_out = NOR_clk; //clk_out的频率是clk的两倍

endmodule

3.测试(testbench)

module test(

);

reg rst;

reg clk;

wire clk_out;

wire clk_;

wire rst_;

reg Q;

initial

begin

rst = 1;

clk = 0;

#5

rst = 0;

#20

rst = 1;

end

assign clk_ = clk;

assign rst_ = rst;

always #5 clk = ~clk;

double_f f(

.clk(clk_),

.rst(rst_),

.clk_out(clk_out)

);

always@(posedge clk_out or negedge rst) #由于clk_out的脉冲宽度特别小,所以我们用Q来捕获它的上升沿

begin

if(!rst)

Q <= 0;

else

Q <= ~Q;

end

endmodule

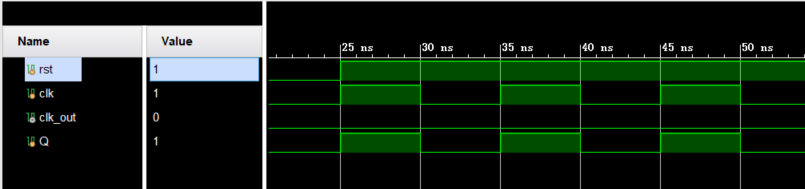

仿真波形如图所示:

由于clk_out的脉冲是延时导致的,而一般FPGA的延时很短,因此clk_out的脉冲长度很短,Xilinx仿真结果不显示这么短的脉冲,为了方便观看,clk_out每经历一次上升沿,Q就改变一次,因此Q的频率是clk_out的1/2, 因此由图可知clk_out的频率是clk的两倍.

相关文章

- java集合之ArrayList的实现原理

- 前端MVVM框架设计及实现(一)

- 链表面试题Java实现【重要】

- Java实现 蓝桥杯 算法训练 字符串长度(IO无敌)

- Java实现 LeetCode 706 设计哈希映射(数组+链表)

- Java实现 LeetCode 211 添加与搜索单词 - 数据结构设计

- Java实现 LeetCode 211 添加与搜索单词 - 数据结构设计

- Java实现 LeetCode 167 两数之和 II - 输入有序数组

- java实现排列序数

- Java实现 蓝桥杯VIP 算法训练 数的划分

- JAVA多线程实现简单的点名系统

- [转]hive实例讲解实现in和not in子句

- Atitit.导出excel报表的设计与实现java .net php 总

- ZZNUOJ_用C语言编写程序实现1166:逆转数(指针专题)(附完整源码)

- DL之NN:利用(本地数据集50000张数据集)调用自定义神经网络network.py实现手写数字图片识别94%准确率

- 基于LS-SVM对偶问题的分类、回归、时间序列预测和无监督学习研究(Matlab代码实现)

- 【多微电网】计及碳排放的基于交替方向乘子法(ADMM)的多微网电能交互分布式运行策略研究(Matlab代码实现)

- m基于FPGA和MATLAB的数字CIC滤波器设计和实现

- 【项目实战】Python实现Stacking分类模型(RF、ExtraTreesClassifier、AdaBoost、GradientBoosting、SVC)项目实战

- 自己主动升级系统的设计与实现(续2) -- 添加断点续传功能 (附最新源代码)

- 【LeetCode Python实现】二次元日麻游戏 雀魂麻将

- .atitit.web 推送实现解决方式集合(3)----dwr3 Reverse Ajax

- reactos操作系统实现(67)

- Vuejs设计与实现2-响应系统

- 基于Java+SpringBoot+Vue前后端分离学生管理系统设计与实现(有视频讲解)

- 【java】Spring Boot -- Spring的IOC实现原理

- kubelet 保护节点不被容器抢占所有资源 垃圾回收机制的设计与实现 image-gc-high-threshold