MPEG2编解码的FPGA实现

1.MPEG2编解码的原理说明

要成功实现MPEG2解码,我们首先要对该系统的基本原理进行研究,目前MPEG2解码的基本结构框图如下图所示:

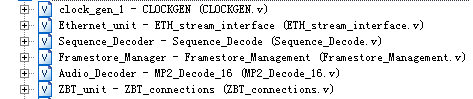

整个程序共分为5个主要部分:

这5个部分的主要功能就是

·MAC网口模块;

·序列压缩模块;

·帧存储管理模块;

·音频压缩模块;

·ZBT单元;

由于本系统是在Xilinx下实现的,里面使用了很多Xilinx内置的原语来设计的,所以我们在移植的时候需要对这些原语进行修改。

下面就针对这六个主要模块进行分析和移植以及最后的仿真验证。

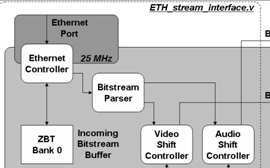

模块1:MAC网口模块

这个模块,主要是需要将其中的ram模块进行修改,该资源占用如下所示:

RTL模块如下所示:

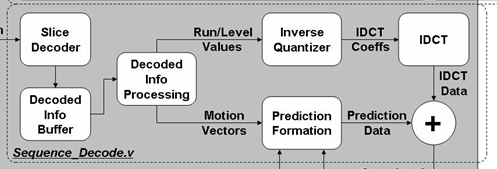

模块2:序列压缩模块

这个模块是整个系统的核心模块,主要涉及到的原语有:

FDCE语句,RAMB16_S18_S18双口RAM模块等。

对应的RTL图如下所示:

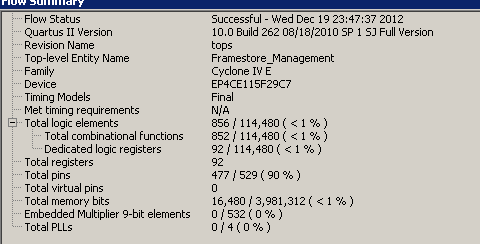

模块3:帧存储管理模块

在这个模块中,涉及到xilinx的原语中的几个RAM模块。

修改后的文件夹在如下的文件夹中:

修改之后,该模块资源如下所示:

其RTL结构图如下所示:

模块4:音频压缩模块

在这个模块中,涉及到xilinx的原语有:RAMB16_S18_S18双口RAM模块,DSP乘法器模块,以及CLKGEN内部的一些基础原语,对于这些,我们都需要重新进行设计。

修改后的文件夹在如下的文件夹中:

修改之后,该模块资源如下所示:

其RTL图如下所示:

模块5:ZBT单元

真个模块的主要功能就是存储器的设计。

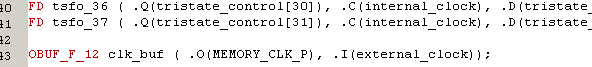

这个模块,其内部主要使用到了xilinx公司的原语:

这些语句,是Xilinx公司内部的支持语句,altera不支持,我们需要根据该模块的功能来重新编写程序,使其能够在altera下综合成果。

其中,xilinx中的FD原语,本质上就是一个D触发器,所以这里我们需要设计一个D触发器。

xilinx中的OBUF_F_12原语,其主要功能就是一个时钟缓冲模块,

xilinx中的IOBUF_F_12原语,其主要功能就是一个时钟的差分模块,这里我们将上面的三个模块进行重新编写。这样才能在QII中进行综合。

我们把这个模块单独的仿真文件夹下:

这个模块的对应的RTL图和资源分布图如下所示:

其RTL图如下所示:

即五个存储器。说明此模块已经成功移植了。

通过移植,整个系统的硬件资源占用为:

RTL图为:

相关文章

- Android多点触控技术,实现对图片的放大缩小平移,惯性滑动等功能

- 【帧率倍频】基于FPGA的视频帧率倍频系统verilog开发实现

- 【人脸定位】基于FPGA的肤色检测人脸定位的verilog实现

- 基于并行搜索的低信噪比环境下GPS信号检测算法FPGA实现

- 基于FPGA的智能PID控制器的设计与实现

- 基于FPGA的AES加解密读写控制系统,实现FLASH内部读写内容的销毁功能

- 【FPGA教程案例80】通信案例6——基于costas环的QPSK解调的FPGA实现

- 【FPGA教程案例40】通信案例10——基于FPGA的简易OFDM系统verilog实现

- 【FPGA教程案例10】基于Verilog的复数乘法器设计与实现

- 【FPGA教程案例8】基于verilog的分频器设计与实现

- 【AES】基于FPGA的128位AES加解密系统设计实现

- 【FPGA波速形成】基于FPGA的波速形成系统的设计实现

- SpringBoot实现电子文件签字+合同系统!

- 基于C语言实现外来人员进出监控与管理系统【100010644】

- Baxter实战:Ubuntu16.04+Kinect2实现动作跟随

- 实现财务自由 之 美股上市公司的年报(年度财报)(国内外公司年报20-F,10-k)查阅、下载、以及 翻译中文查阅、下载的方法

- STM32-USB学习系列(三):USB-MSC实现以SD卡为载体的U盘

- 【图像处理】——Python实现图像特征提取&BP神经网络实现图像二分类

- 利用图文和代码深度解析操作系统OS的内存管理实现原理机制和算法

- Android上实现各种风格的隐藏菜单,比如左右滑动菜单、上下滑动显示隐藏菜单