基于FPGA的串口通信RS232

数据传输方式指的是通过某种方式建立一个数据传输通道将数据信号在其中传输,它是数据通信的基础。数据的传输方式分为并行传输和串行传输,在串行传输中又分为异步传输和同步传输。按照电路的传输能力,可以分为单工、半双工、全双工传输。

2.2.1 并行传输与串行传输

并行传输指的是数据以成组的方式,在多条并行信道上同时进行传输。常用的是将构成一个字符的几位二进制码同时分别在几个并行的信道上传输。另外加一条控制信号即“选通”脉冲,它在数据信号发出之后传送,用以通知接收设备所有的位己经发送完毕,可以对各条信道上的信号进行采样了。收、发双方不存在字符同步的问题,不需要额外的措施来实现收发双方的字符同步,这是并行传输的主要优点。但是并行传输必须有多条并行信道,成本比较高,不适宜远距离传输,因此一般较少使用。

串行传输指的是组成字符的若干位二进制码排列成数据流以串行的方式在一条信道上传输。通常传输顺序为由低位到高位,传完这个字符再传下一个字符。因此收、发双方必须保持字符同步,以使接收方能够从接收的数据比特流中正确区分出与发送方相同的一个一个的字符。这是串行传输必须解决的问题。串行传输只需要一条传输信道,易于实现,是目前主要采用的一种传输方式。

2.2.2 异步传输与同步传输

在串行传输中,如何解决字符的同步问题,目前主要存在两种方式:即异步传输和同步传输。异步传输方式的优点是实现字符同步比较简单,收发双方的时钟信号不需要严格同步。缺点是对每个字符都需加入起始位和终止位,因而传输效率低。

同步传输是以固定的时钟节拍来发送数据信号的,因此在一个串行数据流中,各信号码元之间的相对位置是固定的(即同步)。接收方为了从接收到的数据流中正确地区分一个个信号码元,必须建立准确的时钟信号。与异步传输方式相比,由于它发送每一字符时不需要单独加起始位和终止位,故具有较高的传输效率,但实现起来比较复杂。

有关异步传输和同步传输的数据格式将在2.3中介绍。

2.2.3 单工、半双工、全双工传输

数据传输是有方向性的,根据数据电路的传输能力,可以有三种不同的传输方式或通信方式。

(1)单工传输:传输系统的两端数据只能沿单一方向发送和接收,这种方式传输系统的一端固定为发送端,另一端固定为接收端。反向信道的速率一般较低,为5-75bi/ts。实际应用中可以使用反向信道,也可以不用。气象数据的收集、计算机与监视器及硬盘与计算机的数据传输就是单工传输的例子。

(2)半双工传输:系统两端可以在两个方向上进行数据传输,但两个方向的传输不能同时进行,当其中一端发送时,另一端只能接收,反之亦然。无论哪一方开始传输,都使用信道的整个带宽。对讲机和民用无线电都是半双工传输。

(3)全双工传输:系统两端可以在两个方向上同时进行数据传输,即两端都可同时发送和接收数据。

综上所述,异步串行全双工的数据传输方式是较为容易实现的方式,应用较为广泛。

2.3串行通信协议

数据通信是在各种类型的用户终端和计算机之间以及同一型号的计算机之间进行的。它不同于电话通信方式,其通信控制也复杂得多,因此必须有一系列行之有效的、共同遵守的通信协议。所谓通信协议是指通信双方的一种约定,约定包括对数据格式、同步方式、传送速度、传送步骤、检纠错方式以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。因此,也叫做通信控制规程,或称传输控制规程,它属于国际标准化组织ISO(International Standards Organization)的开放系统互连OSI(Open System Interconnection)七层参考模型中的数据链路层口。

2.3.1串行通信接口标准

串行通信接口按电气标准及协议来划分包括Rs-232、Rs-422、Rs485、LVDS等。RS-232、RS-422与RS-485标准只对接口的电气特性做出规定,不涉及接插件、电缆或协议。LVDS是近几年发展起来的新型接口标准,主要应用于高速数据传输领域。

(l)RS-232串行接口

1969年,美国电子工业协会(EIA)公布了RS-232作为串行通信接口的电气标准,该标准定义了数据终端设备(DTE)和数据通信设备(DCE)间按位串行传输的接口信息,合理安排了接口的电气信号和机械要求。目前RS-232是PC机与通信工业中应用最广泛的一种串行接口。RS-232被定义为一种在低速率串行通信中增加通信距离的标准,它采取不平衡传输方式,即所谓单端通信。典型的RS-232信号在正负电平之间摆动,在发送数据时,发送端驱动器输出正电平在+5到+l5V,负电平在-5到-15v电平。当无数据传输时,线上为TTL电平,从开始传送数据到结束,线上电平从TTL电平到RS-232电平再返回TTL电平。接收器典型的工作电平在+3到+l2v与-3到-12v。Rs-232是为点对点(即只用一对收、发设备)通信而设计的,其驱动器负载为3到7k。。由于RS-232发送电平与接收电平的差仅为2V至3V左右,所以其共模抑制能力差,再加上双绞线上的分布电容,其传送距离最大为约30米,最高速率为20kb/s。所以RS-232适合本地设备之间的通信。

(2)RS-422串行接口

RS-422-B全名为“平衡电压数字接口电路的电气特性” (Electrical Characteristics of Balanced Voltage Digital Interface Circuits),它是美国电子工业协会EIA(Electronic Industry Association)制定的一种串行物理接口标准。RS是英文“推荐标准”的缩写,422为标识号,B表示修改次数。

RS-422由RS-232发展而来,它是一种单机发送、多机接收的单向、平衡传输规范。为改进RS-232通信距离短、速度低的缺点,RS-422定义了一种平衡通信接口,将传输速率提高到10Mbit/s,并允许在一条平衡总线上连接最多10个接收器。

RS-422采用平衡驱动,差分接收电路,即在发送端,驱动器将TTL电平信号转换成差分信号输出;在接收端,接收器将差分信号变成CMOS/TTL电平。从根本上取消了信号地接法,大大减少了地电平所带来的共模干扰。平衡驱动器相当于两个单端驱动器,其输入信号相同,两个输出信号互为反相信号。外部输入的干扰信号是以共模方式出现的,两根传输线上的共模干扰信号相同,因接收器是差分输入,共模信号可以相互抵消,从而大大提高了抗共模干扰的能力,并能在较长距离内明显提高传输速率。

RS-422的数据信号采用差分传输方式,也称作平衡传输。它使用一对双绞线,将其中一线定义为A,另一线定义为B。通常情况下,发送驱动器之间的差分电压正电平在+2V - +6V,是一个逻辑状态,负电平在-2V - 6V之间,是另一个逻辑状态。另有一个信号地C。在RS一485中还有一“使能”端,“使能”端是用于控制发送驱动器与传输线的切断与连接。当“使能”端起作用时,发送驱动器处于高阻状态,称作“第三态”,即它是有别于逻辑“1”与“0”的第三态。接口信号电平比RS-232-C降低了,就不易损坏接口电路的芯片,且该电平与TTL电平兼容,可方便与TTL电路连接。

接收器作与发送端相对的规定,收、发端通过平衡双绞线将AA与BB对应相连,当在接收端AB之间有大于+200mV的电平时,输出正逻辑电平,小于-200mV时,输出负逻辑电平。定义A端B端与地之间电压的平均值为共模电压,RS-422接收器可以承受[-7V,+7V]的共模电压。接收器符号见图2.1。

由于接收器采用高输入阻抗和发送驱动器比RS-232更强的驱动能力,故RS-422允许在相同传输线上连接多个接收节点,最多可接10个节点。即一个主设备(Master),其余为从设备(Slave),从设备之间不能通信,所以RS-422支持点对多的双向通信。RS-422四线接口由于采用单独的发送和接收通道,因此不必控制数据方向,各装置之间任何必须的信号交换均可以按软件方式(XON汉OFF握手)或硬件方式(一对单独的双绞线)实现。

RS-422的最大传输距离为4000英尺(约1200米),最大传输速率为10Mb/s。其平衡双绞线的长度与传输速率成反比在100kb/s速率以下刁一可能达到最大传输距离。

(3)RS-485串行接口

为扩展应用范围,EIA在RS-422的基础上制定了RS-485标准,增加了多点、双向通信能力,通常在要求通信距离为几十米至上千米时,广泛采用RS-485收发器。

RS-485许多电气规定与RS-422相仿。如都采用平衡传输方式、都需要在传输线上接终端电阻等。RS-485可以采用二线与四线方式,二线制可实现真正的多点双向通信。而采用四线连接时,与RS-422一样只能实现点对多的通信,即只能有一个主(Master)设备,其余为从设备,但它比RS一422有改进,无论四线还是二线连接方式总线上可连接多达32个设备,SIPEX公司新推出的SP485R最多可支持400个节点。

RS-485与RS-422的共模输出电压是不同的。RS-485共模输出电压在-7V至+l2V之间,RS-422在-7V至+7V之间,RS-485接收器最小输入阻抗为12k;RS-422是4k;RS-485满足所有RS-422的规范,所以RS-485的驱动器可以用在RS-422网络中应用。但RS-422的驱动器并不完全适用于RS-485网络。

为方便起见将上述几种主流通信接口的电气特性比较列表如表2.1:

表2.1 RS-232\RS-422\RS-485电气特性比较

| 规定 | RS-232 | RS-422 | RS-485 |

| 工作方式 | 单端 | 差分 | 差分 |

| 节点数 | 1收1发 | 10收1发 | 32收1发 |

| 最大传输速率 | 20Kb\s | 10Mb\s | 10Mb\s |

| 最大驱动电压 | +\-25V | -0.25V-+6V | -7V-+12V |

| 接收器输入电压范围 | +\-15V | -10V-+10V | -7V-+12V |

| 接收器输入门限 | +\-3V | +\-200mV | +\-200mV |

| 接收器输入电阻 | 3K-7K | 4K(最小) | 12K |

| 驱动器共模电压 |

| +\-3V | -1V-+3V |

| 接收器共模电压 |

| +\-7V | -7V-+12V |

RS-232串行接口属于个人计算机(PC)及电信应用领域中最为成功的串行数据标准;而RS-422和RS-485串行接口则是工业应用领域中最为成功的串行数据标准。由于可减少布线成本并实现较长的传输距离,RS-422和RS-485串行接口被广泛应用于汽车电子设备、销售点终端(POs)、工业控制、仪器仪表、局域网、蜂窝基站及电信领域,较高的输入电阻允许多个节点连至总线上。由于该类电路的优异性能,国外市场上目前己经出现了种类繁多的同类电路。几乎国际上几家大的集成电路开发公司都有相关产品,产品型号不胜枚举。但大多为双极工艺制造,采用CMOS工艺制作的产品还不多。

(4)LVDS

在被称为信息时代的今天,为适应信息化的高速发展,高速处理器、多媒体、虚拟现实以及网络技术对信号的带宽要求越来越大,多信道应用日益普及,所需传送的数据量越来越大,速度越来越快,l0Mbps的速率已然不能满足现代计算机之间高速互联的要求。因此采用新的技术解决I/O接口问题成为必然趋势,LVDS这种高速低功耗接口标准为解决这一瓶颈问题提供了可能。

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。LVDS的全称为Low Voltage Differential Signal,即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。目前,流行的LVDS技术规范有两个标准:一个是TI/EIA的ANSI/TIA/EIA-644标准,另一个是IEEEI596.3标准。这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确规定。LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是铜质的PCB连线,也可以是平衡电缆。标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

LVDS技术之所以能够解决目前物理层接口的瓶颈,正是由于其在速度、噪声、EMI、功耗、成本等方面的优点:

①高速传输能力:LVDS技术的恒流源模式低摆幅输出意味着LVDS能高速驱动,例如:对于点到点的连接,传输速率可达800MbPs;对于多点互连FR4背板,十块卡作为负载插入总线,传输速率可达400Mbps。

②低噪声:LVDS产生的电磁干扰低。这是因为低电压摆幅、低边沿速率、奇模式差分信号以及恒流驱动器的Iss尖峰只产生很低的辐射。在传输线上流过大小相等、极性相反的电流,电流在该线对内返回,使面积很小的电流回路产生最低的电磁干扰。当差分传输线紧藕合时,串入的信号是作为共模电压出现在接收器输入的共模噪声中,差分接收器只响应正负输入之差。因此当噪声同时出现在2个输入中时,差分信号的幅度并不受影响。共模噪声抑制也同样适用于其它噪声源,比如电源波动、衬底噪声和接地回跳等。

③低功耗:LVDS器件是用CMOS工艺实现的,这就提供了低的静态功耗。同时LVDS使用恒定电流源驱动器,随着工作频率的增加,其电源电流仍然保持平坦,而CMOS和TTL技术的电源电流则随频率增加而呈指数上升。因此,恒定电流驱动模式大大减少了LVDS的功耗。从对负载功率的计算(3.5mA电流乘以100欧终端电阻上的350mV压降)可看到LVDS仅有1.2mW的功耗。作为对比,TTL在负载电阻上有1V压降,负载电流为40mA,因而负载功耗为40mW。

④节省成本:LVDS器件采用经济的CMOS工艺制造,用低成本的电缆线和连接器件就可以达到很高的速率。由于功耗较低,电源,风扇等其他散热开销就大大降低。LVDS产生极低的噪声,噪声控制和EMI等问题迎刃而解。与并行连接相比,可以减少大量的电缆,连接器和面积费用。

⑤集成能力强:由于可在标准CMOS工艺中实现高速LVDS,因此用LVDS模拟电路集成复杂的数字功能是非常有利的。LVDS内集成的串行化器和解串行化器使它能在一个芯片上集成许多通道。较窄的链路大大减少了引脚数量和链路的总费用。差分信号能承受高电平的切换噪声,因而能用大规模数字电路进行可靠的集成。恒定电流的输出模式使LVDS只产生很低的噪声,因此能实现完整的芯片接口系统。

目前LVDS技术在传输距离上有其局限性,一般应用在20m以下。

LVDS的显著优势使得其应用范围远远超过那些传统器件,标准LVDS产品可广泛应用于计算机、通讯、消费电子、显示等领域。LVDS拥有低噪声的特色,最适用于笔记掌上型计算机的液晶显示器。平板显示器链接需要将大量的显示数据从笔记本计算机传送到平板显示器。美国国家半导体公司(NSC)和日本几家笔记本电脑生产商合作定义了FPD-Link标准用于平板显示器的链接,并生产出使用LVDS方式传输的样片。此外,NSC公司还建立基于LVDS的低摆幅差分信号标准RSDS,该标准将LVDS的性能特点应用到平板显示器的列驱动电路与TCON的芯片的连接上。它在功耗、噪声等方面有进一步改善,为LVDS在显示技术领域的应用提供了新的机遇。

高速串行通信也是LVDS最引人注目的应用之一。为实现并行数据并串及串并转换功能,德州仪器公司(TI)日前宣布推出一系列新型通用多芯片组器件,该系列器件充分发挥了TI在数据传输技术方面的设计经验和优势。就低电压差分信号(LVDS)链路数据传输而言,新系列产品是业界用途最为广泛的数据并串、串并转换器解决方案。采用该解决方案,设计人员不仅能将电线或电路板走线的数量减少一半以上,而且可将数据传输距离提高10倍。与其它串并转换器解决方案不同,MuxIt系列产品可高度适应各种总线宽度和速度,应用领域包括电信、打印/复印机、视频成像和消费类产业等。

目前,LVDS技术日益受到中国电路设计工程师的重视,LVDS应用前景广阔,在国内的发展非常迅猛。例如银河巨型机的高速互连传输中就采用了LVDS技术。但是国内使用的基本上都是国外厂商提供的成品,几乎没有自主设计的LVDS核心电路和芯片。令人欣慰的是,国内现在己经有几家公司正在研发LVDS核心电路和芯片。

2.3.2串行通信软件协议

目前,采用的通信协议有两类:异步协议和同步协议。同步协议又有面向字符和面向比特两大类。

2.3.2.1异步通信协议

异步通信协议中常用的是起止式异步协议,SCI软核中采用的就是这种协议。

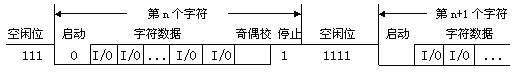

起止式异步协议的特点是一个字符一个字符传输,并且传送一个字符总是以起始位开始,以停止位结束,字符之间没有固定的时间间隔要求。其格式如图2-2所示。每一个字符的前面都有一位起始位(低电平,逻辑值0),后面是字符数据位,接着字符后面是一位校验位(也可以没有校验位),最后是一位、或一位半、或二位停止位,停止位后面是不定长度的空闲位。停止位和空闲位都规定为高电平(逻辑值),这样就保证起始位开始处一定有一个下降沿。

1

|

| 起 | ….. | 止 |

| 起 | …… | 止 |

0 |------一个字符-------| |------一个字符-------|

图2-2起止式异步传输

从图2-2中可以看出,这种格式是靠起始位和停止位来实现字符的界定或同步的,故称为起始式协议。传送时,数据的低位在前,高位在后。

起始位实际上是作为联络信号附加进来的,当它变为低电平时,告诉收方传送开始。它的到来,表示下面是数据位,要准备接收。而停止位标志一个字符的结束,它的出现,表示一个字符传送完毕。这样就为通信双方提供了何时开始收发,何时结束的标志。传送开始前,发收双方把所采用的起止式格式(包括字符的数据位长度,停止位位数,有无校验位以及是奇校验还是偶校验等)和数据传输速率作统一规定。传送开始后,接收设备不断地检测传输线,看是否有起始位到来。当收到一系列的“1”(停止位或空闲位)之后,检测到一个下降沿,说明起始位出现,起始位经确认后,就开始接收所规定的数据位和奇偶校验位以及停止位。经过处理将停止位去掉,把数据位拼装成一个并行字节,并且经校验后,无奇偶错才算正确的接收一个字符。一个字符接收完毕,接收设备有继续测试传输线,监视“0”电平的到来和下一个字符的开始,直到全部数据传送完毕。

由上述工作过程可看到,异步通信是按字符传输的,每传输一个字符,就用起始位来通知收方,以此来重新核对收发双方同步。若接收设备和发送设备两者的时钟频率略有偏差,这也不会因偏差的累积而导致错位,加之字符之间的空闲位也为这种偏差提供一种缓冲,所以异步串行通信的可靠性高。但由于要在每个字符的前后加上起始位和停止位这样一些附加位,使得传输效率变低了。因此,起止协议一般用在数据速率较慢的场合。在高速传送时,一般要采用同步协议。

2.3.2.2 同步通信协议

(1)面向字符的同步协议

面向字符的同步协议的典型代表是IBM公司的二进制同步通信协议。它的特点是一次传送由若干个字符组成的数据块,而不是只传送一个字符,并规定了10个字符作为这个数据块的开头与结束标志以及整个传输过程的控制信息,它们也叫做通信控制字。由于被传送的数据块是由字符组成,故被称作面向字符的协议。

如图2-3所示,数据块的前后都加了几个特定字符。SYN是同步字符(Synchronous Character),每一帧开始处都有SYN,加一个SYN的称单同步,加两个SYN的称双同步。设置同步字符是起联络作用,传送数据时,接收端不断检测,一旦出现同步字符,就知道是一帧开始了。接着的SOH是序始字符(Start Of Header),它表示标题的开始。标题中包括源地址、目的地址和路由指示等信息。STX是文始字符(Start Of Text),它标志着传送的正文(数据块)开始。数据块就是被传送的正文内容,由多个字符组成。数据块后面是组终字符ETB(End Of Transmission Block)或文终字符ETX(End Of Text),其中ETB用在正文很长、需要分成若干个分数据块、分别在不同帧中发送的场合,这时在每个分数据块后面用文终字符ETX。一帧的最后是校验码,它对从SOH开始到ETX或ETB字段进行校验,校验方式可以是奇偶校验或CRC校验。

| SYN字符 | SYN字符 | SOH. | 标题 | STX | 正文 | ETX或ETB | 校验码 |

图2-3 面向字符的同步协议的数据格式

(2)面向比特的同步协议

面向比特的协议中最具有代表性的是BIM的同步数据链路控制规程SDLC(Synchronous Data Link Control),国际标准化组织ISO(International Standard Organization)的高级数据链路控制规程HDLC(High Level Data Link Control),美国国家标准协会(American National Standard Constitute)的先进数据通信规程ADCCP(Advanced Data Communication Control Procedure)。这些协议的特点是所传输的一帧数据可以是任意位,而且它是靠约定的位组合模式,而不是靠特定字符来标志帧的开始和结束,故称“面向比特”的协议。这中协议的一般帧格式如图2-4所示:

|-----------------------一帧--------------------------|

| 0111 1110 | A | C | I | FC | 0111 1110 |

开始标志 地址场 控制场 数据场 16位CRC 结束标志

图2-4 SDLC/HDLC帧格式

由图2-4可见,SDLC/HDLC的一帧信息包括以下几个场(Filed),所有场都是从有效位开始传送。

(1)SDLC/HDLC标志字符:SDLC/HDLC协议规定,所有信息传输必须以一个标志字符开始,且以同一个字符结束。这个标志字符是01111110,称标志场(F)。从开始标志到结束标志之间构成一个完整的信息单位,称为一帧 (Frame)。所有的信息是以帧的形式传输的,而标志字符提供了每一帧的边界。接收端可以通过搜索“01111110”来探知帧的开头和结束,以此建立帧同步。

(2)地址场和控制场:在标志场之后,可以有一个地址场A(Address)和一个控制场C(Control)。地址场用来规定与之通信的次站的地址。控制场可规定若干个命令。SDLC规定A场和C场的宽度为8位或16位。接收方必须检查每个地址字节的第一位,如果为“0”,则后面跟着另一个地址字节;若为“1”,则该字节就是最后一个地址字节。同理,如果控制场第一个字节的第一位为为“0”,则还有第二个控制场字节,否则就只有一个字节。

(3)信息场:跟在控制场之后的是信息场(Information)。I场包含有要传送的数据,并不是每一帧都必须有信息场。即数据场可以为O,当它为O时,则这一帧主要是控制命令。

(4)帧校验信息:紧跟在信息场之后的是两字节的帧校验,帧校验场称为Fe(Frame Check)场或称为帧校验序列FCS(Frame Cheek Sequence)。SDLC/HDLC均采用16位循环冗余校验码CRC(Cyclic Redundancy Code)。除了标志场和自动插入的“0”以外,所有的信息都参加CRC计算。

4.1.1 波特率的计算

电子通信领域,波特率即调制速率,指的是信号被调制以后在单位时间内的波特数,即单位时间内载波参数变化的次数。它是对信号传输速率的一种度量,通常以“波特每秒”(Bps)为单位。 波特率有时候会同比特率混淆,实际上后者是对信息传输速率(传信率)的度量。波特率可以被理解为单位时间内传输码元符号的个数(传符号率),通过不同的调制方法可以在一个码元上负载多个比特信息。调制解调器的通讯速度。波特率是指线路状态更改的次数。只有每个信号符合所传输数据的一位时,才等于每秒位数。 为了在彼此之间通讯,调制解调器必须使用相同的波特率进行操作。如果将调制解调器的波特率设置为高于其他的调制解调器的波特率,则较快的调制解调器通常要改变其波特率以匹配速度较慢的调制解调器。

在FPGA中,我们要讲时钟频率转化为对应的波特率频率,其具体的代码如下:

parameter div_par=16'h104; //产生波特率为9600的分频值

//产生9600波特率的时钟信号

always@(posedge clk ) //40_0000_00/(9600*2)=2083.333333

begin

if(!rst) //----又由于有8个时隙

div_reg<=0;

else begin //----所以分频率系数为:

if(div_reg==div_par-1)

div_reg<=0; //----2083.333333/8=260.4~260

else

div_reg<=div_reg+1; //----转化为16进制为:104

end

end

//产生9600波特率的时钟信号

always@(posedge clk)

begin

if(!rst)

clkbaud8x<=0;

else if(div_reg==div_par-1)

clkbaud8x<=~clkbaud8x;

end

由计算公式,我们将时钟频率40MHZ除以波特率9600的两倍,可以得到一个分频系数2083.3333,又由于我们的串口通信的8位通信,应此要将获得的分频值再除以8,我们得到260,转化为16进制16'h104,这个就是我们得到的分频值。

4.1.3 PC向FPGA进行通信

在这里,我们将介绍由PC机向FPGA开发板发送数据的实现,其主要核心代码如下:

if(state_rec>=1&&state_rec<=8)

begin

if(clkbaud_rec)

begin

rxd_buf[7]<=rxd_reg2;

rxd_buf[6:0]<=rxd_buf[7:1];

state_rec<=state_rec+1;

end

end

这里我们采用的是利用状态机来实现串口通信,当发送数据位的时候,状态在1到8的时候,利用移位的方法,将数据一位一位的发送出去,将状态作为计数器一个一个的相加,这样,对应的发送一位数据,将其中的状态累加,即进入下一个状态,从而实现数据位的发送。

UART协议是实现设备之间低速数据通信的标准协议。因发送时不需同时发送时钟,故此协议为异步,UART链接典型为38400,9600波特。UART字符格式为1个起始位,5~8个数据位,1个地址位或奇偶位(可选),1个停止位。

由于接收器、发送器异步工作,无需联接接收和发送时钟。接收器采取对输入数据流高度采样方式,通常采样为16,并根据采样值确定位值。按惯例,使用16个采样值的中间三个值。

多站系统中,网络上可能会有两个以上的站,每个站有一特定的地址,由许多字符构成的帧可被广播,其第一字符做为目的地址。为实现此功能,UART帧被扩展一位,以区别地址字符和正常数据字符。

异步串口通信协议作为UART的一种,工作原理是将传输数据的每个字符一位接一位地传输。下图给出了其工作模式:

图4-3 串口波形帧格式

在启动一次发送或接收操作之后,串行UART(不论是软件还是硬件形式的UART)并不需要连续监控I/O线。在发送一个字符时,每个位周期,UART只需驱动一次发送信号线的状态,从起始位到8个数据位直到结束位依次设置每个位的电平。在接收一个字符时,UART在第一个下降沿开始工作,之后只需在每个位时隙的中央对接收线上的信号状态进行一次采样。 我们可以用一对状态机来表征软件UART的行为,一个状态机用于发送字符,另一个用于接收字符。对一个全双工的UART而言,这两个状态机是并行运行的,需要两个独立的定时器中断。这两个状态机都有主动和被动两种模式。发送状态机在收到一个需发送的字符时跳出空闲状态,在结束位发送之后回到空闲状态。接收状态机在检测到接收线上的一个下降沿时跳出空闲状态。在检测到这个初始的低电平状态之后(该状态指示起始位已经开始),开始对位时隙进行递减计数,同时按要求采样信号线上的每个信号位,包括停止位。为了避免不必要地占用主应用过多的时间,UART状态机应该由一些周期性的基于定时器的中断来激活。接收线上初始下降沿的检测需要利用一个边沿触发的外部中断单独处理。如果一个状态机的定时器被设置为每个比特周期发出一个中断请求,那么该状态机在每次中断被触发时能够执行任何需要的操作(而且如果需要,还能进入到下一个状态)。用于实现状态机的代码应尽可能优化,因为只要软件UART处于活动状态,这些代码就会在后台连续运行。

这样,我们实现了基本的由PC像串口发送的过程。我们在PC端利用串口调试工具,来向开发板发送数据,串口调试工具的设置如下:

图4-3 串口调试工具设置

利用COM1口,波特率为9600,数据位为8位,停止位为1为,不设置奇偶校验位。

4.1.4 FPGA向PC进行通信

有PC向FPGA发送数据,同时也要实现FPGA向pc发送数据,同样道理,我们也是利用状态机来实现串口通信。

12'b0000_0000_0001: //发送第一位

if(clkbaud_tras)

begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

end

当状态为一的时候发送第一位信号,并做一次移位操作,状态机状态加一从而进入下一个状态。如下面程序所示:

12'b0000_0000_0010: //发送第二位

if(clkbaud_tras)

begin

txd_reg<=txd_buf[0];

txd_buf[6:0]<=txd_buf[7:1];

state_tras<=state_tras+1;

end

这样就完成了第二位的发送,一次类推,就可以完成后面6位的数据发送。当发送完所有的8位数据后,再发送停止位,具体实现如下:

12'b0000_0000_1001: //发送停止位

if(clkbaud_tras) begin

txd_reg<=1;

txd_buf<=8'h55;

state_tras<=state_tras+1;

end

通过这个过程,我们完成了数据的串行发送,完成了数据发送。在PC串口调试工具中,我们可以得到接收到的数据。

图4-4 串口调试工具界面

相关文章

- Android跨进程通信:图文详解 Binder机制 原理

- 基于STBC空时分组码的OFDM通信系统误码率matlab仿真

- 【千兆以太网】基于FPGA的千兆以太网MIMO通信系统开发

- 【FPGA教程案例80】通信案例6——基于costas环的QPSK解调的FPGA实现

- 【FPGA教程案例76】通信案例2——基于FPGA的滑动窗口累加器实现

- 【FPGA教程案例75】通信案例1——基于m序列伪码匹配的直接序列扩频解扩通信系统FPGA实现

- 【FPGA教程案例33】通信案例3——基于FPGA的BPSK调制信号产生,通过matlab测试其星座图

- 基于FPGA的UWB通信/定位系统的开发介绍——简化版

- 基于 OFDM 调制解调传输的通信系统.

- 《云数据管理:挑战与机遇》2.1.5 基于广播和多播的组通信

- tkinter界面的TCP通信/开启线程等待接收数据

- Android基于UDP的局域网聊天通信

- 亿景WideLink系统与微软统一通信的整合

- flux沉思录:面向store和通信机制的前端框架

- Android 串口通信基于licheedev、rxjava、eventbus敏捷实现

- 基于RS422通信的FPGA软件设计第四天

- 基于RS422通信的FPGA软件设计第二天

- 软银将在东京进行5G通信技术外场测试 与中兴联合进行

- 网络与通信程序设计-基于UDP的广播通信实例