基于EDA技术的频率计系统设计

频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。通常情况下计算每秒内待测信号的脉冲个数,此时我们称闸门时间为1秒。闸门时间也可以大于或小于一秒。闸门时间越长,得到的频率值就越准确,但闸门时间越长则每测一次频率的间隔就越长。闸门时间越短,测的频率值刷新就越快,但测得的频率精度就受影响。通过两种不同的设计思路,设计两个不同的频率计,通过观察实验结果,得出频率计精度,作出对比。在此次设计中,均以1秒为闸门时间,在该时间内计算待测信号的脉冲个数,并显示频率值。

4.2 基于FPGA的数字频率计的设计与实现

4.2.1 顶层模块设计

目前,FPGA的设计方法主要有两种,自下而上的设计方法与自上而下的设计方法。另外。还可根据实际情况,利用这两种方法的组合进行综合设计,即综合设计方法。自下而上的设计方法是一种传统的电子系统设计方法,它们的设计流程分别如下所示:

|

系统分解 |

|

单元设计 |

|

功能块划分 |

|

子系统设计 |

|

系统合成 |

图4-1 自下而上的设计方式

|

行文设计 |

|

结构设计 |

|

逻辑设计 |

|

电路设计 |

|

版图设计 |

图4-2 自上而下的设计方式

所以,在本系统,我们也将对其进行自顶向下的设计方法,其顶层代码如下所示:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FREQ IS

PORT(FSIN:IN STD_LOGIC;

CLK:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END ENTITY FREQ;

ARCHITECTURE ART OF FREQ IS

COMPONENT CNT10 IS

PORT(CLK,CLR,ENA:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

CARRY_OUT:OUT STD_LOGIC);

END COMPONENT CNT10;

COMPONENT REG32B IS

PORT(LOAD:IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END COMPONENT REG32B;

COMPONENT TESTCTL IS

PORT(CLK:IN STD_LOGIC;

TSTEN:OUT STD_LOGIC;

CLR_CNT:OUT STD_LOGIC;

LOAD:OUT STD_LOGIC);

END COMPONENT TESTCTL;

SIGNAL SE,SC,SL:STD_LOGIC;

SIGNAL S1,S2,S3,S4,S5,S6,S7,S8:STD_LOGIC;

SIGNAL SD:STD_LOGIC_VECTOR(31 DOWNTO 0);

BEGIN

U0:TESTCTL PORT MAP(CLK=>CLK,TSTEN=>SE,CLR_CNT=>SC,LOAD=>SL);

U1:CNT10 PORT MAP(CLK=>FSIN,CLR=>SC,ENA=>SE,

CQ=>SD(3 DOWNTO 0),CARRY_OUT=>S1);

U2:CNT10 PORT MAP(CLK=>S1,CLR=>SC,ENA=>SE,

CQ=>SD(7 DOWNTO 4),CARRY_OUT=>S2);

U3:CNT10 PORT MAP(S2,SC,SE,SD(11 DOWNTO 8),S3);

U4:CNT10 PORT MAP(S3,SC,SE,SD(15 DOWNTO 12),S4);

U5:CNT10 PORT MAP(S4,SC,SE,SD(19 DOWNTO 16),S5);

U6:CNT10 PORT MAP(S5,SC,SE,SD(23 DOWNTO 20),S6);

U7:CNT10 PORT MAP(S6,SC,SE,SD(27 DOWNTO 24),S7);

U8:CNT10 PORT MAP(S7,SC,SE,SD(31 DOWNTO 28),S8);

U9:REG32B PORT MAP(LOAD=>SL,DIN=>SD(31 DOWNTO 0),DOUT=>DOUT);

END ARCHITECTURE ART;

4.2.2计数器模块

该十进制计数模块由八个一位十进制计数器组成,计数器的特殊之处是,有一个时钟使能输入端ENA,用于锁定计数值。当高电平是计数允许,低电平时计数禁止。

该测频的八位十进制频率计的计数模块,先通过VHDL语言编写一位十进制计数器,再将其原件例化后搭建一个八位十进制计数模块。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CNT10 IS

PORT(CLK:IN STD_LOGIC;

CLR:IN STD_LOGIC;

ENA:IN STD_LOGIC;

CQ:OUT INTEGER RANGE 0 TO 15;

CARRY_OUT:OUT STD_LOGIC);

END ENTITY CNT10;

ARCHITECTURE ART OF CNT10 IS

SIGNAL CQI:INTEGER RANGE 0 TO 15;

BEGIN

PROCESS(CLK,CLR,ENA)IS

BEGIN

IF CLR='1'THEN CQI<=0;

ELSIF CLK'EVENT AND CLK='1'THEN

IF ENA='1'THEN

IF CQI<9 THEN CQI<=CQI+1;

ELSE CQI<=0;END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CQI) IS

BEGIN

IF CQI=9 THEN CARRY_OUT<='1';

ELSE CARRY_OUT<='0';END IF;

END PROCESS;

CQ<=CQI;

END ARCHITECTURE ART;

4.2.3数字锁存模块

锁存模块由锁存器构成,主要功能是数据的稳定显示,不会由于周期行的清零信号而不断闪烁。在信号LOAD的上升沿后即被所存到寄存器的内部,并由锁存器的输出端输出,然后由实验板的7段译码器译成能在数码管上显示的相对应的数值。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG32B IS

PORT(LOAD:IN STD_LOGIC;

DIN:IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(31 DOWNTO 0));

END ENTITY REG32B;

ARCHITECTURE ART OF REG32B IS

BEGIN

PROCESS(LOAD,DIN) IS

BEGIN

IF LOAD'EVENT AND LOAD='1' THEN DOUT<=DIN;

END IF;

END PROCESS;

END ARCHITECTURE ART;

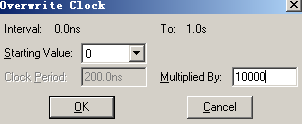

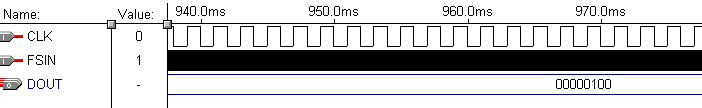

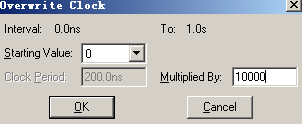

最后我们开始系统的仿真,由于在仿真过程中,1S钟时间将会仿真很长时间,所以我们考虑缩短仿真时间,我们首先假设系统时钟频率1hz对于设置参数为如下所示(左图),而输入的被测试信号的频率为(右图):

图4-5 参数设置一

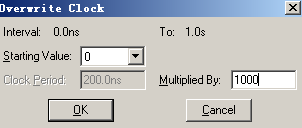

这里表示输入的时钟是系统时钟的10倍,即10hz,那么其仿真结果为:

图4-6 系统仿真结果

检测到信号的频率为10hz。

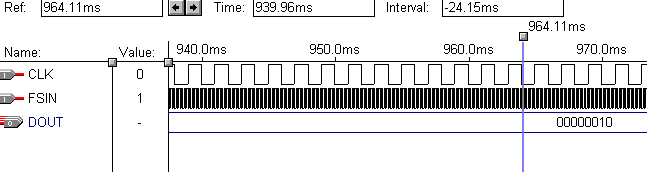

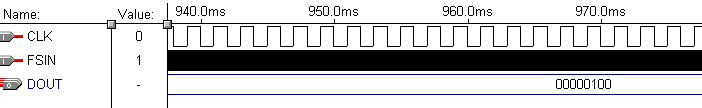

下面再做两次仿真:

图4-7 参数设置二

这里表示输入的时钟是系统时钟的100倍,即100hz,那么其仿真结果为:

图4-7 系统仿真结果

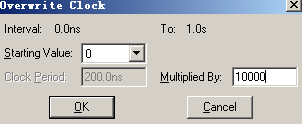

图4-8 参数设置三

这里表示输入的时钟是系统时钟的1000倍,即1khz,那么其仿真结果为:

图4-9 系统仿真结果

由于MAXPLUSII软件内部其最大设置为32000,因此在该系统中,我们无法仿真10Mhz的效果,但是其实际上由于显示的是8位,即10M。那么在实际的应用中,我们可以测量到10Mhz的信号。

相关文章

- 电脑维修常用硬件技术

- HTML5 manifest离线缓存技术

- 基于Hadoop的云盘系统客户端技术难点之二 HDFS文件访问控制

- 基于Hadoop的云盘系统客户端技术选型说明

- 让容器跑得更快:CPU Burst 技术实践

- Instagram的技术探索(转)

- 由金融服务中的智能机器人技术引发的种种思考

- 解读Gartner2023年重要战略技术趋势

- java权限系统的技术演变历史

- 阿里巴巴开源技术汇总:115个软件(三)

- java权限系统的技术演变历史

- Atitit 信息化数据采集与分析解析 技术 处理技术 爬虫与http rest json xml h5解析 db数据库 mail协议与处理 数据压缩与解压 数据处理 文本处理

- atitit 数字音频技术概论 艾提拉著 目录 1. 声学基础2 1.1. 1.2人耳的听觉效应92 2. 第1章数字音频基础2 2.1. 1.1音频的发展历史2 2.2. 1.2音频的发展

- Atiitt cdn技术总结 性能提升之道 目录 1. 组成 最简单的CDN网络由一个DNS服务器和几台缓存服务器组成:1 1.1. CDN是一个经策略性部署的整体系统,包括分布式存储、负载均衡

- 渣本双非进大厂,3轮技术面+1轮HR面,拿下字百万年薪offer

- DL之DNN优化技术:自定义MultiLayerNet【5*100+ReLU】对MNIST数据集训练进而比较三种权重初始值(Xavier参数初始化、He参数初始化)性能差异

- 从入门到精通:深入掌握 Java I/O、NIO 和其他流技术

- 基于模态凝聚算法的特征系统实现算法的自然激励技术(Matlab代码实现)

- 自然激励技术 (NExT) 与特征系统实现算法 (ERA)(Matlab代码实现)

- 5G系统关键无线技术介绍

- 要想推荐系统做的好,图技术少不了

- OFDM系统同步技术的matlab仿真,包括符号定时同步,采样钟同步,频偏估计

- 人工智能技术入门该读哪些书

- 【计算机三级数据库技术】第4章 数据库应用系统功能设计与实现--附思维导图

- Django技术全系列

- 腾讯技术团队最新出品,Android Framework系统框架底层原理解密

- Python基于OpenCV的指针式表盘检测系统(附带源码&技术文档)