基于FPGA的小波变换的verilog实现和硬件测试,使用quartusii平台

1.问题描述:

基于FPGA的小波变换的verilog实现和硬件测试,使用quartusii平台

2.部分程序:

`timescale 1ns / 10ps

//

// Company:

// Engineer:

//

// Design Name:

// Module Name: coff_delta

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module coff_delta(

i_din,

o_dout

);

input signed[15:0] i_din;

output signed[15:0]o_dout;

//0.4435068522

///2 /3 /4 /5 /9 /11 /12 /13 /14

wire signed[15:0]r0;

//0.4435068522

assign r0 ={i_din[15],i_din[15],i_din[15:2]} +

{i_din[15],i_din[15],i_din[15],i_din[15:3]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:4]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:5]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:9]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:11]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:12]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:13]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:14]};

//0.4435068522

assign o_dout = r0;

endmodule

`timescale 1ns / 10ps

//

// Company:

// Engineer:

//

// Design Name:

// Module Name: coff_alpha

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module coff_beta(

i_din,

o_dout

);

input signed[15:0] i_din;

output signed[15:0]o_dout;

//-0.052978515625

//1/5 1/6 1/8 /9 1/12

wire signed[15:0]r0;

//0.052978515625

assign r0 ={i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:5]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:6]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:8]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:9]} +

{i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15],i_din[15:12]};

//-0.052978515625

assign o_dout = ~r0 + 1'b1;

endmodule

3.仿真结论:

硬件测试图

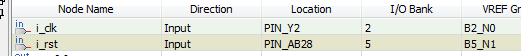

1.先进行管脚绑定

选择pin planner

这个就是管脚绑定。

3.然后对signaltap进行配置

小波shint编码压缩:

小波shint解压缩:

使用modeslsim进行仿真,结果如下

将仿真波形放大,其中小波变换之后如下所示:

编码解码如下所示

最后小波逆变换之后得到如下结果:

A17-9

相关文章

- 绕过CDN测试出真实IP

- 渗透测试MySQL扩展UDF后门原理与代码编写

- 关于接口测试自动化的总结与思考

- 性能测试知多少---性能需求分析

- MES对接Simba实现展讯平台 IMEI 写号与耦合测试

- Robot Framework - 2 - 创建测试库

- 测试平台使用git+Jenkins进行持续集成

- centos8平台使用ab做压力测试

- 云效平台——基于jmeter的轻量级性能测试平台

- SAP云平台 Document Information Extraction服务测试

- Tricentis NeoLoad:自动化的企业性能测试平台

- SAVE: 软件分析验证和测试平台

- 程序人生:“未来的测试人”听听一名老程序员的一点感悟!【经验谈】送给迷途中的你...

- 从0到1实现自动化测试平台(三):开发登录接口

- 测试必备工具 —— Postman实战教程

- 接口测试系列——转转接口测试平台实践

- C# OCR AspriseOcr测试使用图像文字中英文识别

- sqlmap的使用 ----常用tamper模块,TODO,绕过WAF的测试

- 利用http_load测试Web引擎性能

- 安全测试----使用Docker搭建SQL注入安全测试平台sqli-labs

- 全干工程师神器 - Jmeter 10 - Jmeter持续集成介绍及轻量级接口自动化测试框架(思维导图)

- 目标检测系列算法复现2:Darknet-YOLO-CUDA11-OpenCV4(Ubuntu平台)推理测试

- 针对域控制器的一种升级测试方案介绍

- 会充电的CANoe又来了|OBC测试系统

- 基于 HttpRunner 的接口自动化测试平台框架