【按键消抖】基于FPGA的按键消抖模块开发

2023-09-11 14:15:36 时间

1.软件版本

QUARTUSII8.1

Modelsim6.5d

2.系统源码

module tops(

i_clk, //100M

i_rst, //系统复位功能,高电平复位,如果不使用这个角,那么一直接低电平即可

i_input1, //按键输入1

i_input2, //按键输入2

o_output1,//脉冲输出1

o_output2,//脉冲输出2

test_cnt1,//测试计数器1

test_cnt2,//测试计数器2

test_enable1,//测试使能信号

test_enable2 //测试使能信号

);

//100M等于10ns,所以1s中就是10_000_000个100M时钟周期

//仿真的时候,为了方便看到仿真效果,所以将10_000_000改为一个较小的值10_000

//parameter NUM = 32'd10000000; //实际用

parameter NUM = 32'd100; //仿真用

input i_clk;//100M为10ns

input i_rst;

input i_input1;

input i_input2;

output o_output1;

output o_output2;

output[31:0]test_cnt1;

output[31:0]test_cnt2;

output test_enable1;

output test_enable2;

reg o_output1 = 1'b0;

reg o_output2 = 1'b0;

reg test_enable1 = 1'b0;

reg test_enable2 = 1'b0;

reg[31:0]cnt1 = 32'd0;

reg[31:0]cnt2 = 32'd0;

reg flag1 = 1'b1;

reg flag2 = 1'b1;

always @(posedge i_clk or posedge i_rst)//处理主要进程

begin

if(i_rst)//系统复位

begin

test_enable1 <= 1'b0;//定义使能信号

test_enable2 <= 1'b0;//定义使能信号

cnt1 <= 32'd0;

cnt2 <= 32'd0;

flag1 <= 1'b1;

flag2 <= 1'b1;

end

else begin

if(i_input1 == 1'b0 & i_input2 == 1'b1 & flag1 == 1'b1)//按下按键1,不按按键2

begin

//1s钟内使能维持10_000_000个时钟周期

cnt2 <= 32'd0;

if(cnt1 < NUM)//不到1s

begin

cnt1 <= cnt1 + 32'd1;

test_enable1 <= 1'b1;//输出1个脉冲,//按下按钮后,持续1s钟

test_enable2 <= 1'b0;

flag1 <= 1'b1;//用来屏蔽第二个按钮

flag2 <= 1'b0;//用来屏蔽第二个按钮

end

if(cnt1 == NUM)//到1s,停止输出

begin

cnt1 <= cnt1;

test_enable1 <= 1'b0;

test_enable2 <= 1'b0;

flag1 <= 1'b1;

flag2 <= 1'b1;

end

end

if(i_input1 == 1'b1 & i_input2 == 1'b0 & flag2 == 1'b1)//按下按键2,不按按键1

begin

//50s钟内使能维持

cnt1 <= 32'd0;

if(cnt2 < 50*NUM)//不到50s

begin

cnt2 <= cnt2 + 32'd1;

test_enable1 <= 1'b0;//输出1个脉冲,//按下按钮后,持续1s钟

test_enable2 <= 1'b1;

flag1 <= 1'b0;//用来屏蔽第1个按钮

flag2 <= 1'b1;//用来屏蔽第1个按钮

end

if(cnt2 == 50*NUM)//到1s,停止输出

begin

cnt2 <= cnt2;

test_enable1 <= 1'b0;

test_enable2 <= 1'b0;

flag1 <= 1'b1;

flag2 <= 1'b1;

end

end

if(i_input1 == 1'b1 & i_input2 == 1'b1)//不发生按键操作

begin

cnt1 <= 32'd0;

cnt2 <= 32'd0;

end

end

end

assign test_cnt1 = cnt1;

assign test_cnt2 = cnt2;

//下面根据是能信号,输出脉冲

//定义两个脉冲计数器

reg[31:0]pcnt1 = 32'd0;

reg[31:0]pcnt2 = 32'd0;

always @(posedge i_clk or posedge i_rst)//处理主要进程

begin

if(i_rst)//系统复位

begin

pcnt1 <= 32'd0;

pcnt2 <= 32'd0;

o_output1 <= 1'b0;

o_output2 <= 1'b0;

end

else begin

if(test_enable1 == 1'b1)//1s内一个100ns的脉冲,即1s内发生一个10M的脉冲信号

begin

pcnt1 <= pcnt1 + 32'd1;

if(pcnt1 < 32'd10)

begin

o_output1 <= 1'b1;//产生100ns的信号

end

else begin

o_output1 <= 1'b0;

end

end

else begin

pcnt1 <= 32'd0;

o_output1 <= 1'b0;

end

if(test_enable2 == 1'b1)//50s内50个100ns的脉冲,即1s内发生一个10M的脉冲信号

begin

if(pcnt2 == NUM-1)

begin

pcnt2 <= 32'd0;

end

else begin

pcnt2 <= pcnt2 + 32'd1;

end

if(pcnt2 < 32'd10)

begin

o_output2 <= 1'b1;//产生100ns的信号

end

else begin

o_output2 <= 1'b0;

end

end

else begin

pcnt2 <= 32'd0;

o_output2 <= 1'b0;

end

end

end

endmodule 3.仿真结论

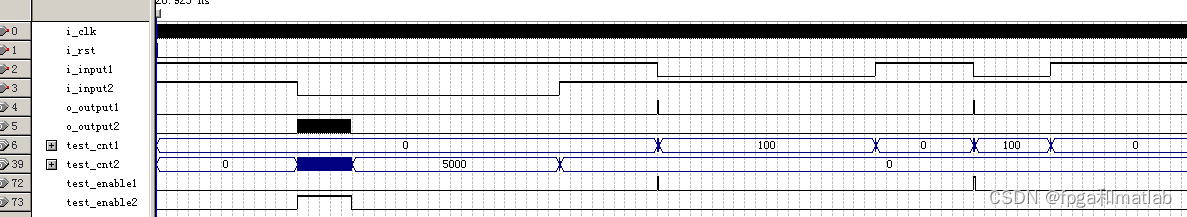

QII自带仿真说明:

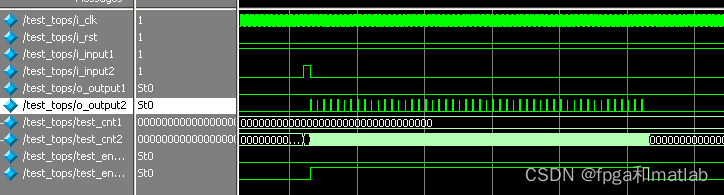

我们将波形进行局部放大:

第一部分,可以看到input1为高,input2为低,说明2按下了,所以output2产生连续的50个脉冲。

第二部分,input1为低,第一个按键按下了,所以只产生一个高电平信号

第三部分,还是第一个按钮被按下了,所以只产生一个脉冲。

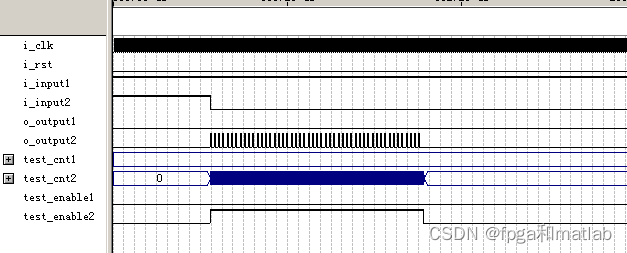

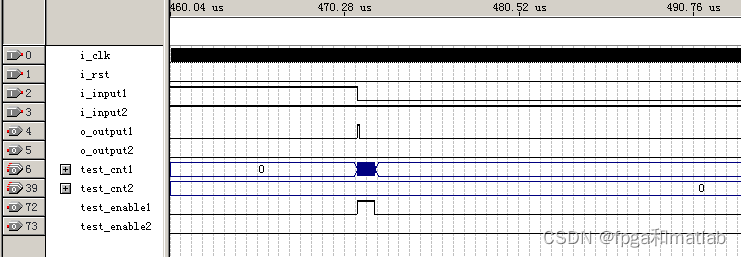

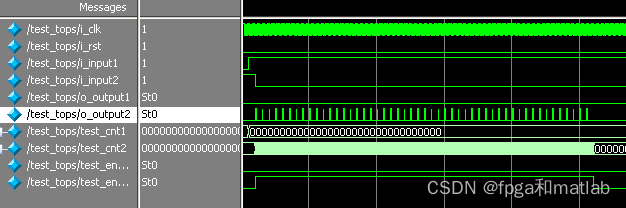

Modelsim仿真说明:

我们将仿真进行局部放大:

按键一按下:

按键二被按下;

还是按键二被按下。

A35-09

相关文章

- 4 ~ express ~ 划分模块开发

- Node.js处理I/O数据之Buffer模块缓冲数据

- Cocoapods多模块开发

- 第三百零四节,Django框架,urls.py模块,views.py模块,路由映射与路由分发以及逻辑处理——url控制器

- python-django框架-电商项目-订单模块开发_20191125

- python-django框架-电商项目-订单模块开发_20191125

- python-django框架-电商项目-购物车模块开发_20191125

- day15 内置模块和开发规范

- android系统 Audio模块

- 总结几个好用的CNN模块(Pytorch)

- python 时间模块 time datetime calendar

- 【Python自动化办公】分享几个好用到爆的模块,建议收藏

- python运维开发常用模块(7)web探测模块pycurl

- python运维开发常用模块(四)文件对比模块difflib

- 安卓开发之简单的短信操作模块

- LabVIEW编程LabVIEW开发 PXI-6259多功能IO模块 例程与相关资料

- JS模块式开发

- Laravel认证模块开发

- pytorch中Conv2d中模块的padding 参数使用

- Android Telephony RIL公开开发模块记录

- YOLOv7改进主干结构系列:结合丰富的梯度流信息模块,来自YOLOv8的核心模块

- python异常处理模块raise NotImplementedError

- 综合案例:利用ansible常用七种模块实现备份系统的部署及告警(十一)

- 2021 年全国职业院校技能大赛(中职组)网络安全竞赛 A 模块评分标准

- FPGA--VGA显示实验之Verilog代码描述(图像数据生成模块)