【高阶循环谱】基于FPGA的高阶循环谱的调制识别算法开发

2023-09-11 14:15:33 时间

1.软件版本

matlab2013b,quartusii12.1

2.本算法理论知识

参考文献《基于高阶循环累积量的 OFDM 子载波盲估计》

3.部分源码

`timescale 1ns / 1ps

module C4012_cal(

i_clk,

i_rst,

i_din,

o_C40,

o_FM

);

input i_clk;

input i_rst;

input signed[15:0]i_din;

output signed[15:0]o_C40;

output[1:0] o_FM;

reg signed[31:0]S2s;

reg signed[63:0]S4s;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

S2s <= 32'd0;

S4s <= 64'd0;

end

else begin

S2s <= i_din * i_din;

S4s <= i_din * i_din * i_din * i_din;

end

end

wire signed[15:0]S2;

wire signed[15:0]S4;

assign S2 = S2s[31:16];

assign S4 = S4s[63:48];

reg[11:0]cnt;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnt <= 12'd0;

end

else begin

if(cnt == 12'd2000)

cnt <= 12'd2000;

else

cnt <= cnt + 12'd1;

end

end

reg start;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

start <= 1'd0;

end

else begin

if(cnt == 12'd406)

start <= 1'd1;

else

start <= 1'd0;

end

end

wire signed[15:0]DOUT;

C4012 C4012_u(

.CLK (i_clk),

.RST (i_rst),

.START(start),

.DIN (i_din[15:6]),

.DOUT (DOUT),

.FM (o_FM)

);

reg [15:0] CNT;

reg signed[15:0]o_C40;

reg flag;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

flag <= 1'b0;

end

else begin

if(DOUT >= 1000)

flag <= 1'b1;

else

flag <= flag;

end

end

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

CNT <= 16'd0;

end

else begin

if(flag == 1'b1)

begin

CNT <= CNT + 16'd1;

if(CNT >= 16'd10000)

CNT <= 16'd10000;

end

end

end

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_C40 <= 16'd0;

end

else begin

if(CNT <= 100)

o_C40 <= DOUT;

else

o_C40 <= 16'd0;

end

end

endmodule 4.仿真分析

信号产生模块:

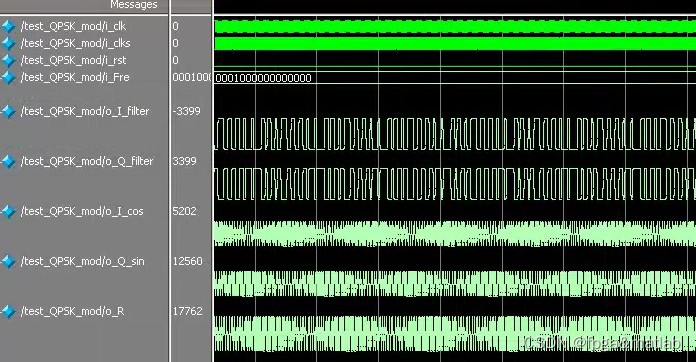

这个部分主要是QPSK和BPSK信号的产生。根据QPSK和FSK的计算公式,获得如下的modelsim仿真结果:

信道模块:

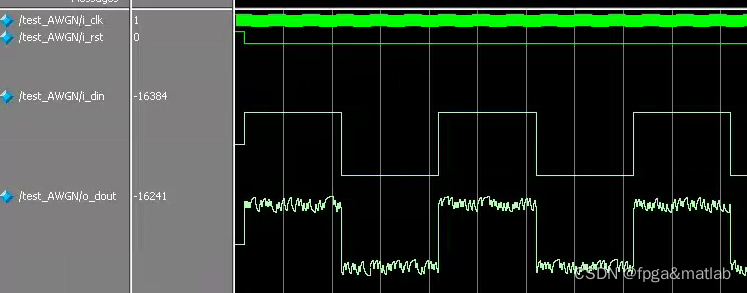

这个模块,主要是产生噪声信息。模拟一个高斯白噪声。即对输入信号加入白噪声。仿真结果如下所示:

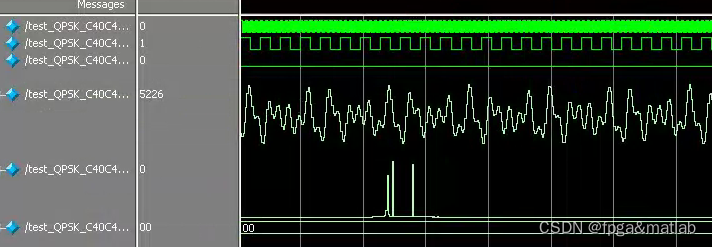

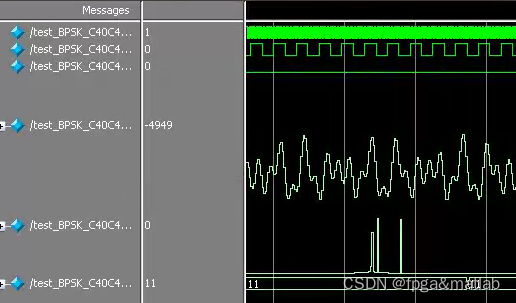

计算4阶循环累积算法:

下面开始对核心部分进行设计。计算C40,以及对应的FM。仿真结果如下所示:

QPSK:

FSK:

整个系统的RTL结构图如下所示:

5.参考文献

[1]郑文秀, 赵国庆, 罗明. 基于高阶循环累积量的OFDM子载波盲估计[J]. 电子与信息学报, 2008, 30(2):4.A01-107

相关文章

- Yii2给数据库表添加字段后对应模型无法识别到该属性的原因和解决办法

- 【问题解决方案】Keras手写数字识别-ConnectionResetError: [WinError 10054] 远程主机强迫关闭了一个现有的连接

- 阿里小蜜的语音识别、语义理解技术用的是哪家公司的产品?

- CV之OD:基于深度学习算法实现目标检测之GUI界面产品设计并实现图片识别、视频识别、摄像头识别(准确度非常高)

- android app用百度ocr识别sdk实现手写扫描功能(二)

- 【第20篇】像人类一样阅读:自主、双向和迭代语言 场景文本识别建模

- CVPR2021 行人重识别/Person Re-identification 论文+开源代码汇总

- Modelarts与无感识别技术生态总结(浅出版)

- m分别通过matlab和FPGA实现基于高阶循环谱的信号载波调制识别(四阶循环累量)仿真

- 如何利用AI识别未知——加入未知类(不太靠谱),检测待识别数据和已知样本数据的匹配程度(例如使用CNN降维,再用knn类似距离来实现),将问题转化为特征搜索问题而非决策问题,使用HTM算法(记忆+模式匹配预测就是智能),GAN异常检测,RBF

- python工具方法 1 tensorflow简单全连接神经网络,识别minist手写数字