【数字IC/FPGA】任意深度异步FIFO的设计

2023-09-14 09:16:18 时间

在许多资料中,都会讲到异步FIFO的深度必须为2的幂,否则无法使用格雷码设计。那么究竟是不是这样呢?博主查阅了一些资料,发现任意深度的异步FIFO都可以通过格雷码实现,只需要施加一些额外的处理即可。本文以深度为5的异步FIFO为例,介绍了任意深度异步fifo的设计流程。

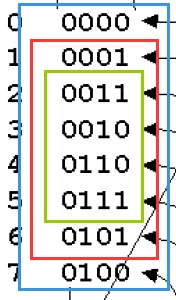

格雷码的对称性

如下图所示,格雷码不仅相邻两个数只有一个比特不同,它还有另外一个性质:首位去掉相同个数后,剩下的数仍然满足相邻数只有一个比特不同的性质,包括绕回。

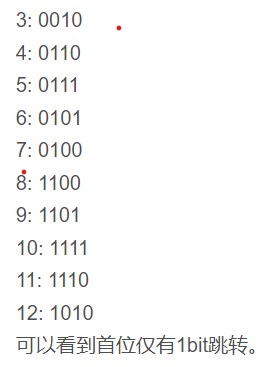

这个性质给了我们启发:我们现在要设计深度为5的异步FIFO,那么为了判断空满,我们还需要加上一个bit,即将深度5乘以2,也就是说,我们需要一个长度为10的序列,该序列满足相邻数只有一个位不同的性质,根据上述格雷码的性质,这是很容易做到的,我们只要取0-15的格雷码序列,并将它头部的0,1,2和尾部的13,14,15去掉即可:

使用了这个序列后,跨时钟域同步的问题得到了解决,但另一个问题是相应二进制码到实际RAM地址的映射:和之前的2的幂深度的fifo不同,在这里,二进制码的值并不能直接作为RAM的地址,需要作如下变换:

相关文章

- 你知道吗?印度IC工程师费用这么低!

- VK3601单键触摸芯片IC,适用单按键开关,台灯等

- IC验证工程师工作半年的成长和感悟

- 2023届数字IC面经 | 按部就班做好该做的事情

- IC面试:你很优秀,但是对不起

- 世微AP51656 60V高端电流采样降压恒流驱车灯IC

- AP5160 LED 2.5-100V 7.5A 降压恒流驱动IC 效率高 省空间

- AP6317 同步3A锂电充电IC 带散热 便携式设备 充电器

- Adobe IC 2019:创意与设计的完美融合 安装步骤+全版本安装包

- InCopy(Ic)2022软件下载 IC中文直装版下载 最新版Win/Mac附安装包

- InCopy(Ic)是一种什么软件可以用来做什么?Ic详细下载安装教程

- HM9232原厂12.8V, 10A高效升压IC转换器

- 5G logo敲定,IBM和爱立信携手推硅基毫米波相控阵IC | IoT科技评论周刊