【Verilog 流水线设计】以全加器为例阐述流水线设计的影响

目录

流水线设计思想

关于流水线对于FPGA设计中的作用,既有利也有弊,优点是能够优化时序从而提高系统运行的最大频率,缺点是增加延时,因为流水线的设计思想就是在计算过程中插入寄存器,从而增加了延时,下面就以一个八位全加器的例子去验证以上的论述。

全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

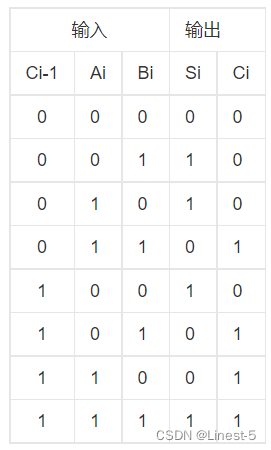

以下为全加器的真值表,可以看到其实和普通的加法没什么差别,就多了一个进位数,直接累加上就行。

非流水线全加器设计

不使用流水线的话,就比较简单粗暴,直接两个加数和进位一同相加得到最终的加法结果和进位值。

Verilog设计

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/* Engineer : Linest-5

/* File : add_no_pipeline.v

/* Create : 2022-09-02 09:29:04

/* Module Name : add_no_pipeline

/* Description : 全加器非流水线设计

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

module add_pipeline(

input clk,

input [7:0] a,

input [7:0] b,

input cin,

output reg [7:0] sum,

output reg cout

);

always @(posedge clk) begin

{cout,sum} <= a + b + cin;

end

endmodule testbench设计

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/* Engineer : Linest-5

/* File : tb_add_no_pipeline.v

/* Create : 2022-09-02 09:34:46

/* Module Name : tb_add_no_pipeline

/* Description : 全加器非流水线设计仿真模块

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

`timescale 1ns/1ps

module tb_add_no_pipeline();

reg clk;

reg [7:0] a;

reg [7:0] b;

reg cin;

wire [7:0] sum;

wire cout;

initial begin

clk = 'd1;

end

always #10 clk = ~clk;

always #20 a <= {$random}%256;

always #20 b <= {$random}%256;

always #20 cin <= {$random}%2;

add_pipeline inst_add_pipeline (

.clk(clk),

.a(a),

.b(b),

.cin(cin),

.sum(sum),

.cout(cout)

);

endmodule仿真波形

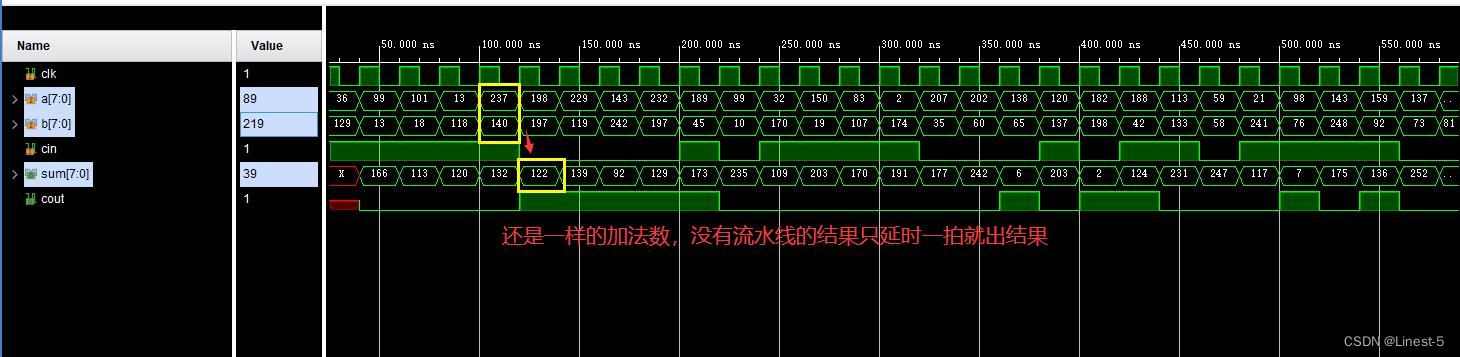

可以很清晰的看到,加数为237和140,相加为377,这超过了8位最大值,因此需要进一位,最终加法结果为sum = 377-255 = 122,进位cout = 1,并且只使用了一拍时钟周期就得到了结果。

RTL视图

从RTL图中可以看到结构很简单,两个加法器并对输出结果打一拍即可。

资源使用情况

可以看到LUT使用了8个,触发器使用了9个。

流水线加法器设计

这里使用一级流水设计方法,即将a、b 8位加法拆分开计算,分别计算a、b 的低四位和高四位,将最终的结果拼接在一起即得到最终的计算结果。

Verilog设计

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/* Engineer : Linest-5

/* File : add_pipeline.v

/* Create : 2022-09-02 09:25:18

/* Module Name : add_pipeline

/* Description : 全加器的流水线设计

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

module add_pipeline(

input clk,

input [7:0] a,

input [7:0] b,

input cin,

output reg [7:0] sum,

output reg cout

);

reg [3:0] a_reg;

reg [3:0] b_reg;

reg [3:0] sum1;

reg cout1;

//计算低四位

always @(posedge clk) begin

{cout1,sum1} <= a[3:0] + b[3:0] + cin;

a_reg <= a[7:4];

b_reg <= b[7:4];

end

//计算高四位

always @(posedge clk) begin

{cout,sum[7:4]} <= a_reg + b_reg + cout1;

sum[3:0] <= sum1;

end

endmodule testbench设计

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

/* Engineer : Linest-5

/* File : tb_add_pipeline.v

/* Create : 2022-09-02 09:30:52

/* Module Name : tb_add_pipeline

/* Description : 全加器的流水线设计仿真模块

/*~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~*/

`timescale 1ns/1ps

module tb_add_pipeline();

reg clk;

reg [7:0] a;

reg [7:0] b;

reg cin;

wire [7:0] sum;

wire cout;

initial begin

clk = 'd1;

end

always #10 clk = ~clk;

always #20 a <= {$random}%256;

always #20 b <= {$random}%256;

always #20 cin <= {$random}%2;

add_pipeline inst_add_pipeline (

.clk(clk),

.a(a),

.b(b),

.cin(cin),

.sum(sum),

.cout(cout)

);

endmodule仿真波形

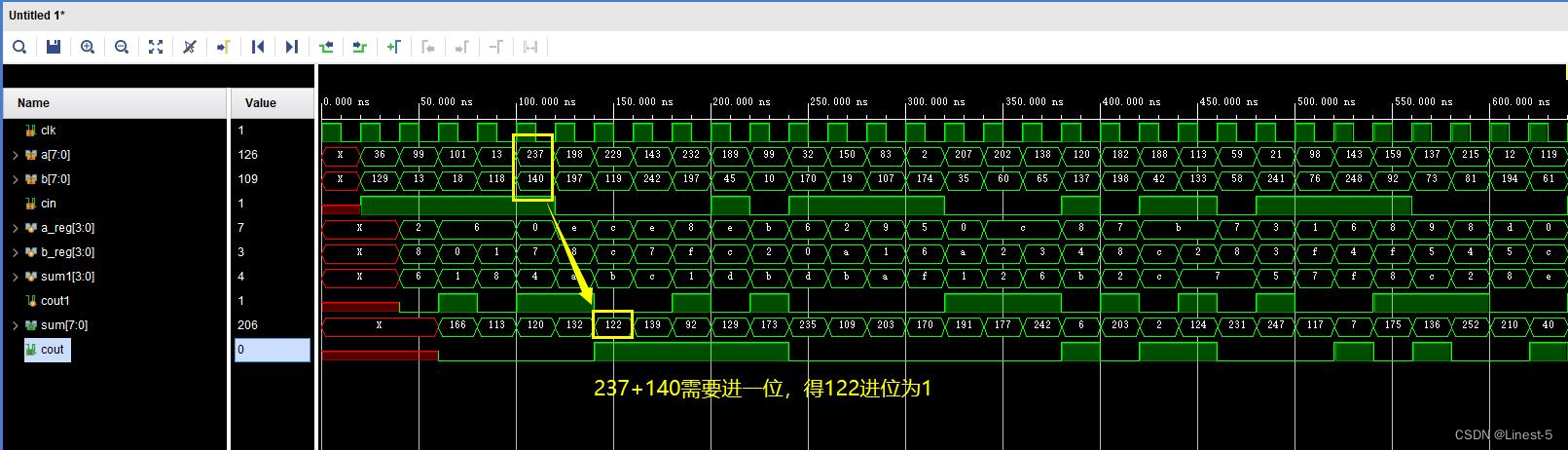

可以看到和非流水线设计的仿真图形不同的是,加法结果需两个时钟周期才能出结果,结果也是正确的,这与前面说的一致。

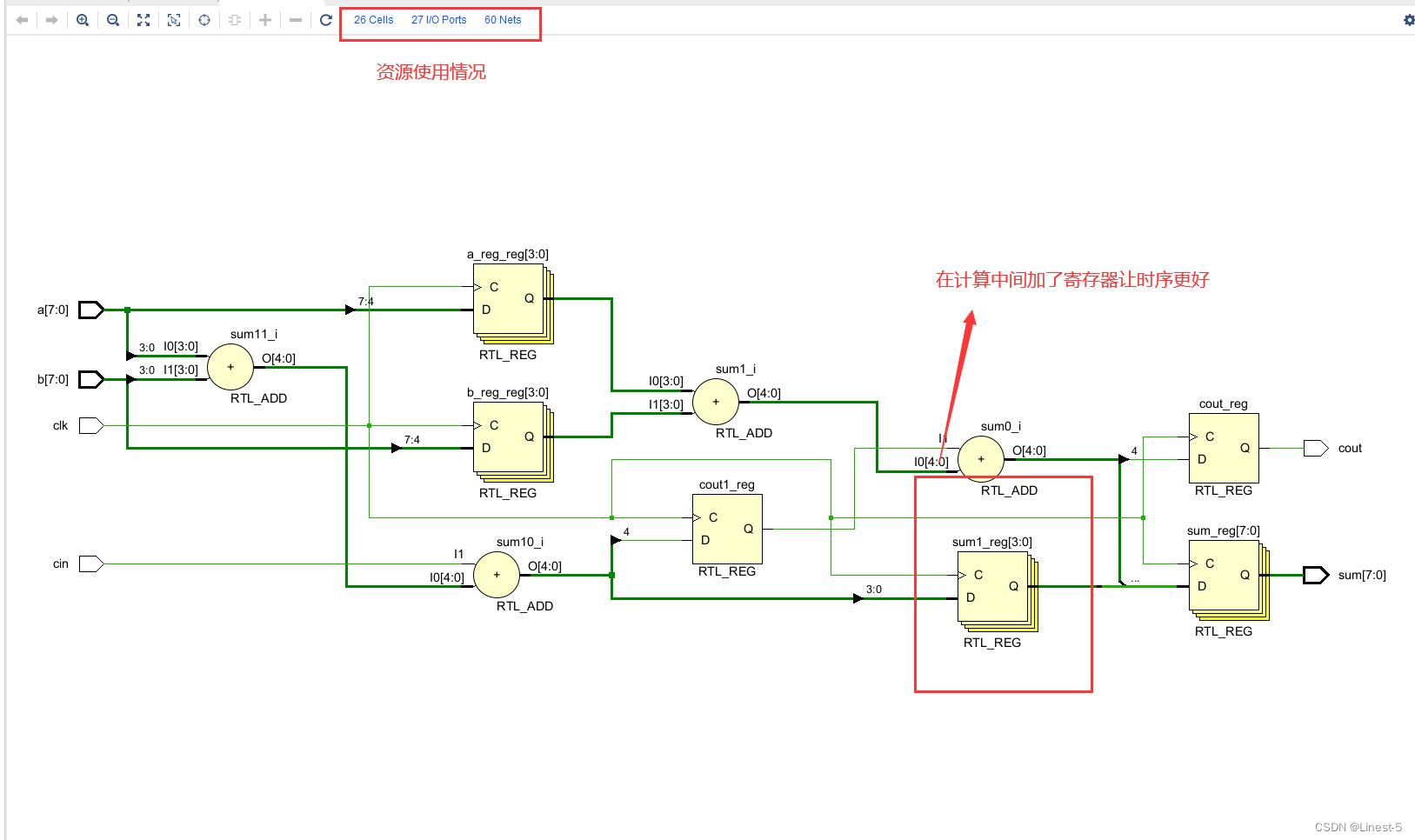

RTL视图

从RTL图可以看到,相比较非流水线的RTL图,流水线设计的全加器使用的资源明显更多,在计算链上插入了红框中的寄存器,这样可以一定程度上优化时序并提高系统的最大工作频率值。

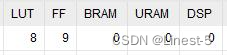

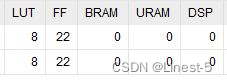

资源使用情况

与非流水线设计的相比,LUT同样使用了8个,但是触发器个数却是其2倍多,这就是流水线设计的弊端,尤其是大位宽的计算,更是资源消耗成倍的增加,这就是有得必有失。

总结

流水线设计在FPGA中应用得很广泛,至于什么时候选择使用流水线设计:当资源充足的情况下,需要提高系统运行速率,这时就可以使用流水线的设计,这是用资源换速率的案例,当然使用的流水线的部分计算延时也会增加,但能提高整体系统的运行速率,这点延迟可以忽略不计。

相关文章

- AI设计

- 高复用率的RTSPClient组件EasyRTSPClient设计流程概述

- 基于FPGA的直接序列扩频通信verilog设计,包括汉明编译码,扩频解扩,同步模块以及testbench

- 如何设计一个消息中间件? 消息中间件的总体架构

- 面向对象设计原则之接口隔离原则

- 数据结构和算法设计专题之---八大内部排序

- VL36-状态机-重叠序列检测;设计一个状态机,用来检测序列1011.

- IC/FPGA设计中的静态时序分析(STA)

- 通讯电平转换电路中的经典设计

- 【网络结构设计】8、ConvNeXt | 卷积神经网络还有很大的优化空间

- 基于Java+SpringBoot+Vue前后端分离商城系统设计与实现

- 并行数据流转换为一种特殊串行数据流模块的设计:设计两个可综合的电路模块,第一个模块(M1)能把4位的并行数据转换为符合以下协议的串行数据流