【数字IC/FPGA】数据累加输出

2023-09-14 09:16:18 时间

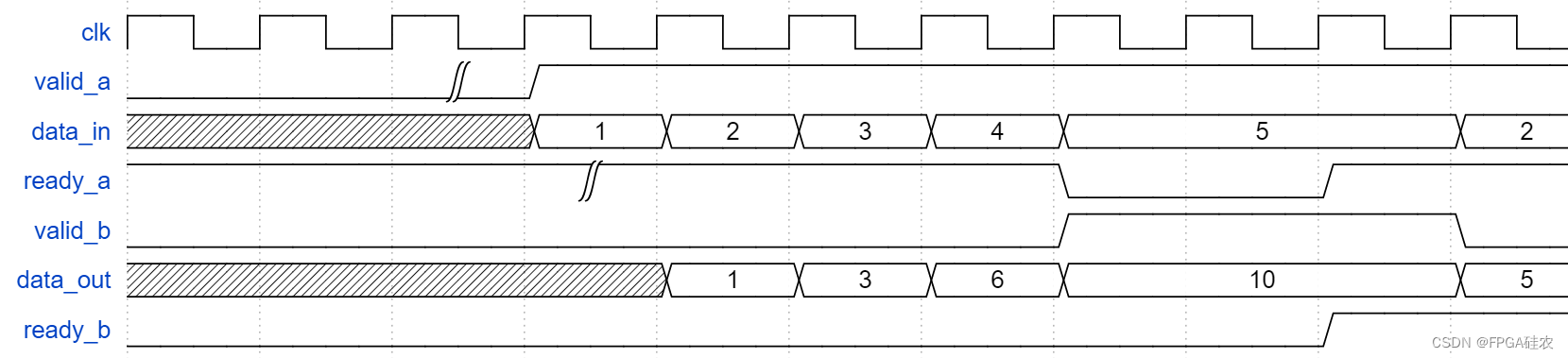

题目描述:实现串行输入数据累加输出,输入端输入8bit数据,每当模块接收到4个输入数据后,输出端输出4个接收到数据的累加结果。输入端和输出端与上下游的交互采用valid-ready双向握手机制。要求上下游均能满速传输时,数据传输无气泡,不能由于本模块的设计原因产生额外的性能损失。

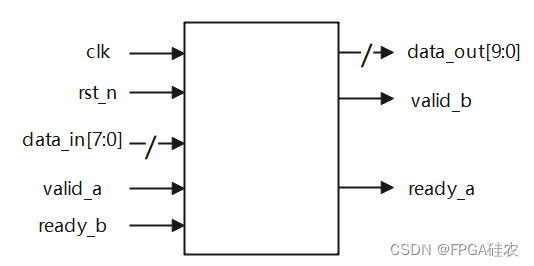

电路的接口如下图所示。valid_a用来指示数据输入data_in的有效性,valid_b用来指示数据输出data_out的有效性;ready_a用来指示本模块是否准备好接收上游数据,ready_b表示下游是否准备好接收本模块的输出数据;clk是时钟信号;rst_n是异步复位信号。

代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

相关文章

- Vue+ElementUI项目使用webpack输出MPA

- [C#] 常用工具类——直接在浏览器输出数据

- 【C语言入门教程】3.2 数据的输入 与 输出

- destoon8.0生成输出热门搜索sitemap地图方法

- 大叔经验分享(66)docker启动tomcat不输出catalina.out

- SPSS输出结果如何在word中设置小数点前面显示加0

- Qt开源作品39-日志输出增强版V2022

- ASP.NET Core 6框架揭秘实例演示[15]:针对控制台的日志输出

- Scala里的控制台输出print实现原理

- Excel:python结合Excel使用技巧经验总结之(将python输出的等间隔列数据直接粘贴复制存到物理表格内等)图文教程之详细攻略

- AIGC:利用人工智能生成技术之依次生成文本类、图片类内容并对比多个前沿模型(GPT-3.5、GPT-4、Claude)的输出结果并分析性能案例集合

- Python之pandas:对dataframe数据的索引简介、应用大全(输出索引/重命名索引列/字段去重/设置复合索引/根据列名获取对应索引)、指定某字段为索引列等详细攻略

- TF之CNN:CNN实现mnist数据集预测 96%采用placeholder用法+2层C及其max_pool法+隐藏层dropout法+输出层softmax法+目标函数cross_entropy法+

- m基于遗传优化的复杂工序调度matlab仿真,输出甘特图和优化收敛图

- 习题 9.11 将例9.13中的Time类声明为Date类的友元类,通过Time类中的display函数引用Date类对象的私有数据,输出年、月、日和时、分、秒。

- 习题 3.10 有一函数:写一程序,输入x,输出y值。

- log4js-node:node.js日志框架输出到文件

- Java通过PDF模板导出数据 adobe acrobat的PDF编辑器 itextpdf java导出文件输出流

- 【数字信号处理】线性时不变系统 LTI “ 输入 “ 与 “ 输出 “ 之间的关系 ( 线性卷积起点定理 | 左边序列概念 | 推理 )

- TreeSet和TreeMap的输出

- VL48-使用Verilog解决多bit MUX同步器—慢时钟域同步到快时钟域(多bit跨时钟域),快时钟同步使能端并通过该使能端控制输出数据

- 同步FIFO(计数器法),8位数据,没有扩展位,以计数器的方式来输出空满!

- VL33-非整数倍数据位宽转换8to12,实现先到的数据应置于输出的 高bit 位。

- VL30-数据串转并电路(移位寄存器实现),实现一个6bit位的拼接,拼接完成后输出信号!

- 数据累加输出

- 特征学习——特征工程自动化,无非类似CNN最后一层softmax前的输出层就是特征表征层,但那是分类器,如何用在无标注数据中是难点——word2vec对“上下文”距离建模来实现特征提取;此外,kernel mechine的结合相当于学习内核,即特征空间

- 用流控制成员函数输出数据

- 计算机存的(识别)补码,那输出打印时是补码还是原码?

- 浮点型数据的输入和输出(C语言)

- flume监控一个文件实时采集新增的数据输出到控制台

- ffprobe输出相关参数的解析

- 1043 输出PATest

- 原子半导体第7题:请使用超过一种方法去写一个可综合的Verilog代码去选择一个64个输入数据给输出。