信号完整性(SI)电源完整性(PI)学习笔记(三十二)电源分配网路(四)

电源分配网路(四)

1.从稳压模块和体电容器不再提供低阻抗直到频率约为100MHz的范围内,设计电源分配网络阻抗曲线的策略就是选择合适容值和个数的电容器,以保持阻抗峰值低于目标阻抗。

n个电容器并联的等效电容、电阻和电感分别为:

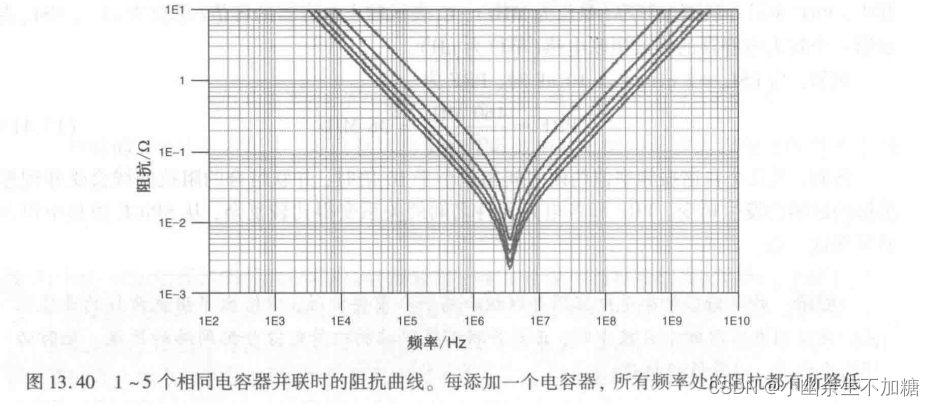

2.多个相同电容器并联的阻抗曲线,如图,该图表明总的RLC曲线轮廓保持相似,但整个频率范围内的总的阻抗是变化的。

3.两个电容器并联的性能与单个的RLC模型一样,在自谐振频率处拥有相同的低阻抗下冲。大电容器的自谐振频率较低,小电容器的自谐振频率较高。当各自的理想电容容抗与该电容器的理想电感感抗匹配时,就会发生谐振情况,并联电容器组合的自谐振频率和单个电容器各自的自谐振频率相同。另外,在自谐振频率之间有一个新的特征,即阻抗的峰值称为并联谐振峰值,它发生在并联谐振频率(PRF)处。

4.并联谐振频率是电容器并联组合的一个重要特性,它给出了阻抗曲线的峰值位置,当使用电容器个数较少时,正是并联谐振阻抗制约着电源分配网络的性能。

并联谐振频率处的阻抗峰值粗略计算为:

降低阻抗峰值的重要途径:

(1)减小较大电容器的等效串联电感;

(2)增大较小电容器的容器;

(3)同时增大两个电容器的等效串联电阻。

5.一个电容器的等效串联电阻与构造电容器的多层平行板金属化平面有关,通常情况下容值越大,平行板的层数就越多,等效串联电阻越小。

使用小容值电容器可以做到有较高的ESR值,从而得到较低的并联谐振峰值。

6.减小ESL值是降低阻抗峰值的一种重要方法。另一种方法是添加更多的电容器。

7.如何选择添加电容器的以降低并联谐振峰值?

当有个具有不同的自谐振频率的电容器并联时,在他们的自谐振频率之间形成了一个并联谐振阻抗峰值。这个阻抗峰值可以通过添加一个其自谐振频率介于他们之间的电容器加以降低。

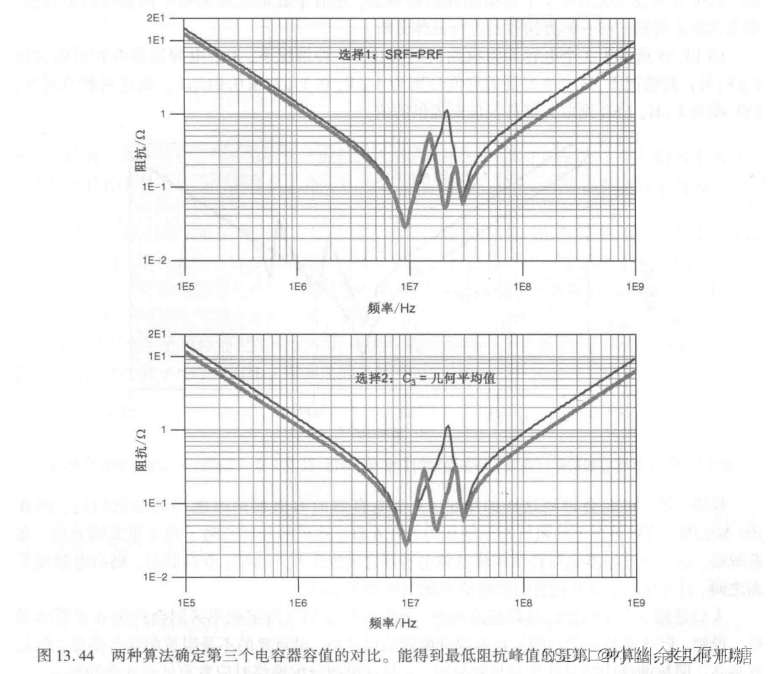

第三个电容器的自谐振频率最佳值和所有三个电容器的容值,ESL和ESR都有关系。采用SPICE求出这个最佳值:

(1)让第三个电容器的自谐振频率和并联谐振频率相一致;

(2)或使第三个电容器的自谐振频率值取为处于其他两个电容器自谐振频率值之间的某个值。

结论:当每个电容器的ESL值都相同时,可以设计添加一个容值为其他两个容值几何平均的电容器以得到最低的阻抗峰值。

8.很多手册建议,每对电源/地的封装引脚上加3个电容器。理由是他们会在特定频率区间产生非常低的阻抗。但是很重要的不是阻抗曲线有多低,而是有多高,阻抗曲线的高峰值会导致电路故障。

9.降低这一低频阻抗峰值的主要方法是减小体电容器的电感。如果在设计中不能减小,那么将更多的电容并联。

10.对于频率在100MHz以下的情况,减小阻抗峰值的方法有以下6种:

(1)大幅度加大接在平面上的电容值,从而将其自谐振频率降到很低,而且阻抗峰值也要降低。

(2)减小平面电容,是并联谐振频率高于100MHz;

(3)减小去耦电容器的电感;

(4)增大电容器的等效串联电感;

(5)调整某个电容器的容值,是其自谐振频率接近于并联谐振频率;

(6)添加一个自谐振频率接近于并联谐振频率的电容器。

11.(1)在低频段,可以通过调整体电容器的容值和个数来保持阻抗低于目标阻抗;

(2)在高频段,电容器组合可以得到相对最低的阻抗(由等效串联电感并联值决定)

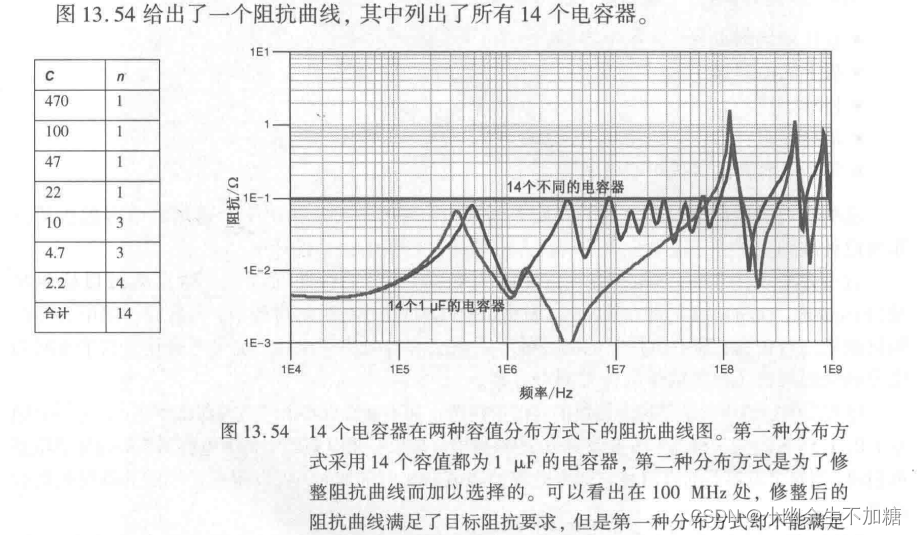

满足目标阻抗所需要的电容器的最少个数是评估设计优化程度的一个优质指标参数

12.通过优选电容器容值就能用最少的电容器设计出平坦的阻抗曲线,只要精选电容器的容值,就能做到满足目标阻抗所需电容器个数最少,这一过程是在修正阻抗曲线。

所选目标电容器的个数和最优值取决于:

稳压模块附带的体去耦电容器;板上的电容量,目标阻抗,最高频率,每个电容器的等效串联电感。

13.修正阻抗曲线的方法:从低频开始,选择最大值的电容器并进行仿真。对每一种容值都加上足够个数电容,使阻抗峰值低于目标阻抗,然后再添加足够个数的下一种容值的电容器直到满足目标阻抗。

14.需要培养的重要设计习惯:

(1)依照组装的设计规则,采用尽量短而粗的表层布线;

(2)电容器要放在靠近封装的位置, 有一些可以放在封装下面的电路板底层,还有一些可以放在封装的同一顶层,要避免这些外围电容使扩散电感饱和。

(3)当电源/地平面相邻层是在不增加成本的情况下尽量使用最薄的介质;

(4)如果有可能,则应使用电源/地腔尽可能靠近PCB的表面层。

相关文章

- ADRC学习笔记( 一)[通俗易懂]

- 《算法竞赛进阶指南》0x00 基本算法 - 学习笔记

- GoogLeNet论文学习笔记

- web前端学习/工作笔记(四)

- PCEP 协议学习笔记

- git学习笔记

- [学习笔记]unity3d-UGUI

- Selenium WebDriver API 学习笔记(二):浏览器控制

- Rust变成学习笔记Day9 值的使用及如何销毁?

- spring学习笔记一 入门及配置详解编程语言

- Java基础学习笔记九 Java基础语法之this和super详解编程语言

- Spark学习笔记6:Spark调优与调试详解大数据

- HBase笔记详解大数据

- 使用Redis培训机构学习心得(培训机构redis笔记)

- 在线rss阅读聚合器lilina-0.7安装笔记

- JavaScript学习笔记(十二)dom

- Android笔记之:在ScrollView中嵌套ListView的方法

- JQuery中使用.each()遍历元素学习笔记

- Nodejs学习笔记之Stream模块