RFSoC应用笔记 - RF数据转换器 -12- RFSoC关键配置之其他功能(三)

前言

本文参考官方手册,主要对RFSOC的上电顺序、TDD 模式、比特流重配置等内容进行介绍。

文章目录

上电序列

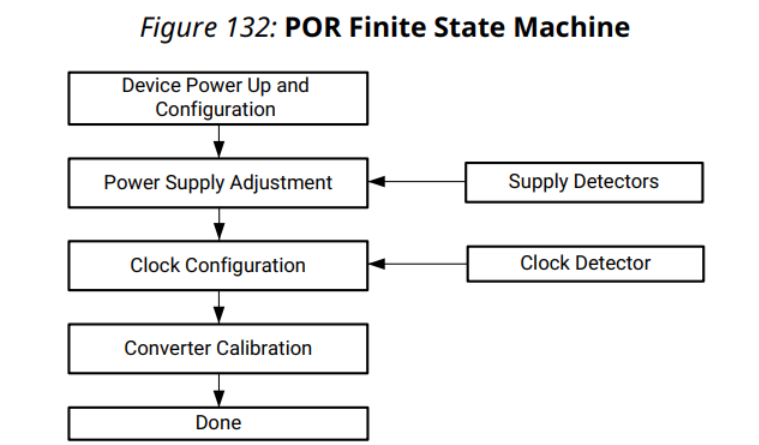

Tile 由不同的独立模块组成,由不同的电源供电,并由不同版本的主时钟提供时钟。 瓦片必须以已知的顺序出现,转换器才能正常工作。 当使用比特流配置或重新配置器件时,上电状态机会自动运行,但也可以在软件控制下随时重新运行。

仅当所有外部时钟都运行且稳定(无故障)时,才应启动 IP。如果需要延迟启动直到外部时钟有效,IP AXI4-Lite 复位 (s_axi_aresetn) 可以保持低电平。

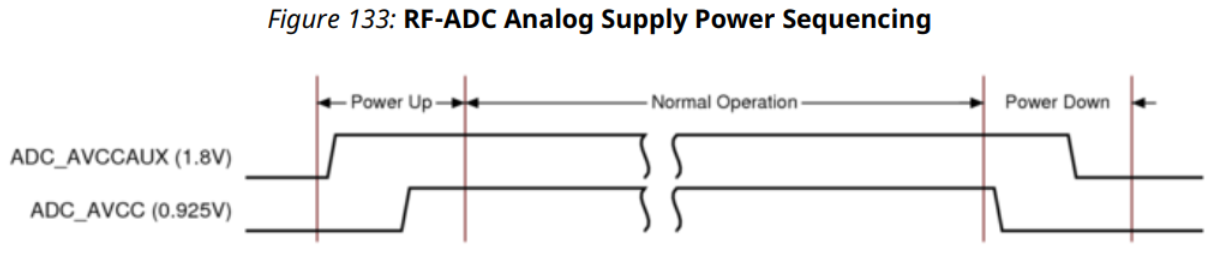

RF-ADC 模拟电源电源排序(第 3 代)

RF-ADC 电源有一个推荐的上电和断电顺序,以确保安全运行。 下图显示了 ADC_AVCC 电源应在 ADC_AVCCAUX 电源上电后上电并在 ADC_AVCCAUX 电源下电前断电的推荐顺序。只要遵循/遵守顺序,供电斜坡之间就没有特定的延迟时间。

如果实施的电源管理具有大多数稳压器常见的 Power Good 和 Enable 引脚,则可以启用此功能。 ADC_AVCCAUX 的电源良好指示灯可用作 ADC_AVCC 稳压器的使能控制。 Xilinx 推荐用于数据转换器模拟电源的全开关模式电源解决方案,因为大多数应用的电源效率高于基于低压差 (LDO) 的解决方案。

开机顺序步骤

| Sequence Number | State | Description |

|---|---|---|

| 0-2 | Device Power-up and Configuration | Vivado 中设置的配置参数被编程到转换器中。 然后状态机等待外部电源上电。 在硬件中,这可能需要长达 25 毫秒。 然而,这在行为仿真中减少到 200 μs。 |

| 3-5 | Power Supply Adjustment | 配置设置传播到转换器的模拟部分。 此外,RF DAC 中的稳压器、偏置设置和 RF-ADC 中的共模输出缓冲器均已启用。 |

| 6-10 | Clock Configuration | 状态机首先检测到转换器中是否存在良好的时钟。 然后,如果启用了 PLL,它会检查 PLL 锁定。 然后将时钟释放到转换器的数字部分。 |

| 11-13 | Converter Calibration (ADC only) | 校准在 RF-ADC 中进行。 在硬件中,第 1 代/第 2 代可能需要大约 10 毫秒,第 3 代需要 63 毫秒。但是,在行为仿真中,这会减少到 60 微秒。 在第 3 代器件中,共模过压和欠压信号会在校准过程开始之前进行监测。 在开始校准之前,两个信号都必须为低电平。 |

| 14 | Wait for deassertion of AXI4- Stream reset | 在 AXI4-Stream 时钟稳定之前,应断言 Tile 的 AXI4-Stream 复位。 例如,如果时钟由 MMCM 提供,则应保持复位直到它实现锁定。 状态机在此状态下等待,直到复位无效。 |

| 15 | Done | 状态机已完成上电序列。 |

重新启动所有 Tile

要在软件控制下重新启动所有 Tile 并在初始化后执行完整的上电序列,请执行以下步骤:

- 将 0x0000_0001 写入主复位寄存器以重新启动所有 Tile(开始和结束状态恢复为其默认值,因此 无需将 0x0000_000F 写入单个 tile 重启状态寄存器)。

- 轮询每个单独的块的块重启上电状态机寄存器以检查操作是否完成。 当该寄存器读取全零时,上电序列完成。

Restart Tile

要在软件控制下在初始化后重新启动 Tile 并执行完整的开机顺序,请执行以下步骤:

-

任何一个即可

a. 将 0x0000_000F 写入 tile< n > 重新启动状态寄存器以使用 Vivado IDE 配置重新启动;

b. 将 0x0000_010F 写入 tile< n > 重启状态寄存器以使用当前配置(可能与 Vivado 设置不同)重启。 -

将 0x0000_0001 写入 tile< n > 重启上电状态机寄存器以重启 tile。

-

轮询 tile< n > Restart Power-On State Machine 寄存器检查操作是否完成; 当该寄存器读取全零时,上电序列完成。

Power-Down Tile

要关闭一个 tile,重新运行通电序列的方式与重新启动一个 tile 的方式相同,但 End State 设置为 3 而不是 F。将 End State 设置为 3 可以清除通电序列器 所有寄存器,而无需执行完整的上电序列。 执行以下步骤来关闭 tile:

-

将 0x0000_0003 写入各个 tile 重启状态寄存器。 在第 3 代器件中使用多块同步时,如果块在 SYSREF 链中,则应将 0x0000_0006 写入各个块重启状态寄存器。

-

将 0x0000_0001 写入 tile< n > 重启上电状态机寄存器以重启 tile。

-

轮询 tile< n > Restart Power-On State Machine 寄存器检查操作是否完成; 当该寄存器读取全零时,掉电序列完成。

TDD 模式(第 3 代)

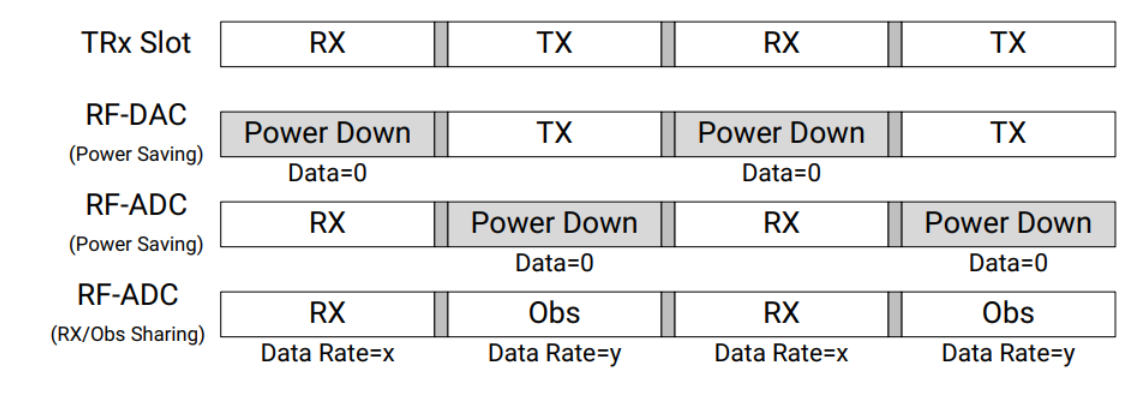

时分双工 (TDD) 是一种无线系统架构,它使用相同的载波频率进行发送和接收。 这意味着 TX (RF-DAC) 和 RX (RFADC) 不需要同时处于活动状态。RFSoC 支持以下两种模式:

- TDD 省电模式:RFSoC 允许独立的 RF-ADC 或 RF-DAC 通道在任何给定时刻断电和唤醒,从而产生可观的系统功耗储蓄。

- TDD RX/Obs 共享模式:RFSoC 允许在不同时隙的 RX 和观察 (Obs) 模式之间共享 RF-ADC 的子集,两个 RF-ADC 抽取状态(数据速率)保持在 它们之间的动态切换。

下图显示了 RFSoC 在 TDD 应用中的工作方式。

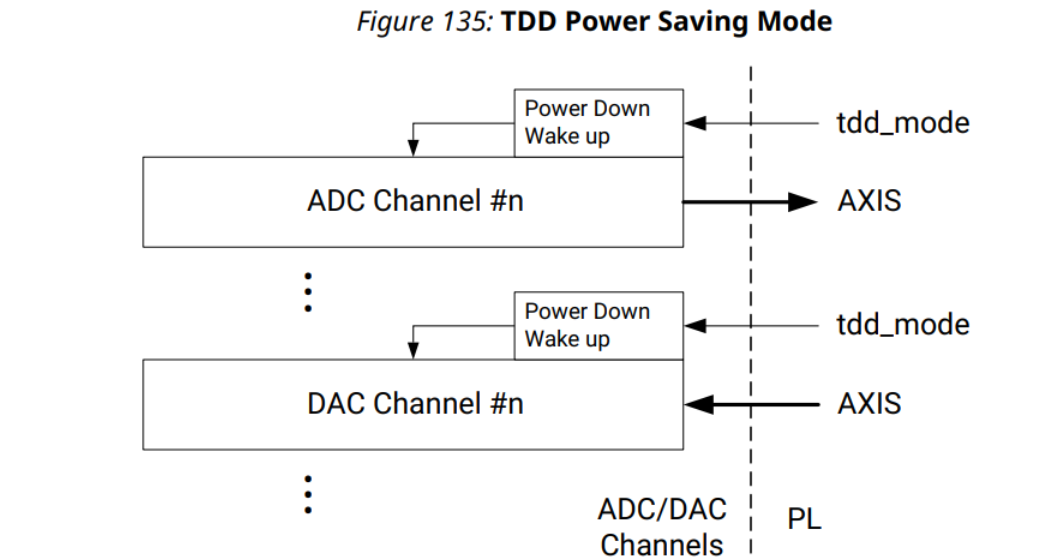

TDD 省电模式

在 TDD 省电模式下,每个转换器通道都使用 PL 输入独立控制。 瓦片同步、时钟和通道状态被保留。 当 RF-ADC 处于断电和唤醒状态时,无需用户干预即可自动处理交错校准。下图说明了 TDD 省电模式。

实时 tdd_mode 信号可用于进入和退出每个转换器的省电模式。在掉电状态下,RF-ADC 和 RF-DAC 都输出 0。当存在多个转换器通道时,Zynq UltraScale+ RFSoC RF 数据转换器 IP 内核使用小的内部延迟来错开通道的启动,以防止电源上出现大的步进电流。

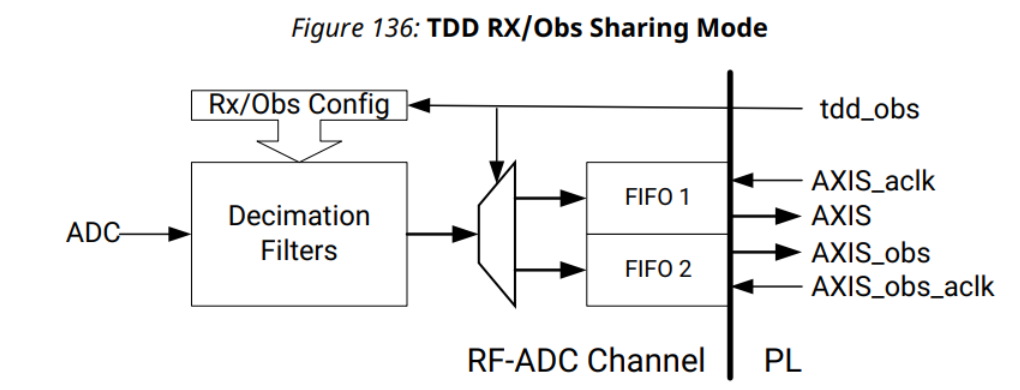

TDD RX/Obs Sharing Mode

在 TX 时隙中,一些 RX 通道可以被复用为 TX 观察通道进行 PA 线性化。 观察通道,一般来说,比RX通道需要更宽的带宽; 这会导致 RX 和 Obs 配置之间的抽取因子和数据速率不同。

在 IP 配置中启用 TDD RX/Obs 共享模式时,每个 RF-ADC 通道都有两个 AXI4Stream 接口可用。 请注意,它们不会同时处于活动状态。

每个 AXI4-Stream 的抽取因子、输出数据速率和 FIFO 配置都独立保留,并且可以使用 PL 输入 (tdd_obs) 动态切换。 请注意,RX 和 Obs 配置共享 RF-ADC 中的其他功能块,例如复混频器/NCO、DSA 等。例如,为 RX 和 Obs 通道选择相同的实数/复数模式和相同的 NCO 频率。 当 RF-ADC 从一种模式切换到另一种模式时,DSA 值会有所不同。 您应该每次通过实时端口或 RFdc API 设置所需的 DSA 值。

多图块同步 (MTS) 仅对 RX 模式有效,在 Obs 模式下不支持。MTS 保持其状态,不会在 RX/Obs 模式切换时受到影响。

两个 PL 时钟(AXIS_aclk、AXIS_obs_aclk)可用于不同的数据速率。下图说明了 TDD RX/Obs 共享模式。

比特流重配置

当有一个或多个块在运行时,要加载新比特流或将当前比特流重新加载到RFSoC 中,必须遵循以下步骤以确保安全运行。 在重新配置事件期间未能遵循这些步骤可能会影响部件的使用寿命可靠性。

- 使模拟前端静音以避免 TX 和 RX 信号。

- 使用 XRFDC_Shutdown API 命令或 Power-Down Tile 寄存器单独关闭所有使用的 RF-ADC 和 RF-DAC 块。

- 加载新的比特流或重新加载现有的比特流。

- 配置完成后,IP 中的上电状态机将按照正确的顺序启动磁贴。

与 AXI4-Stream 接口的接口

AXI4-Stream 接口的数量和每条总线的宽度取决于 Vivado 中选择的操作模式所需的带宽。 内插和抽取可以降低 AXI4-Stream 带宽要求,并且可以在 IP 内核配置屏幕上选择每个 AXI4Stream 接口的宽度以及时钟速率和内插/抽取设置。

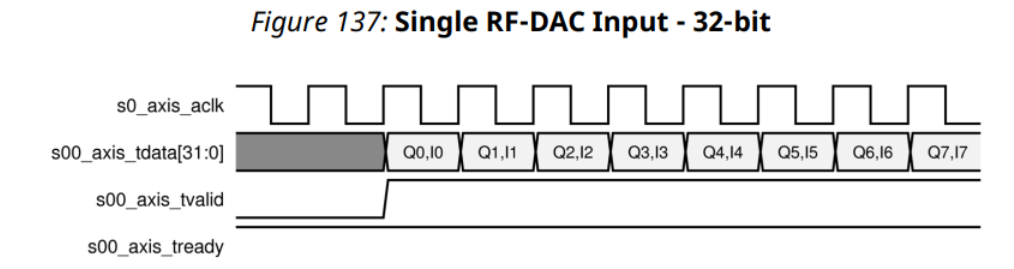

下图显示了 4 GSPS 的单个 RF-DAC 数据输入,在 500 MHz 运行的单个 AXI4-Stream 接口上具有 8 倍的 I 和 Q 插值。

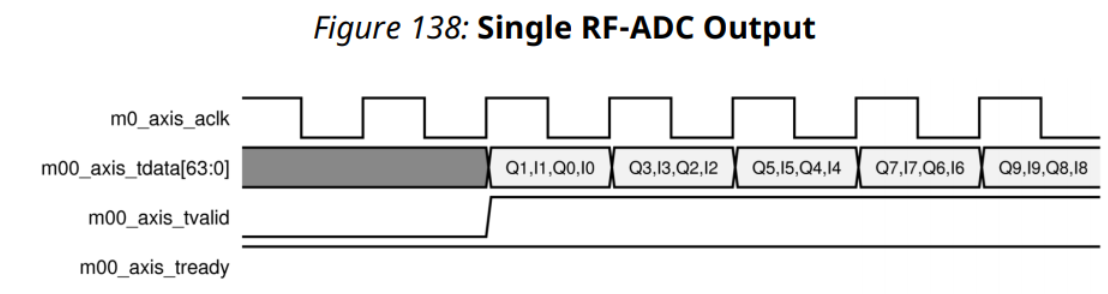

下图显示了在 500 MHz 运行的单个 AXI4-Stream 接口上具有 4x 抽取和 I 和 Q 的 RF-ADC。

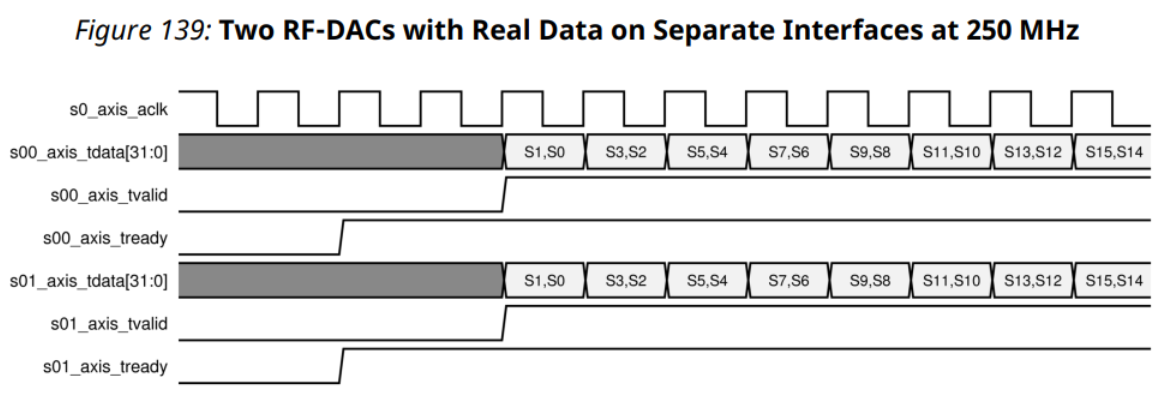

下图显示了 4 GSPS 的 2x32 位 RF-DAC,具有真实数据、8x 插值,并以 250 MHz AXI4-Stream 时钟运行。

reference

1.PG269

相关文章

- Pycharm配置(1)——解释器(interpreter)「建议收藏」

- 【分享】在集简云上架应用如何配置一个执行动作?

- LDAP客户端认证配置与应用接入

- 安装生物软件和配置数据库

- 小程序功能页面配置怎么填_设置企业级应用在哪

- 软件测试|SonarQube 安装、配置及 JaCoCo、Maven 集成

- 【错误记录】NDK 报错 java.lang.UnsatisfiedLinkError 的一种处理方案 ( 主应用与依赖库 Module 的 CPU 架构配置不匹配导致 )

- 【错误记录】Android 应用配置第三方 so 动态库 ( /data/app/comxxx==/base.apk/lib/arm64-v8a]couldn‘t find “libx.so“ )

- 【Android Gradle 插件】Gradle 基础配置 ⑥ ( Android工程 Gradle 常用命令 | gradlew 可执行文件 | 查看帮助文档 | 查看应用依赖 )

- Spring Boot 2.x基础教程:配置元数据的应用

- Spring Batch 配置方式XML

- Linux网卡聚合:构建牢固的网络性能(linux网卡聚合配置)

- MySQL Variables thread_pool_prio_kickup_timer 数据库 参数变量解释及正确配置使用

- 加密MySQL数据库配置SALT加密安全(mysqlsalt)

- Linux下Qt4应用的安装与配置(qt4linux安装)

- 使用Linux安装和配置Sogo,高效管理您的邮件和日历(linuxsogo)

- Oracle监听器配置指南:简明扼要(怎么配置oracle监听)

- 探讨Linux操作系统中网段ip的应用及配置技巧(linux网段ip)

- Redis远程访问:简单配置实现(redis 远程访问设置)

- 轻松搞定Redis安装配置,提升Web应用性能!(redis在安装配置)

- 应用Redis配置提升应用效能(应用配置redis)

- 根据Redis应用,搭建最佳服务器配置(redis需要多少机器)

- 应用中的应用Redis简化一层应用配置与使用(redis配置在一层)

- Oracle11配置简易教程(oracle11配置教程)

- Windows配置Apache以便在浏览器中运行Pythonscript的CGI模式