FPGA - 7系列 FPGA内部结构之Memory Resources -01- Block RAM资源

前言

7系列的FPGA内部存储资源主要包括RAM、FIFO这些部分,本文主要节选自UG473第一章,介绍了7系列的FPGA内部的Block RAM资源。

文章目录

- 前言

- Block RAM 资源概述

- Block RAM 简介

- 同步双端口和单端口RAM

- 7 系列器件中的其他 Block RAM 特性

- Block RAM 库原语

- Block RAM 端口信号介绍

- Block RAM 地址映射

- Block RAM 属性

- 内容初始化 - INIT_xx

- 内容初始化 - INITP_xx

- 输出锁存器初始化 - INIT(INIT_A 或 INIT_B)

- 输出锁存器/寄存器同步设置/复位 (SRVAL_[A|B])

- 复位或 CE 优先级 - RSTREG_PRIORITY_[A|B]

- 可选输出寄存器开/关开关 - DO[A|B]_REG

- 扩展模式地址决定因素 - RAM_EXTENSION_[A|B]

- 读取宽度 - READ_WIDTH_[A|B]

- 写入宽度 - WRITE_WIDTH_[A|B]

- 模式选择 - RAM_MODE

- 写入模式 - WRITE_MODE_[A|B]

- RDADDR_COLLISION_HWCONFIG

- SIM_COLLISION_CHECK

- INIT_FILE

- SIM_DEVICE

- Block RAM 位置约束

- VHDL 或 Verilog 代码中的 Block RAM 初始化

- 其他 RAMB18E1 和 RAMB36E1 原语设计注意事项

- Block RAM 应用

- Block RAM 时序模型

- reference

Block RAM 资源概述

Xilinx 7 系列 FPGA 中的 Block RAM 可存储高达 36 Kb 的数据,可配置为两个独立的 18 Kb RAM 或一个 36 Kb RAM。 每个 36 Kb 块 RAM 可配置为 64K x 1(与相邻的 36 Kb 块 RAM 级联时)、32K x 1、16K x 2、8K x 4、4K x 9、2K x 18、1K x 36 或 512 x 72,简单双端口模式。

每个 18 Kb 块 RAM 可以在简单双端口模式下配置为 16K x 1、8K x2、4K x 4、2K x 9、1K x 18 或 512 x 36。

与 Virtex-6 FPGA 块 RAM 类似,写入和读取是同步操作; 这两个端口是对称且完全独立的,仅共享存储的数据。 每个端口都可以配置为其中一个可用宽度,独立于另一个端口。 此外,每个端口的读端口宽度可以与写端口宽度不同。 内存内容可以通过配置比特流初始化或清除。 在写操作期间,内存可以设置为保持数据输出保持不变,反映正在写入的新数据或现在正在覆盖的先前数据。

7 系列 FPGA 块 RAM 特性包括:

- 每块存储器的存储能力,其中每个块 RAM 可以存储高达 36 Kbits 的数据。

- 支持两个独立的 18Kb 块或单个 36Kb 块 RAM。

- 每个 36Kb 块 RAM 可设置为简单双端口 (SDP) 模式,将块 RAM 的数据宽度加倍至 72 位。 18Kb 块 RAM 也可以设置为简单的双端口模式,将数据宽度加倍至 36 位。 简单双端口模式定义为具有一个只读端口和一个具有独立时钟的只写端口。

- 简单的双端口RAM 支持一侧的固定宽度数据端口设置和另一侧的可变数据端口宽度设置。

- 两个相邻的 Block RAM 可以组合成一个更深的 64K x 1 存储器,无需任何外部逻辑。

- 每个 36 Kb 块 RAM 或 36 Kb FIFO 提供一个 64 位纠错编码块。 提供单独的编码/解码功能。 在 ECC 模式下注入错误的能力。

- Block RAM 输出的锁存模式和寄存器模式都可以将输出同步设置/复位为初始值。

- 独立的同步置位/复位引脚可独立控制块RAM 中可选输出寄存器和输出锁存级的置位/复位。

- 将 Block RAM 配置为同步 FIFO 以消除标志延迟不确定性的属性。

- 7 系列 FPGA 中的 FULL 标志被断言,没有任何延迟。

- 18、36 或72 位宽的块RAM 端口可以有一个单独的每个字节的写使能。此功能在连接微处理器时很受欢迎。

- 每个块 RAM 包含可选的地址排序和控制电路,可作为内置双时钟 FIFO 存储器运行。 在 7 系列架构中,Block RAM 可配置为 18 Kb 或 36 Kb FIFO。

- 所有输入都注册到端口时钟,并具有设置时钟时序规范。

- 所有输出都具有读取功能或read-during-write 功能,具体取决于写使能(WE) 引脚的状态。 输出在时钟到输出时序间隔之后可用。 read-during-write 输出具有以下三种操作模式之一:WRITE_FIRST、READ_FIRST 和 NO_CHANGE。

- 写操作需要一个时钟沿。

- 读操作需要一个时钟沿。

- 所有输出端口都被锁存或寄存(可选)。 直到端口执行另一个读或写操作,输出端口的状态才会改变。 默认 Block RAM 输出为锁存模式。

- 输出数据路径有一个可选的内部流水线寄存器。 强烈建议使用寄存器模式。 这允许更高的时钟频率; 但是,它增加了一个时钟周期延迟。

7 系列 FPGA 块 RAM 使用规则包括:

- 当启用 ECC 解码器 (EN_ECC_READ = TRUE) 时,不能使用同步设置/复位 (RSTRAM) 端口。

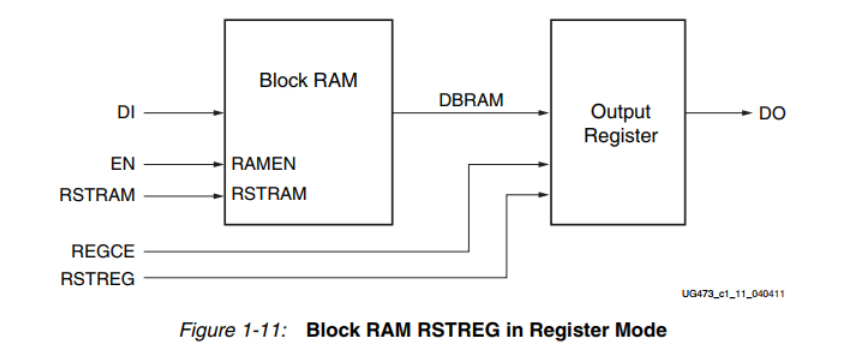

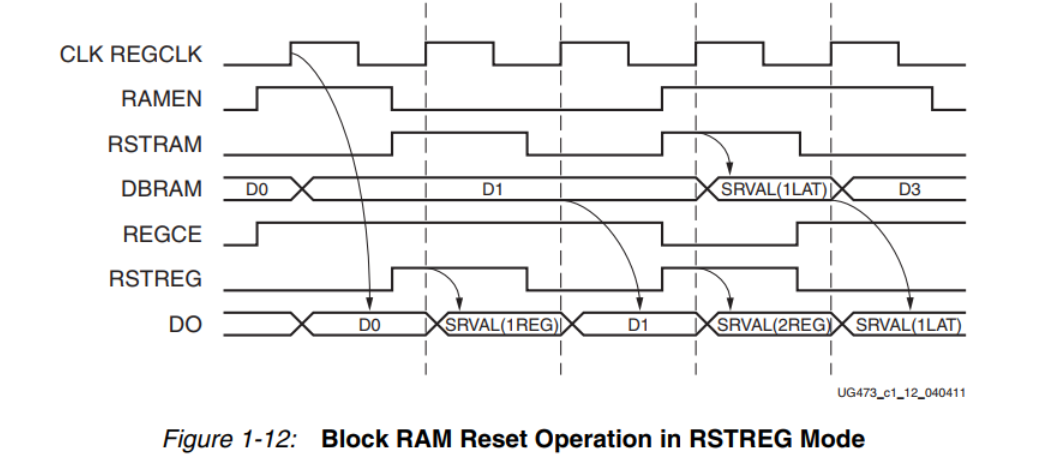

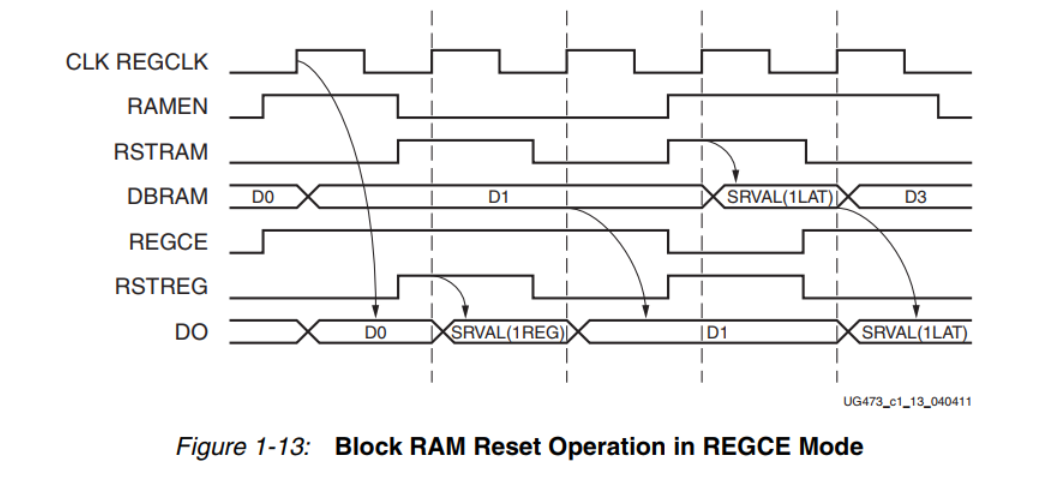

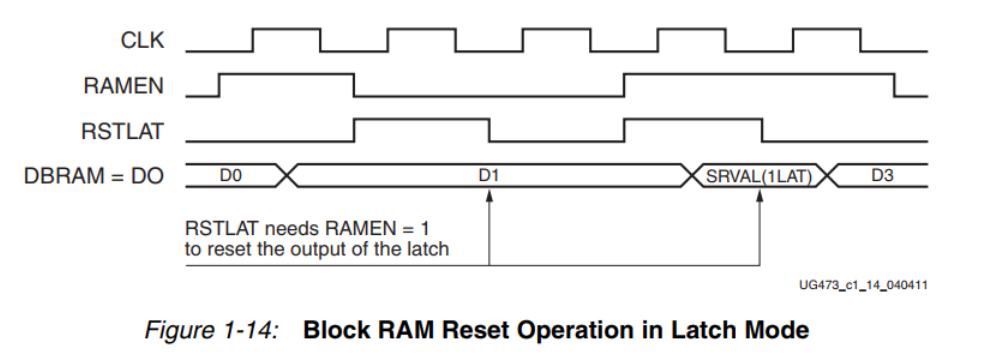

- 当 DO_REG = 1 时,使用 RSTREG 设置或复位 Block RAM 同步输出寄存器(可选) (SRVAL)。RSTREG_PRIORITY 属性确定 RSTREG 是否具有高于 REGCE 的优先级。 当 DO_REG 为 0 或 1 时,使用 RSTRAM 设置或复位同步输出锁存器 (SRVAL)。

- 不得违反 Block RAM 地址和写使能引脚的建立时间。违反地址设置时间(即使写使能为低电平)可能会损坏 Block RAM 的数据内容。

- Block RAM 寄存器模式RSTREG 要求REGCE = 1 来复位输出DO 寄存器值; 如果 RSTREG_PRIORITY 设置为 REGCE。 Block RAM 阵列数据输出锁存器在此模式下不会复位。 Block RAM 锁存模式 RSTRAM 需要 Block RAM 使能 EN = 1 来复位输出 DO 锁存值。

- 有两个 Block RAM 原语:RAMB36E1 和 RAMB18E1。 RAM_MODE 属性确定 Block RAM 的模式,即 SDP 模式或真双端口 (TDP) 模式。

- 当使用特定的块 RAM 原语时,可以选择不同的读取和写入端口宽度。 奇偶校验位仅适用于 x9、x18 和 x36 端口宽度。 当读取宽度为 x1、x2 或 x4 时,不应使用奇偶校验位。 如果读取宽度为 x1、x2 或 x4,则有效写入宽度为 x1、x2、x4、x8、x16 或 x32。

同样,当写入宽度为 x1、x2 或 x4 时,实际可用的读取宽度为 x1、x2、x4、x8、x16 或 x32,即使原始属性设置为 1、2、4、9、18、 或 36等。 下表显示了一些可能的情况。

| Primitive | Settings | Settings | Effective Read Width | Effective Write Width |

|---|---|---|---|---|

| Read Width | Write Width | |||

| RAMB18E1 | 1, 2, or 4 | 9 or 18 | Same as setting | 8 or 16 |

| RAMB18E1 | 9 or 18 | 1, 2, or 4 | 8 or 16 | Same as setting |

| RAMB18E1 | 1, 2, or 4 | 1, 2, or 4 | Same as setting | Same as setting |

| RAMB18E1 | 9 or 18 | 9 or 18 | Same as setting | Same as setting |

| RAMB36E1 | 1, 2, or 4 | 9, 18, or 36 | Same as setting | 8, 16, or 32 |

| RAMB36E1 | 9, 18, or 36 | 1, 2, or 4 | 8, 16, or 32 | Same as setting |

| RAMB36E1 | 1, 2, or 4 | 1, 2, or 4 | Same as setting | Same as setting |

| RAMB36E1 | 9, 18, or 36 | 9, 18, or 36 | Same as setting | Same as setting |

RAMB36E1 中的A15 引脚只能用于级联。 在所有其他情况下,A15 应保持未连接或连接为高电平。

由异步复位引起的EN 信号的异步断言或取消断言可能会违反EN 信号的建立/保持时间。在这种情况下,第一次读取或写入操作不会产生预期的结果。 如果无法避免 EN 的异步声明或取消声明,请在异步 RESET 声明和取消声明期间保持 EN 取消声明,或者在有效数据周期发生之前在声明 EN 之后插入读取或写入周期。 如果 PLL 或 MMCM LOCKED 信号丢失,或自由运行时钟停止,则立即将 EN 置低。

当一个端口宽度小于 9 而另一个端口宽度为 9 或更大时,不要使用奇偶校验位 DIP/DOP。

Block RAM 简介

除了分布式 RAM 和高速 SelectIO存储器接口之外,7 系列器件还具有大量 36 Kb Block RAM。 每个 36 Kb 块 RAM 包含两个独立控制的 18 Kb RAM。 Block RAM 是按列放置的,7 系列器件在下表中列出了 Block RAM 资源的总数。 36 Kb 块可级联,以实现更深、更宽的内存实现,同时将时序损失降至最低。

嵌入式双端口或单端口 RAM 模块、ROM 模块、同步 FIFO 和数据宽度转换器使用 Xilinx CORE Generator 块存储器模块实现。 可以使用 CORE Generator FIFO Generator 模块生成双时钟 FIFO。 同步或异步(双时钟)FIFO 实现不需要额外的 CLB 资源用于 FIFO 控制逻辑,因为它使用专用硬件资源。

同步双端口和单端口RAM

数据流

真双端口 36 Kb block RAM 双端口存储器由一个 36 Kb 存储区域和两个完全独立的访问端口 A 和 B 组成。同样,每个 18 Kb block RAM 双端口存储区由一个 18 Kb 的存储区和两个完全独立的访问端口 A 和 B 组成。结构完全对称,两个端口可以互换。 数据可以写入任一端口或两个端口,也可以从任一端口或两个端口读取。 每个写操作都是同步的,每个端口都有自己的地址、数据输入、数据输出、时钟、时钟使能和写使能。 读取和写入操作是同步的并且需要时钟沿。没有专门的监视器来仲裁相同地址对两个端口的影响。 两个时钟的时间由您决定。 对同一位置的同时写入冲突不会导致任何物理损坏,但会导致数据不确定性。

下图说明了 RAMB36 的双端口数据流。

下文列出了端口的功能和说明。

| Port Function | Description |

|---|---|

| DI[A|B] | 数据输入总线 |

| DIP[A|B] | 数据输入奇偶校验总线。 可用于附加数据输入。 |

| ADDR[A|B] | 地址总线 |

| WE[A|B] | 字节宽写使能 |

| EN[A|B] | 当不使能时,没有数据写入 Block RAM,输出总线保持之前的状态。 |

| RSTREG[A|B] | 同步设置/复位输出寄存器 (DO_REG = 1)。 RSTREG_PRIORITY 属性决定了 REGCE 的优先级。 |

| RSTRAM[A|B] | 同步设置/复位输出数据锁存器。 |

| CLK[A|B] | 时钟输入 |

| DO[A|B] | 数据输出总线 |

| DOP[A|B] | 数据输出奇偶校验总线。 可用于附加数据输出。 |

| REGCE[A|B] | 输出寄存器时钟使能。 |

| CASCADEIN[A|B] | 64K x 1 模式的级联输入。 |

| CASCADEOUT[A|B] | 64K x 1 模式的级联输出。 |

读操作

在锁存模式下,读操作使用一个时钟沿。 读取地址锁存在读取端口上,存储的数据在 RAM 访问时间后加载到输出锁存器中。

使用输出寄存器时,读取操作需要一个额外的延迟周期。

写操作

写操作是单时钟沿操作。 写地址寄存在写端口上,输入的数据存储在内存中。

写入模式

写入模式的三种设置决定了写入时钟沿后输出锁存器上可用数据的行为:WRITE_FIRST、READ_FIRST 和 NO_CHANGE。

写入模式选择由配置设置。 可以为每个端口单独选择写入模式属性。 默认模式是 WRITE_FIRST。 WRITE_FIRST 将新写入的数据输出到输出总线。 READ_FIRST 在写入新数据时输出先前存储的数据。 NO_CHANGE 维护先前由读取操作生成的输出。

WRITE_FIRST 或Transparent 模式(默认)

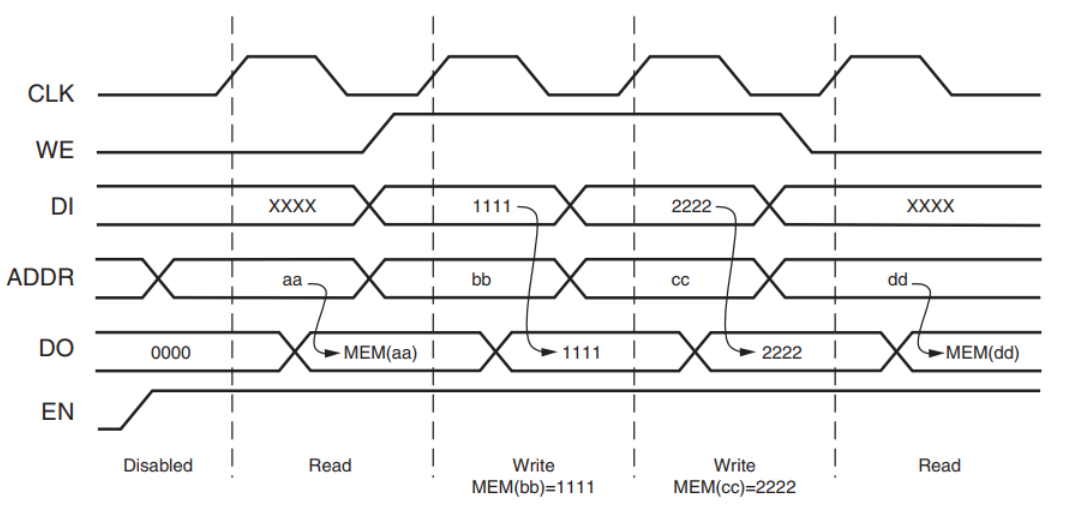

在 WRITE_FIRST 模式下,输入数据同时写入内存和存储在数据输出中(透明写入),如图 1-2 所示。 当不使用可选输出流水线寄存器时,这些波形对应于锁存模式。

READ_FIRST 或 Read-Before-Write 模式

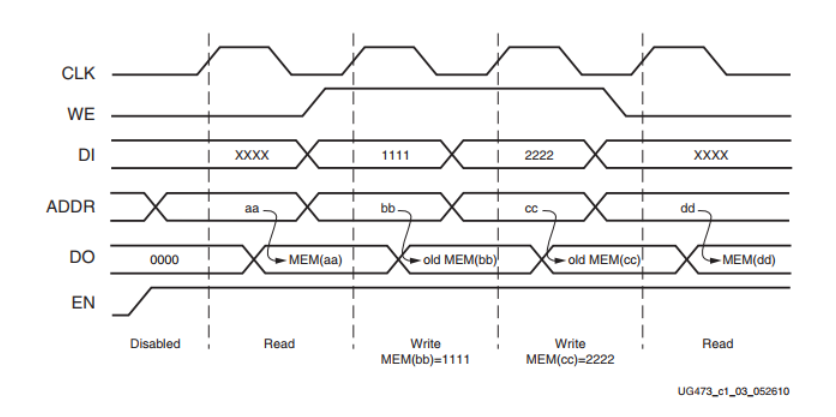

在 READ_FIRST 模式下,先前存储在写地址的数据出现在输出锁存器上,而输入数据存储在内存中(写前读)。 下图中的波形对应于不使用可选输出流水线寄存器时的锁存模式。

NO_CHANGE 模式

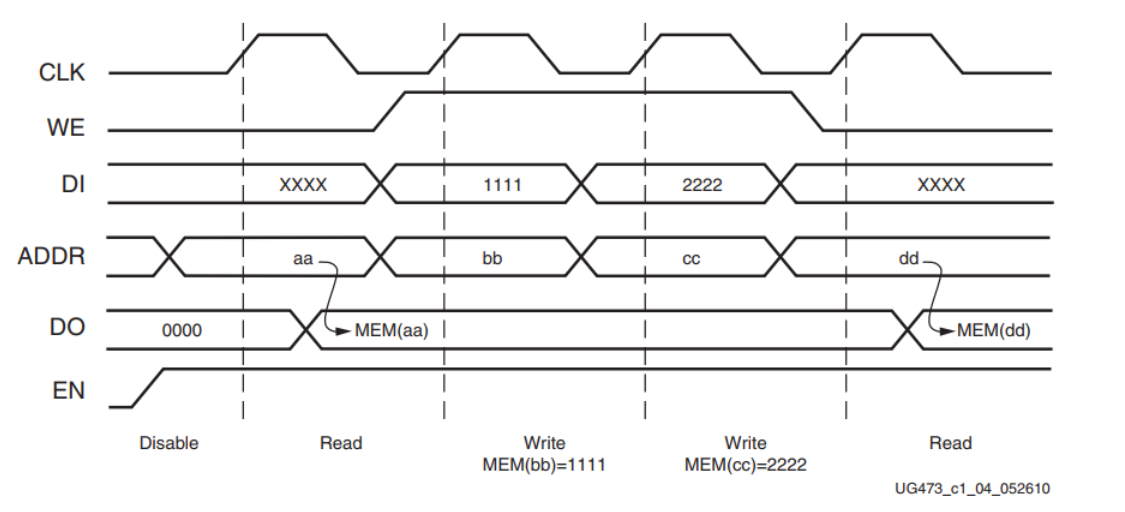

在 NO_CHANGE 模式下,输出锁存器在写操作期间保持不变。

如下图所示,数据输出仍然是最后读取的数据,不受同一端口上的写操作的影响。 这些波形对应于锁存模式时可选不使用输出流水线寄存器。 这种模式是最省电的。 此模式在 SDP 模式中不可用,因为它的行为与 WRITE_FIRST 模式相同。

避免冲突

7 系列 FPGA 块 RAM 是真双端口 RAM,其中两个端口都可以随时访问任何内存位置。 从两个端口访问相同的内存位置时,可能会发生地址冲突。 地址冲突是指两个 Block RAM 端口在同一时钟周期内访问同一地址位置。 有两种基本时钟类型设置,通用时钟和独立时钟。 公共(同步)时钟由公共时钟缓冲器驱动器驱动。 所有其他 CLKA 和 CLKB 连接都被视为独立(异步)时钟。 如果预计或可能不会发生地址冲突(SDP 配置)以节省功耗,则推荐的写入模式为 NO_CHANGE。

使用 READ_FIRST 模式比 NO_CHANGE 有 15% 的功率损失,并且只应在必要时用于功能或地址冲突缓解。

- 当两个端口都在读取时,操作成功完成。

- 当两个端口写入不同的数据时,内存位置将写入不确定的数据。

- 当一个端口在写而另一个端口在读时,写总是成功的,但最终的读内存值可能会有所不同。

7 系列器件中的其他 Block RAM 特性

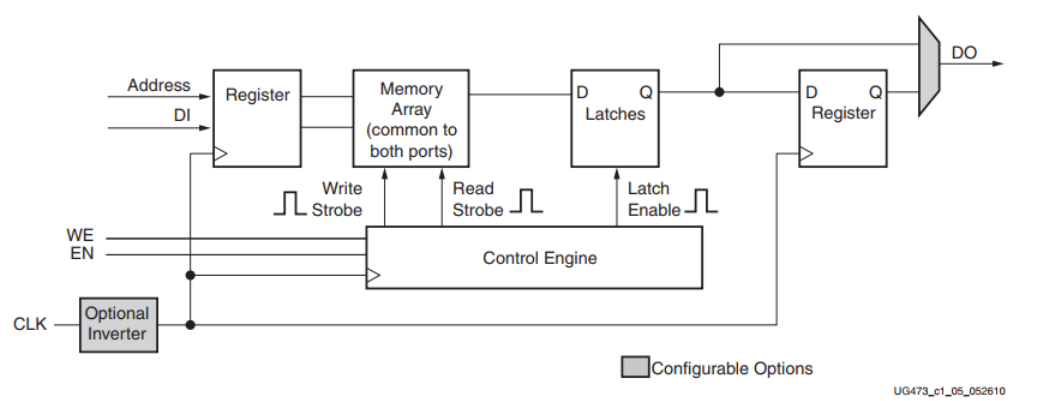

可选输出寄存器

可选输出寄存器通过消除 CLB 触发器的布线延迟以进行流水线操作,从而提高了设计性能。 为这些输出寄存器提供了独立的时钟和时钟使能输入。 因此,输出数据寄存器的值独立于输入寄存器操作。 下图显示了可选的输出寄存器。

独立的读写端口宽度选择

每个 Block RAM 端口都可以控制数据宽度和地址深度(纵横比)。7 系列 FPGA 中真双端口 Block RAM 将这种灵活性扩展到了读写,其中每个单独的端口都可以配置不同的数据位宽度。 例如,端口 A 可以具有 36 位读取宽度和 9 位写入宽度,端口 B 可以具有 18 位读取宽度和 36 位写入宽度。

如果读端口宽度与写端口宽度不同,并且配置为 WRITE_FIRST 模式,则 DO 显示所有启用的写字节的有效新数据。 DO 端口为所有未启用的字节输出存储在内存中的原始数据。

独立的读写端口宽度选择提高了在块 RAM 中实现内容可寻址存储器 (CAM) 的效率。 该选项适用于所有 7 系列 FPGA 真正的双端口 RAM 端口大小和模式。

简单双端口RAM

每个 18 Kb 块和 36 Kb 块也可以配置为简单双端口 RAM 模式。在此模式下,对于 18 Kb 块 RAM,块 RAM 端口宽度加倍至 36 位,对于 36 Kb 块 RAM 则为 72 位。 在简单双端口模式下,可以同时进行独立的读取和写入操作,其中端口 A 指定为读取端口,端口 B 指定为写入端口。 当 Read 和 Write 端口同时访问相同的数据位置时,它被视为冲突,与真正的双端口模式下的端口冲突相同。

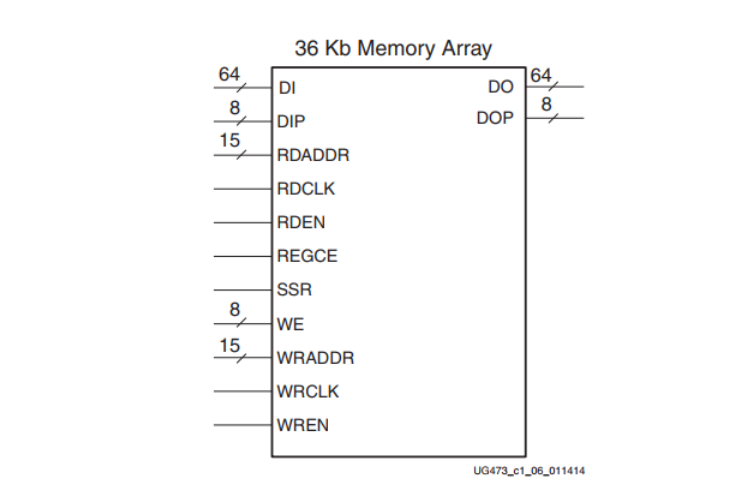

简单双端口 Block RAM 模式支持通过配置端口回读。 7 系列 FPGA 在 SDP 中支持这些模式(READ_FIRST、WRITE_FIRST)。下图显示了 SDP 模式下 RAMB36 的简单双端口数据流。

Block RAM 原语端口名称可以与端口功能名称不同。

| Port Function | Description |

|---|---|

| DO | 数据输出总线 |

| DOP | 数据输出奇偶校验总线 |

| DI | 数据输入总线 |

| DIP | 数据输入奇偶校验总线 |

| RDADDR | 读取数据地址总线 |

| RDCLK | 读数据时钟 |

| RDEN | 读取端口启用 |

| REGCE | 输出寄存器时钟使能 |

| SBITERR | 单位错误状态 |

| DBITERR | 双位错误状态 |

| ECCPARITY | ECC 编码器输出总线 |

| SSR | 输出寄存器或锁存器的同步设置或复位 |

| WE | 字节宽写使能 |

| WRADDR | 写数据地址总线 |

| WRCLK | 写数据时钟 |

| WREN | 写端口使能 |

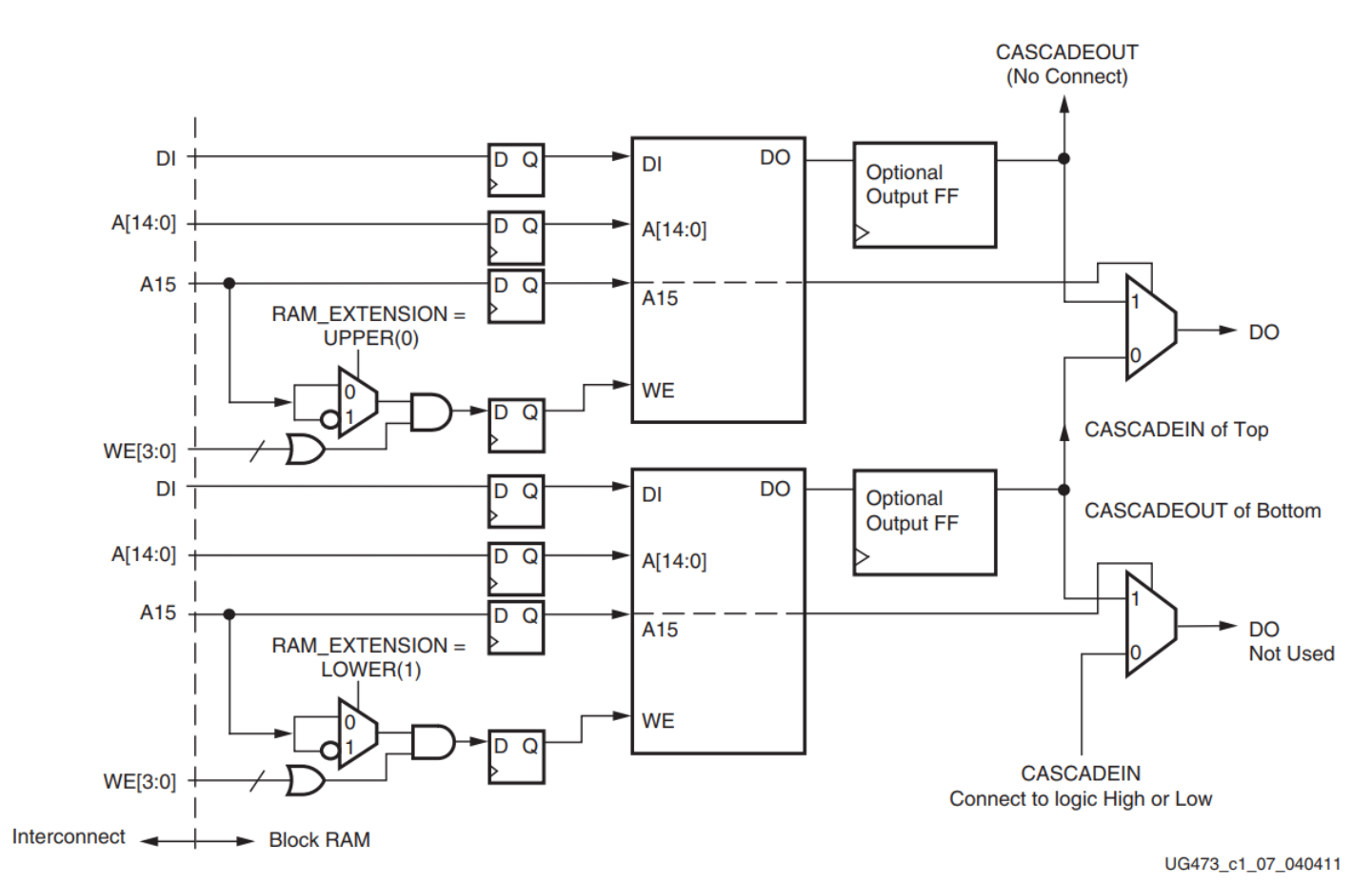

级联RAM

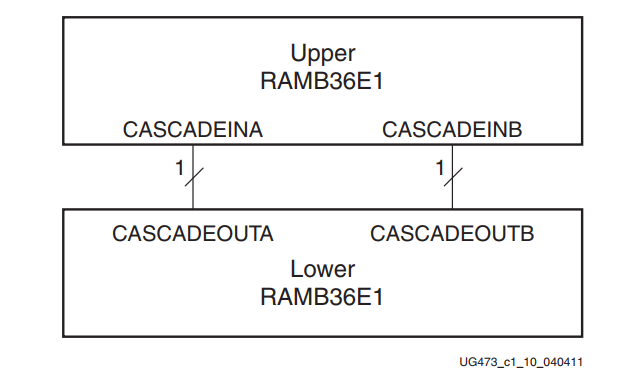

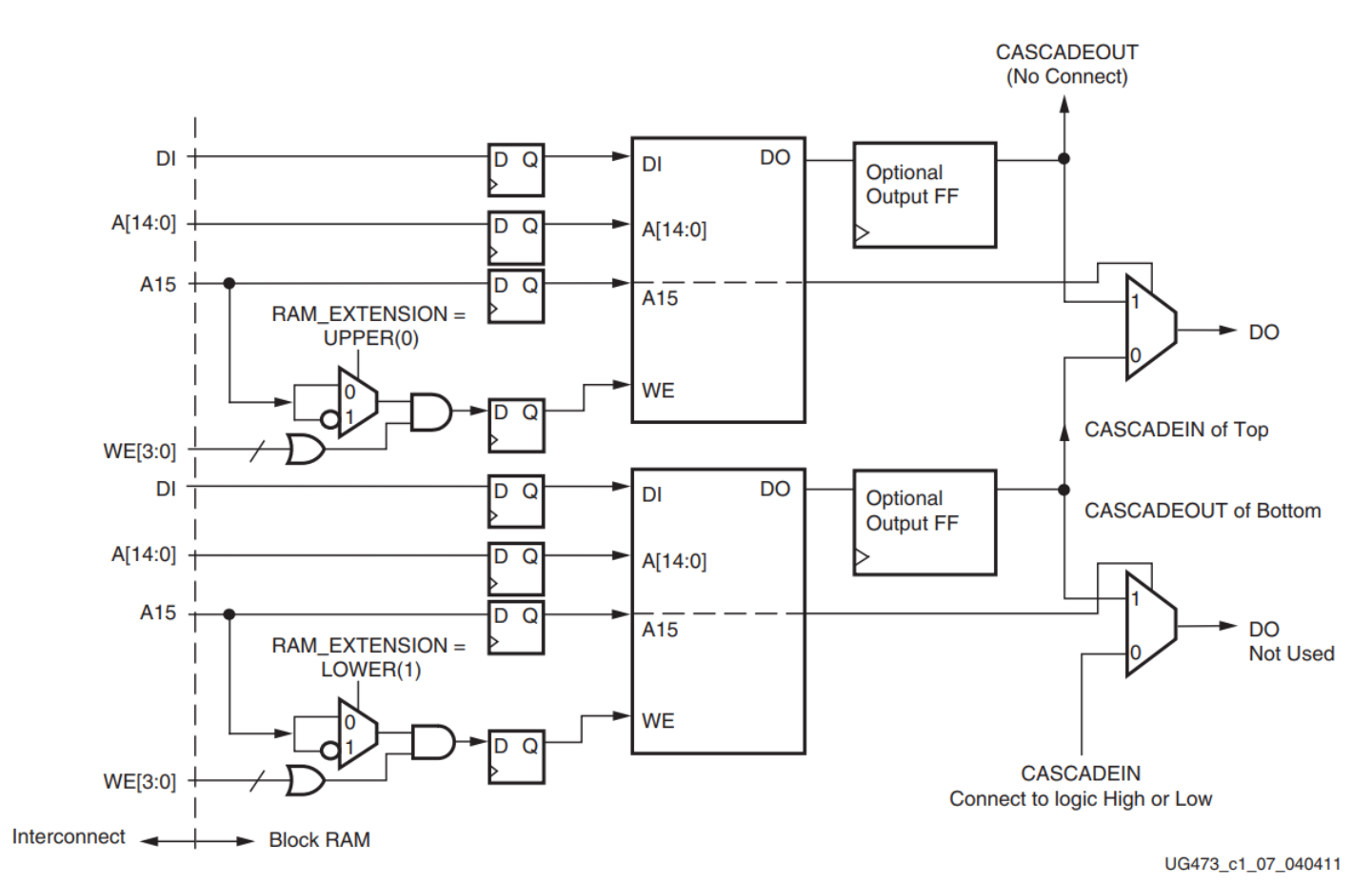

在 7 系列 FPGA 块 RAM 架构中,两个 32K x 1 RAM 可以组合成一个 64K x 1 RAM,而无需使用本地互连或额外的 CLB 逻辑资源。 任何两个相邻的块 RAM 可以级联以生成 64K x 1 块 RAM。 通过级联两个 Block RAM 来增加 Block RAM 的深度仅在 64K x 1 模式下可用。 下图显示了在 Cascadable 模式下连接了适当端口的 Block RAM。

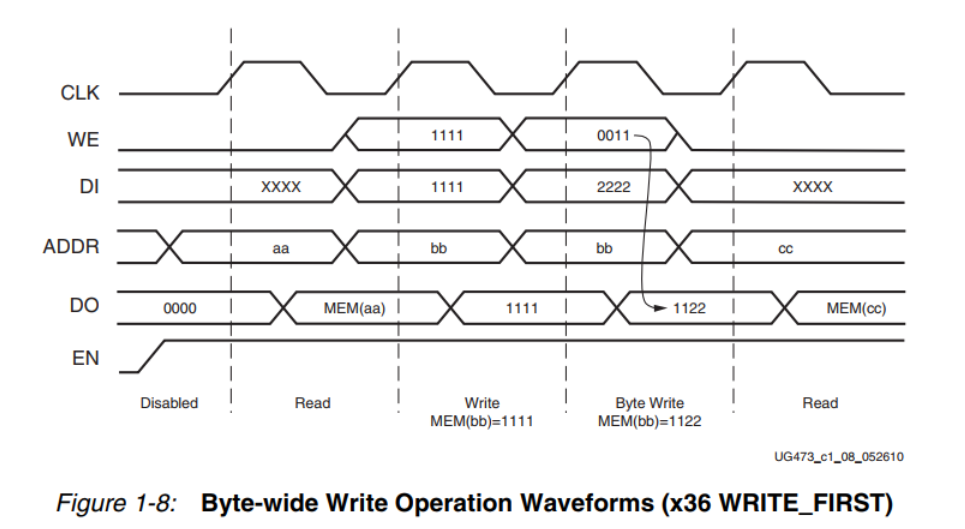

字节宽写使能

Block RAM 的字节宽写使能特性允许写入输入数据的 8 位(一个字节)部分。RAMB36E1 真双端口 RAM 有四个独立的字节宽写使能输入。 在简单双端口模式下(RAMB36E1 在 SDP 模式下)有 8 个独立的字节宽写使能输入到 Block RAM。

下表总结了 36Kb 和 18Kb 块 RAM 的字节宽写使能。

| Primitive | Maximum Bit Width | Number of Byte-Wide Write Enables |

|---|---|---|

| RAMB36E1 TDP mode (真双口模式) | 36 | 4 |

| RAMB36E1 SDP mode (伪双口模式) | 72 | 8 |

| RAMB18E1 TDP mode (真双口模式) | 18 | 2 |

| RAMB18E1 SDP mode (伪双口模式) | 36 | 4 |

每个字节范围的写使能与一个字节的输入数据和一个奇偶校验位相关联。 所有字节宽度的写使能输入必须在所有数据宽度配置中驱动。 当使用块 RAM 与微处理器接口时,此功能很有用。 在双时钟 FIFO 或 ECC 模式下,字节宽写使能不可用。 下图显示了 RAMB36E1 的字节宽写使能时序图。

当 RAMB36E1 配置为 36 位或 18 位宽数据路径时,任何端口都可以限制写入数据字中的指定字节位置。 如果配置为 READ_FIRST 模式,DO 总线会显示整个寻址字的先前内容。在 WRITE_FIRST 模式下,DO 显示新写入的启用字节和未写入字节的初始内存内容的组合。

Block RAM 纠错码

36 Kb Block RAM 的 Block RAM 和 FIFO 实现都支持 64 位纠错码 (ECC) 实现。 该代码用于检测读出的 Block RAM 数据中的单位和双位错误。 然后在输出数据中纠正单位错误。

未使用 Block RAM 的电源门控

7 系列器件以 18Kb 的粒度关闭未使用/未实例化的 Block RAM 块。 在设计中未例化的每个 18Kb 块上启用电源门控以节省功耗。 电源门控 18Kb 块在配置期间未初始化,无法通过配置接口读回。 与以前的 FPGA 系列不同,配置和回读需要有效的比特流。 不再允许空白比特流。 通过禁用内部操作来防止对未实例化的块 RAM 的访问。

Block RAM 库原语

7 系列 FPGA 的 Block RAM 库原语 RAMB18E1 和 RAMB36E1 是所有 Block RAM 配置的基本构建块。 其他块 RAM 原语和宏基于这些原语。 某些 Block RAM 属性只能使用这些原语之一进行配置(例如,流水线寄存器、级联)。 请参见 Block RAM 属性部分。

输入和输出数据总线由 9 位宽度 (8 + 1)、18 位宽度 (16 + 2) 和 36 位宽度 (32 + 4) 配置的两条总线表示。 与每个字节相关的第九位可以存储奇偶校验/纠错位或用作附加数据位。 第 9 位不执行特定功能。 奇偶校验位的单独总线有助于某些设计。 但是,其他设计通过将常规数据总线与奇偶校验总线合并来安全地使用 9 位、18 位或 36 位总线。 所有位的读/写和存储操作都是相同的,包括奇偶校验位。

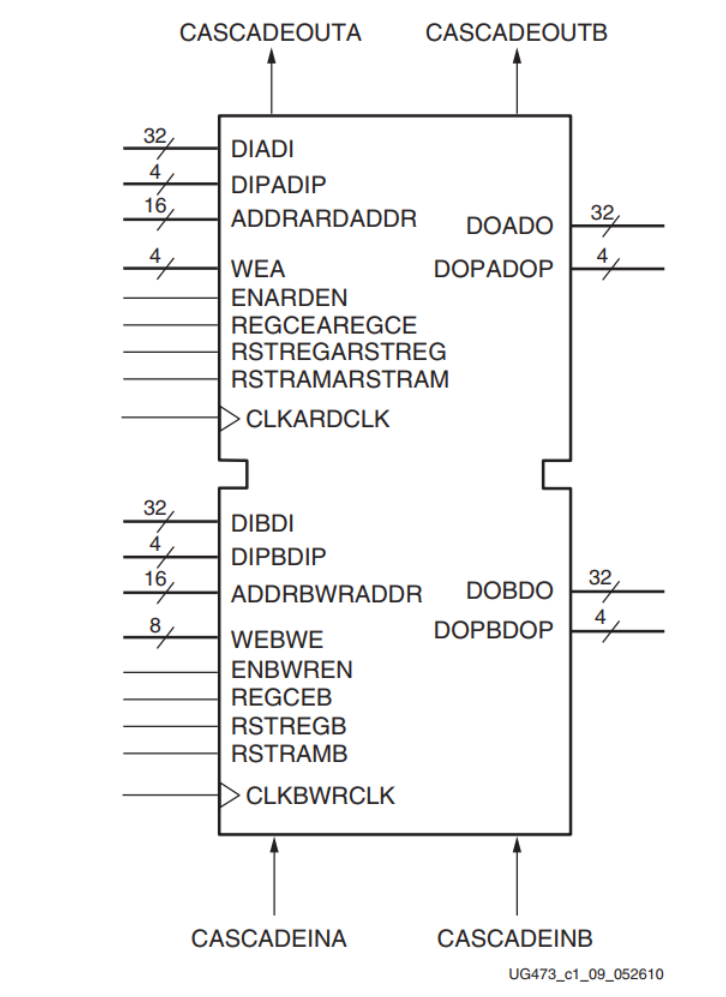

下图显示了 36 Kb 真双端口 Block RAM 原语 (RAMB36) 的所有 I/O 端口。

下表列出了这些原语。虽然在常规使用的时候都在IP中配置,不需要了解底层结构,但是工其事必先利器,了解底层可以更好地帮助我们进行更高层的开发。

| Primitive | Description |

|---|---|

| RAMB36E1 | 在 TDP 模式下,支持 x1、x2、x4、x9、x18、x36 的端口宽度 在 SDP 模式下,Read 或 Write 端口宽度为 x64 或 x72。 备用端口是 x1、x2、x4、x9、x18、x36、x72。 ECC模式下,支持64位ECC编解码 |

| RAMB18E1 | 在 TDP 模式下,支持 x1、x2、x4、x9、x18 的端口宽度 在 SDP 模式下,Read 或 Write 端口宽度为 x32 或 x36。 备用端口是 x1、x2、x4、x9、x18、x36。 |

| FIFO36E1 | 在 FIFO36 模式下,支持 x4、x9、x18、x36 的端口宽度 在 FIFO36_72 模式下,端口宽度为 x72,可选 ECC 支持。 |

| FIFO18E1 | FIFO18模式下,支持x4、x9、x18的端口宽度 在FIFO18_36模式下,端口宽度为x36 |

源语的端口

下面介绍各个源语的端口说明。

RAMB36E1

RAMB36E1的端口名称和说明如下所示:

| Port Name | Description |

|---|---|

| DIADI[31:0] | 由 ADDRARDADDR 寻址的端口 A 数据输入。 |

| DIPADIP[3:0] | 由 ADDRARDADDR 寻址的端口 A 数据奇偶校验输入。 |

| DIBDI[31:0] | 由 ADDRBWRADDR 寻址的端口 B 数据输入。 |

| DIPBDIP[3:0] | 由 ADDRBWRADDR 寻址的端口 B 数据奇偶校验输入。 |

| ADDRARDADDR [15:0] | 端口 A 地址输入总线。 在 RAM_MODE = SDP 中,这是 RDADDR 总线。 |

| ADDRBWRADDR[15:0] | 端口 B 地址输入总线。 在 RAM_MODE = SDP 中,这是 WRADDR 总线。 |

| WEA[3:0] | 端口 A 字节宽的写使能。 在 RAM_MODE = SDP 中不使用。 |

| WEBWE[7:0] | 端口 B 字节宽的写使能。 在 RAM_MODE = SDP 中,这是字节范围的写使能。 |

| ENARDEN | 端口 A 启用。 在 RAM_MODE = SDP 中,这是 RDEN。 |

| ENBWREN | 端口 B 启用。 在 RAM_MODE = SDP 中,这是 WREN。 |

| RSTREGARSTREG | 同步输出寄存器设置/复位由 SRVAL_A (DOA_REG = 1) 初始化。 RSTREG_PRIORITY_A 确定 REGCE 的优先级。 在 RAM_MODE = SDP 中,这是 RSTREG。 |

| RSTREGB | 同步输出寄存器设置/复位由 SRVAL_B (DOB_REG = 1) 初始化。 RSTREG_PRIORITY_B 确定 REGCE 的优先级。 |

| RSTRAMARSTRAM | 同步输出锁存器设置/复位由 SRVAL_A (DOA_REG = 0) 初始化。 在 RAM_MODE = SDP 中,这是 RSTRAM。 |

| RSTRAMB | 同步输出锁存器设置/复位由 SRVAL_B (DOB_REG = 0) 初始化。 |

| CLKARDCLK | 端口 A 时钟输入。 在 RAM_MODE = SDP 中,这是 RDCLK。 |

| CLKBWRCLK | 端口 B 时钟输入。 在 RAM_MODE = SDP 中,这是 WRCLK。 |

| REGCEAREGCE | 端口 A 输出寄存器时钟使能 (DOA_REG = 1)。 在 RAM_MODE = SDP 中,这是 REGCE。 |

| REGCEB | 端口 B 输出寄存器时钟使能 (DOB_REG = 1)。 |

| CASCADEINA | 端口 A 级联输入。 仅用于 RAM_MODE = TDP。 |

| CASCADEINB | 端口 B 级联输入。 仅用于 RAM_MODE = TDP。 |

| CASCADEOUTA | 端口 A 级联输出。 仅用于 RAM_MODE = TDP。 |

| CASCADEOUTB | 端口 B 级联输出。 仅用于 RAM_MODE = TDP。 |

| DOADO[31:0] | 由 ADDRARDADDR 寻址的端口 A 数据输出总线。 |

| DOPADOP[3:0] | 由 ADDRARDADDR 寻址的端口 A 奇偶校验输出总线。 |

| DOBDO[31:0] | 由 ADDRBWRADDR 寻址的端口 B 数据输出总线。 |

| DOPBDOP[3:0] | 端口 B 奇偶校验输出总线由 ADDRBWRADDR 寻址。 |

RAMB18E1

RAMB18E1的端口名称和说明如下所示:

| Port Name | Description |

|---|---|

| DIADI[15:0] | 由 ADDRARDADDR 寻址的端口 A 数据输入。 |

| DIPADIP[1:0] | 由 ADDRARDADDR 寻址的端口 A 数据输入。 |

| DIBDI[15:0] | 由 ADDRBWRADDR 寻址的端口 B 数据输入。 |

| DIPBDIP[1:0] | 由 ADDRBWRADDR 寻址的端口 B 数据奇偶校验输入。 |

| ADDRARDADDR[13:0] | 端口 A 地址输入总线。 在 RAM_MODE = SDP 中,这是 RDADDR 总线。 |

| ADDRBWRADDR[13:0] | 端口 B 地址输入总线。 在 RAM_MODE = SDP 中,这是 WRADDR 总线。 |

| WEA[1:0] | 端口 A 字节宽的写使能。 在 RAM_MODE = SDP 中不使用。 |

| WEBWE[3:0] | 端口 B 字节宽写使能 (WEBWE[1:0])。 在 RAM_MODE = SDP 中,这是字节范围的写使能。 |

| ENARDEN | 端口 A 启用。 在 RAM_MODE = SDP 中,这是 RDEN。 |

| ENBWREN | 端口 B 启用。 在 RAM_MODE = SDP 中,这是 WREN。 |

| RSTREGARSTREG | 同步输出寄存器设置/复位由 SRVAL_A (DOA_REG = 1) 初始化。 RSTREG_PRIORITY_A 确定 REGCE 的优先级。 在 RAM_MODE = SDP 中,这是 RSTREG。 |

| RSTREGB | 同步输出寄存器设置/复位由 SRVAL_B (DOB_REG = 1) 初始化。 RSTREG_PRIORITY_B 确定 REGCE 的优先级。 |

| RSTRAMARSTRAM | 同步输出锁存器设置/复位由 SRVAL_A (DOA_REG = 0) 初始化。 在 RAM_MODE = SDP 中,这是 RSTRAM。 |

| RSTRAMB | 同步输出锁存器设置/复位由 SRVAL_B (DOB_REG = 0) 初始化。 |

| CLKARDCLK | 端口 A 时钟输入。 在 RAM_MODE = SDP 中,这是 RDCLK。 |

| CLKBWRCLK | 端口 B 时钟输入。 在 RAM_MODE = SDP 中,这是 WRCLK。 |

| REGCEAREGCE | 端口 A 输出寄存器时钟使能 (DOA_REG = 1)。 在 RAM_MODE = SDP 中,这是 REGCE。 |

| REGCEB | 端口 B 输出寄存器时钟使能 (DOB_REG = 1)。 |

| DOADO[15:0] | 由 ADDRARDADDR 寻址的端口 A 数据输出总线。 |

| DOPADOP[1:0] | 由 ADDRARDADDR 寻址的端口 A 奇偶校验输出总线。 |

| DOBDO[15:0] | 由 ADDRBWRADDR 寻址的端口 B 数据输出总线。 |

| DOPBDOP[1:0] | 端口 B 奇偶校验输出总线由 ADDRBWRADDR 寻址。 |

Block RAM 端口信号介绍

每个 Block RAM 端口在访问同一组 36 Kbit 存储单元时相互独立运行。

时钟 - CLKARDCLK 和 CLKBWRCLK

每个端口与独立的时钟引脚完全同步。 所有端口输入引脚的建立时间都以端口 CLK 引脚为参考。 输出数据总线有一个以 CLK 引脚为参考的时钟输出时间。 时钟极性是可配置的(默认为上升沿)。 在 SDP 模式下,CLKA 端口是 RDCLK,CLKB 端口是 WRCLK。

启用 - ENARDEN 和 ENBWREN

启用引脚影响端口的读、写和设置/复位功能。 具有非活动使能引脚的端口将输出引脚保持在先前的状态,并且不会将数据写入存储单元。 启用极性是可配置的(默认为高电平有效)。 在 SDP 模式下,ENA 端口为 RDEN,ENB 端口为 WREN。

字节宽写使能 - WEA 和 WEBWE

要将数据输入总线的内容写入寻址的存储器位置,EN 和 WE 都必须在有效时钟沿之前的设置时间内有效。 根据写入配置(WRITE_FIRST、READ_FIRST、NO_CHANGE)加载或不加载输出锁存器。 当 WE 无效且 EN 有效时,将发生读取操作,并且地址总线引用的存储单元的内容出现在数据输出总线上,而与写入模式属性无关。 写使能极性不可配置(高电平有效)。 在 SDP 模式下,WEBWE[7:0] 端口是字节写使能。 在 TDP 模式下,WEA[3:0] 和 WEB[3:0] 分别是端口 A 和端口 B 的字节写使能。

寄存器启用 - REGCEA、REGCE 和 REGCEB

寄存器启用引脚 (REGCE) 控制可选输出寄存器。 当 RAM 处于寄存器模式时,REGCE = 1 在时钟沿将输出寄存到寄存器中。 REGCE 的极性不可配置(高电平有效)。 在 SDP 模式下,REGCEA 端口是 REGCE。

置位/复位

RSTREGARSTREG、RSTREGB、RSTRAMARSTRAM 和 RSTRAMB

在锁存模式下,RSTRAM 引脚同步强制数据输出锁存器包含值 SRVAL。启用可选输出寄存器 (DO_REG = 1) 时,RSTREG 信号同步强制数据输出寄存器包含 SRVAL 值。 RSTREG 相对于 REGCE 的优先级是使用 RSTREG_PRIORITY 属性确定的。 数据输出锁存器或输出寄存器同步置为 0 或 1,包括奇偶校验位。 每个端口都有一个独立的 36 位 SRVAL[A|B] 属性。 此操作不会影响 RAM 存储单元,也不会干扰其他端口上的写操作。 两个信号的极性都是可配置的(默认为高电平有效)。 在 SDP 模式下,RSTREGA 端口是 RSTREG,而 RSTRAMA 端口是 RSTRAM。

地址总线 - ADDRARDADDR 和 ADDRBWRADDR

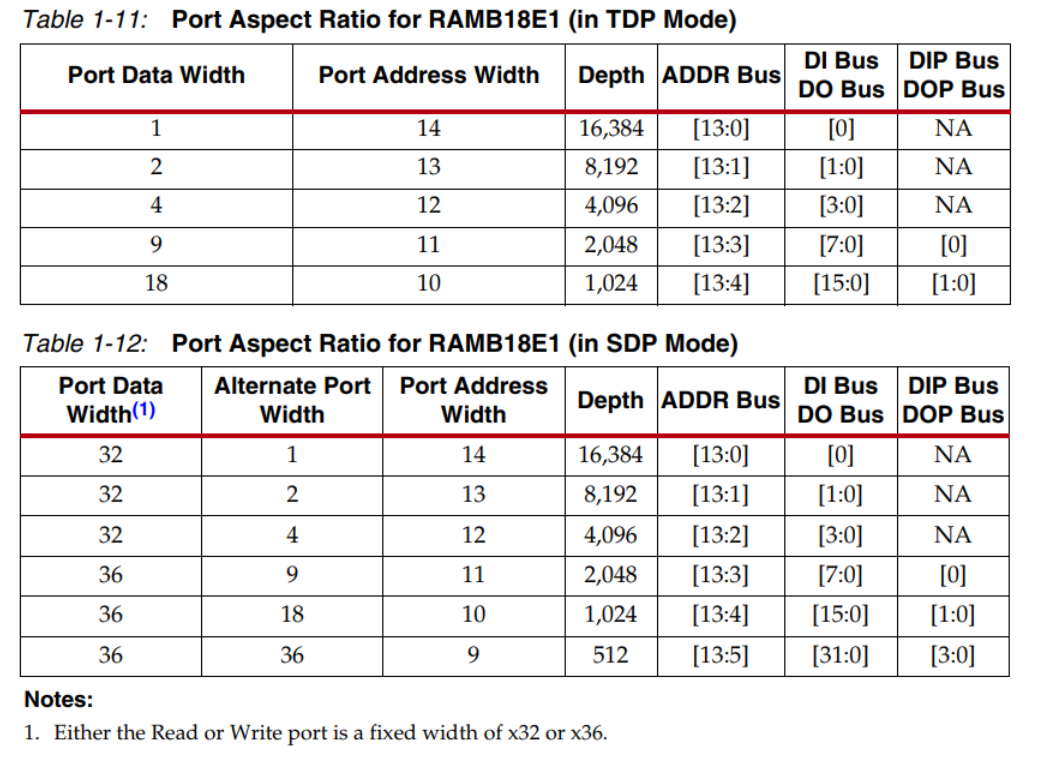

地址总线选择用于读取或写入的存储单元。 在 SDP 模式下,ADDRA 端口是 RDADDR,ADDRB 端口是 WRADDR。 端口的数据位宽决定了单个 RAMB18E1 或 RAMB36E1 所需的地址总线宽度,如下表所示,列举了不同模式下,RAMB18E1和RAMB36E1端口配置 。

对于使用 RAMB36E1 的可级联 Block RAM,数据宽度为 1 位,地址总线为 16 位 [15:0]。 地址位 15 仅用于级联块 RAM。 对于非级联块 RAM,连接高。

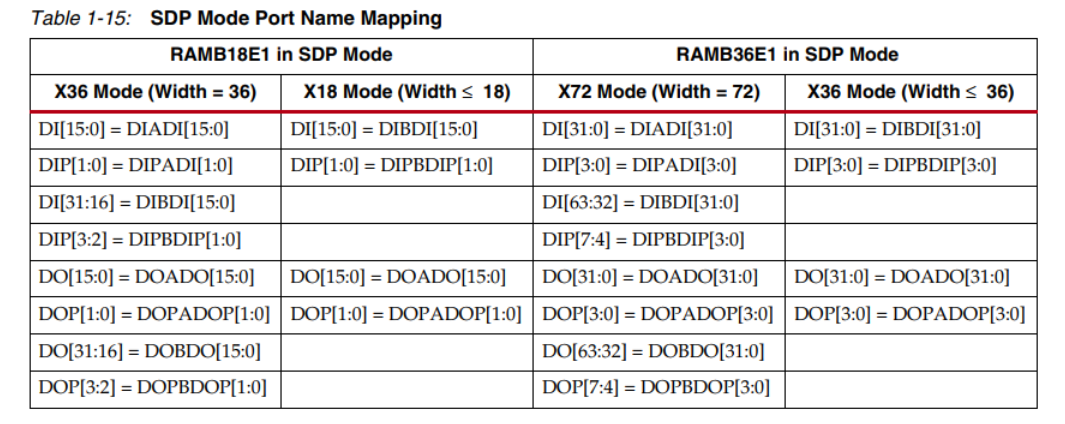

SDP模式端口名称映射如下表所示。

数据输入总线 - DIADI、DIPADIP、DIBDI 和 DIPBDIP

数据输入总线提供要写入 RAM 的新数据值。 常规数据输入总线 (DI) 以及可用的奇偶校验数据输入总线 (DIP) 的总宽度等于端口宽度。 例如 36 位端口数据宽度由 DI[31:0] 和 DIP[3:0] 表示。

数据输出总线 - DOADO、DOPADOP、DOBDO 和 DOPBDOP

数据输出总线反映了在读取操作期间最后一个有效时钟沿处地址总线所引用的存储单元的内容。 在写入操作(WRITE_FIRST 或 READ_FIRST 配置)期间,数据输出总线反映正在写入的数据或写入前存储的值。 在 NO_CHANGE 模式下的写操作期间,数据输出总线不会改变。 常规数据输出总线 (DO) 加上奇偶校验数据输出总线 (DOP)(如果可用)的总宽度等于端口宽度。

级联

CASCADEINA、CASCADEINB、CASCADEOUTA 和 CASCADEOUTB

CASCADEIN/CASCADEOUT 引脚用于连接两个 Block RAM 以形成 64K x 1 模式,如下图。 上部 Block RAM 的 CASCADEIN 引脚连接到相应端口的下部 Block RAM 的 CASCADEOUT 引脚。 当不使用级联模式时,该引脚不需要连接。 有关详细信息,请参阅级联块 RAM。 级联仅在 TDP 模式下可用。

反相控制引脚

对于每个端口,八个控制引脚(CLK、EN、RSTREG 和 RSTRAM)都有一个单独的反相选项。 EN、RSTREG 和 RSTRAM 控制信号可配置为高电平有效或低电平有效,时钟可在上升沿或下降沿有效(默认为上升沿有效),无需其他逻辑资源。

GSR

7 系列器件的全局设置/复位 (GSR) 信号是异步全局信号,在器件配置结束时有效。 GSR 还可以随时恢复初始 7 系列设备状态。 GSR 信号将输出锁存器初始化为 INIT(简单双端口)或 INIT_A 和 INIT_B 值(真双端口)。 请参见块 RAM 属性。 GSR 信号对内部存储器内容没有影响。 因为它是一个全局信号,所以 GSR 在功能级别(块 RAM 原语)没有输入引脚。 当 GSR 被断言时,写操作并不总是成功的。

未使用的输入

未使用的数据输入应连接到低电平。 未使用的地址输入应连接为高电平。

Block RAM 地址映射

每个端口使用取决于它是 RAMB18E1 还是 RAMB36E1 的寻址方案访问同一组18,432 或 36,864 个存储单元。 使用以下公式确定针对特定宽度寻址的物理 RAM 位置(仅当两个端口使用不同的纵横比时才有意义):

E

N

D

=

(

(

A

D

D

R

+

1

)

×

W

i

d

t

h

)

−

1

S

T

A

R

T

=

A

D

D

R

×

W

i

d

t

h

END = ((ADDR + 1) × Width) -1 \newline START = ADDR × Width

END=((ADDR+1)×Width)−1START=ADDR×Width

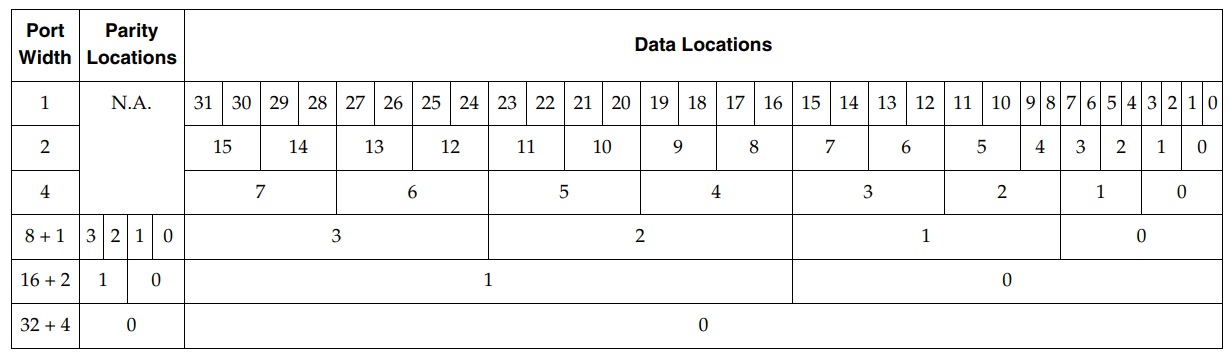

下表显示了每个端口宽度的低位地址映射。

Block RAM 属性

内容初始化 - INIT_xx

内存内容可以在配置比特流中初始化或清除。 在上一代 Virtex 设备中,可以通过空白比特流初始化或读回内存内容。 在 7 系列器件中,由于电源门控特性,Block RAM 初始化或回读需要标准的有效比特流。

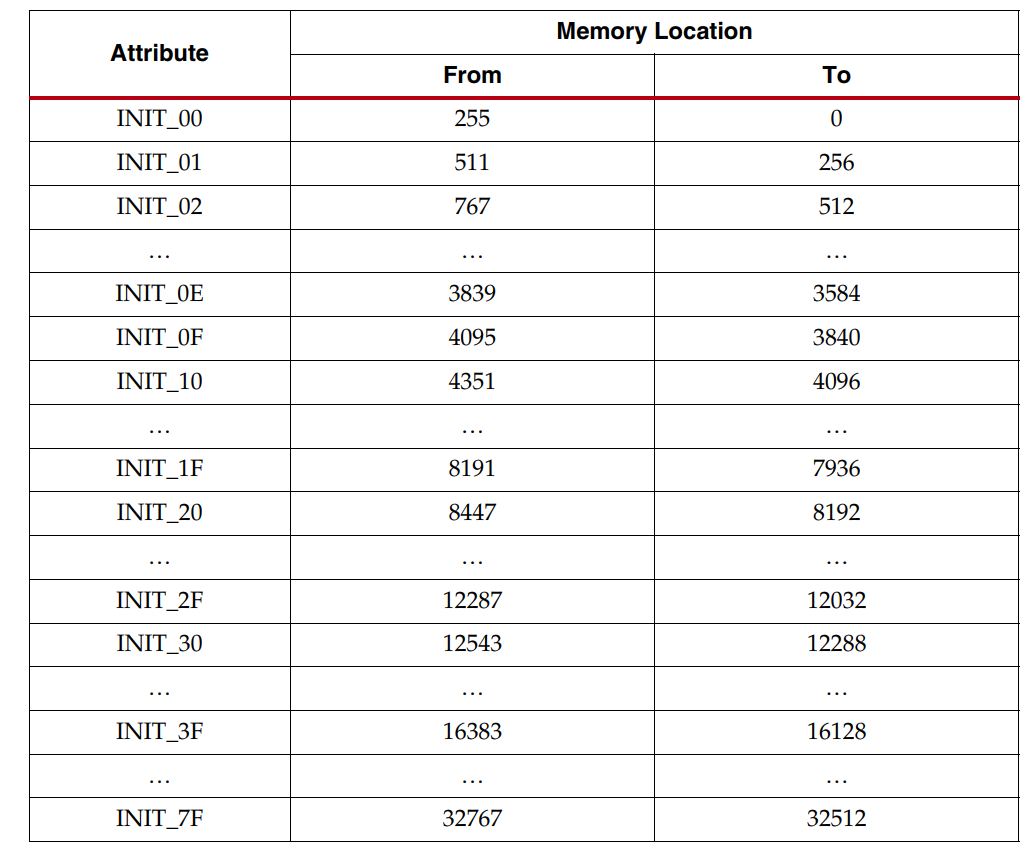

INIT_xx 属性定义初始内存内容。 默认情况下,Block RAM 在器件配置序列期间初始化为全零。 RAMB18E1 从 INIT_00 到 INIT_3F 的 64 个初始化属性,以及 RAMB36E1 从 INIT_00 到 INIT_7F 的 128 个初始化属性代表常规存储器内容。

每个 INIT_xx 是一个 64 位十六进制编码的位向量。 内存内容可以部分初始化,并自动以零完成。以下公式用于确定每个 INIT_xx 属性的位位置。

给定 yy = 十六进制编码到十进制 (xx) 的转换,INIT_xx 对应的存储单元如下:

- 从 [(yy + 1) × 256] – 1

- 到 (yy) × 256

例如,对于属性 INIT_1F,转换如下:

- yy = 十六进制编码转换为十进制 (xx) “1F” = 31

- 从 [(31+1) × 256] – 1 = 8191

- 到 31 × 256 = 7936

内容初始化 - INITP_xx

INITP_xx 属性定义对应于 DIP/DOP 总线(奇偶校验位)的存储单元的初始内容。 默认情况下,这些存储单元也被初始化为全零。

初始化属性表示奇偶校验位的内存内容。 RAMB18E1 的八个初始化属性是 INITP_00 到 INITP_07。 RAMB36E1 的 16 个初始化属性是 INITP_00 到 INITP_0F。 每个 INITP_xx 是一个 64 位十六进制编码的位向量,具有常规的 INIT_xx 属性行为。相同的公式可用于计算由特定 INITP_xx 属性初始化的位置。

输出锁存器初始化 - INIT(INIT_A 或 INIT_B)

INIT(单端口)或 INIT_A 和 INIT_B(双端口)属性定义配置后的输出锁存器或输出寄存器值。 INIT(INIT_A和INIT_B)属性的宽度为端口宽度,如下表所示。 这些属性是十六进制编码的位向量,默认值为 0。在级联模式下,上下块 RAM 应初始化为相同的值。

输出锁存器/寄存器同步设置/复位 (SRVAL_[A|B])

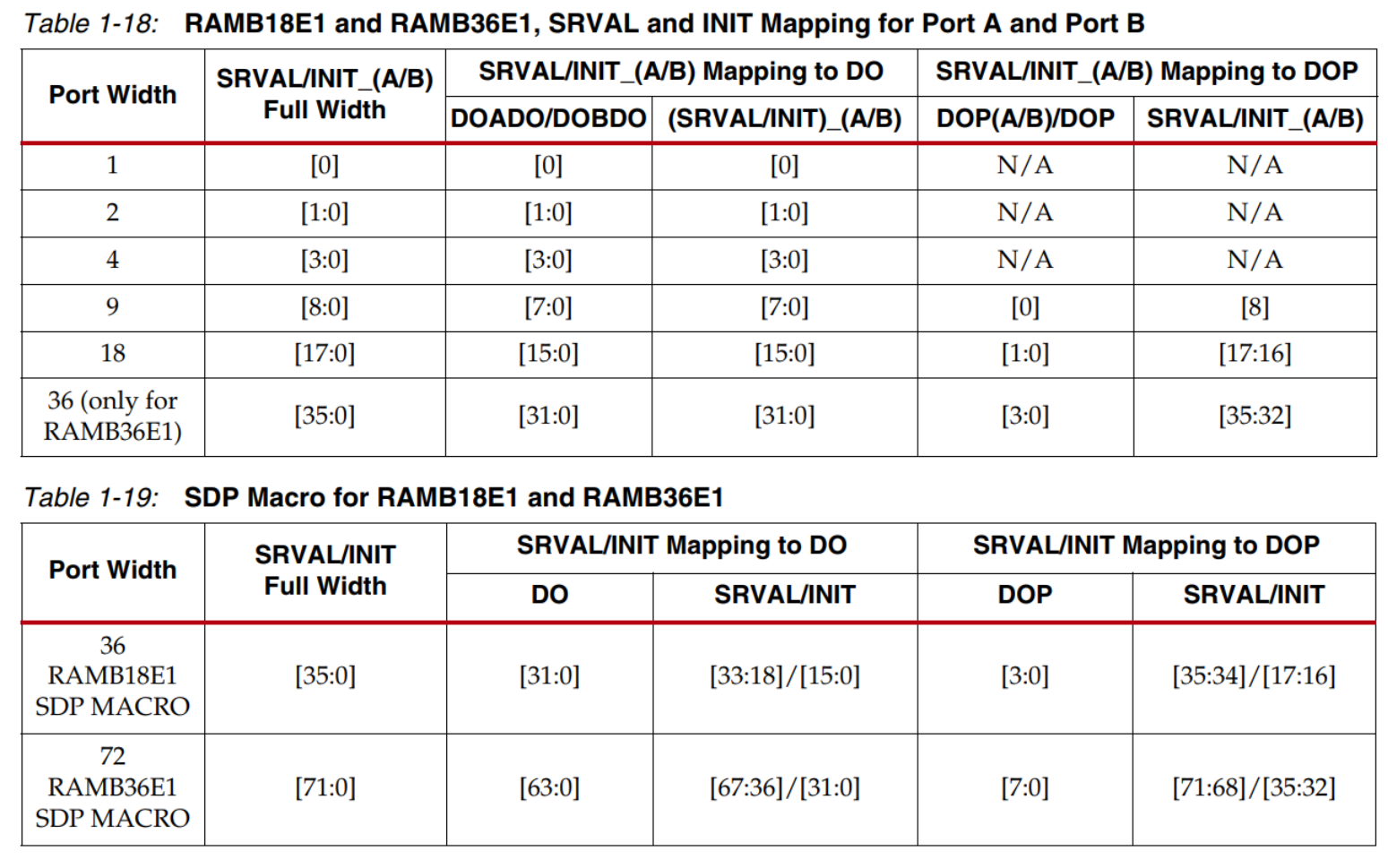

SRVAL(单端口)或 SRVAL_A 和 SRVAL_B(双端口)属性定义了 RSTRAM/RSTREG 输入有效时的输出锁存器值。 SRVAL(SRVAL_A和SRVAL_B)属性的宽度就是端口宽度,如表1-18所示。 这些属性是十六进制编码的位向量,默认值为 0。此属性在设置可选输出寄存器属性时设置输出寄存器的值。 当不使用寄存器时,锁存器被设置为 SRVAL。 表 1-18 和表 1-19 显示了 SRVAL 和 INIT 位位置如何映射到 Block RAM 原语和 SDP 宏的 DO 输出。

复位或 CE 优先级 - RSTREG_PRIORITY_[A|B]

当 DO_REG = 1 时,该属性确定 RSTREG 或 REGCE 的优先级。有效值为 RSTREG 或 REGCE。

可选输出寄存器开/关开关 - DO[A|B]_REG

_此属性设置块 RAM 的 A/B 输出处的流水线寄存器数量。 有效值为 0(默认)或 1。

扩展模式地址决定因素 - RAM_EXTENSION_[A|B]

此属性确定在使用级联模式时,感兴趣的 Block RAM 是否将其 A/B 端口作为 UPPER/LOWER 地址。 在级联模式下不使用 Block RAM 时,默认值为 NONE。

读取宽度 - READ_WIDTH_[A|B]

此属性确定 Block RAM 的 A/B 读取端口宽度。 有效值为:0(默认)、1、2、4、9、18、36,在 SDP 模式下使用 RAMB36E1 端口 A 时,为 72。

写入宽度 - WRITE_WIDTH_[A|B]

此属性确定 Block RAM 的 A/B 写入端口宽度。 有效值为:0(默认)、1、2、4、9、18、36,在 SDP 模式下使用 RAMB36E1 端口 A 时,为 72。

模式选择 - RAM_MODE

此属性选择真双端口模式 (TDP) 或简单双端口模式 (SDP)。有效值为:TDP(默认)或 SDP。

写入模式 - WRITE_MODE_[A|B]

此属性确定 A/B 输入端口的写入模式。 可能的值为 WRITE_FIRST(默认)、READ_FIRST 和 NO_CHANGE。

RDADDR_COLLISION_HWCONFIG

此属性允许在 SDP 或 TDP 模式下的性能和潜在地址重叠(冲突)之间进行权衡。 如果 SDP 模式下的 Block RAM 设置为 READ_FIRST 或 TDP 模式下的 Block RAM 已将任何端口设置为 READ_FIRST 模式,则地址重叠可能发生在同步或异步时钟应用中。 对于 RAMB36E1,地址重叠被定义为 A14-A8 在同一时钟周期中对于两个端口是相同的,并且两个端口都被启用。 对于 RAMB18E1,地址重叠定义为 A13-A7 在相同时钟周期内的两个端口相同,并且两个端口都启用。

如果地址重叠(冲突)不能发生,则可以通过将此属性设置为 PERFORMANCE 来恢复整个 Block RAM 性能。 否则,您应该将其设置为 DELAYED_WRITE(默认)。 如果在 PERFORMANCE 模式下发生地址冲突,则存储单元的内容可能会被破坏。

SIM_COLLISION_CHECK

此属性设置模拟模型中的碰撞检查和行为级别。

可能的值为 ALL(默认)、GENERATE_X_ONLY、NONE 和 WARNING_ONLY。

INIT_FILE

该属性指向一个可选的 RAM 初始化文件(初始内容)。 值为 NONE(默认)或 STRING(文件名)。

SIM_DEVICE

该属性设置仿真目标器件系列。 允许的值为 NONE(默认)或具有系列名称的 STRING:VIRTEX5、VIRTEX6(默认)、7_SERIES。

Block RAM 位置约束

Block RAM 实例可以附加 LOC 属性以约束放置。Block RAM 放置位置不同于用于命名 CLB 位置的约定,允许 LOC 属性在阵列之间传输。

LOC 属性使用以下形式:

LOC = RAMB36_X#Y#

RAMB36_X0Y0 是器件左下方的块 RAM 位置。 如果 RAMB36E1 被限制为 RAMB36_X#Y#,则 FIFO 不能被限制为 FIFO36_X#Y#,因为它们共享一个位置。

两个 RAMB18E1 可以放在同一个 RAMB36E1 位置:

inst "my_ramb18_2" LOC = RAMB36_X0Y0

inst "my_ramb18_1" LOC = RAMB36_X0Y0

此外,一个 FIFO18 和一个 RAMB18 可以放在同一个 RAMB36E1 位置:

inst "my_ramb18" LOC = RAMB36_X0Y0

inst "my_fifo18" LOC = RAMB36_X0Y0

VHDL 或 Verilog 代码中的 Block RAM 初始化

Block RAM 属性和内容可以在 VHDL 或 Verilog 代码中初始化,用于通过在实例化组件中使用通用映射 (VHDL) 或 defparams (Verilog) 进行综合和仿真。 修改通用映射或 defparam 的值会影响仿真行为和实现的综合结果。 推断的块 RAM 也可以被初始化。 7 系列 FPGA 库指南包含用于例化 RAMB36E1 原语的代码。

其他 RAMB18E1 和 RAMB36E1 原语设计注意事项

RAMB18E1 和 RAMB36E1 原语在 7 系列 FPGA 块 RAM 解决方案中是不可或缺的。

可选输出寄存器

可选输出寄存器可用于 RAMB18E1 和 RAMB36E1 的 A|B 输出端口中的一个或两个。 使用 DO[A|B] _REG属性进行选择。

两个独立的时钟使能引脚是 REGCE[A|B]。 在端口 [A|B] 上使用可选输出寄存器时,端口 [A|B] 的同步置位/复位(RSTREG 和 RSTRAM)引脚的置位会导致属性 SRVAL 指定的值在输出中寄存。

下图显示了一个可选的输出寄存器。

独立读写端口宽度

要使用 Block RAM 的双端口模式指定端口宽度,设计人员必须使用 READ_WIDTH_[A|B] 和 WRITE_WIDTH_[A|B] 属性。 应考虑以下规则:

- 设计单端口 Block RAM 需要设置一次写入和一次读取的端口对宽度(例如,READ_WIDTH_A 和 WRITE_WIDTH_A)。

- 设计双端口块 RAM 需要设置所有端口宽度。

- 使用这些属性时,如果两个写端口或两个读端口都设置为0,Xilinx 工具不会实现该设计。 在简单双端口模式下,端口的一侧是固定的,而另一侧可以具有可变宽度。 RAMB18E1 的数据端口宽度高达 36,而 RAMB36E1 的数据端口宽度高达 72。

RAMB18E1 和 RAMB36E1 端口映射设计规则

7 系列 FPGA 块 RAM 可配置为各种端口宽度和大小。根据配置,某些数据引脚和地址引脚未使用。这些规则对于确定 RAMB 端口连接很有用:

- 使用 RAMB36E1 时,如果 DI[A|B] 引脚宽度小于 32 位,则将 (32 – DI_BIT_WIDTH) 逻辑零连接到 DI[A|B] 的前面。

- 如果 DIP[A|B] 引脚宽度小于 4 位,则将 (4 – DIP_BIT_WIDTH) 逻辑零连接到 DIP[A|B] 的前面。 DIP[A|B] 在不使用时可以不连接。

- DO[A|B] 引脚必须为 32 位宽。 但是,有效数据只能在引脚 DO_BIT_WIDTH – 1 到 0 上找到。

- DOP[A|B] 引脚必须为 4 位宽。 然而,有效数据只能在引脚 DOP_BIT_WIDTH – 1 到 0 上找到。DOP[A|B] 在不使用时可以保持不连接。

- ADDR[A|B] 引脚必须为 16 位宽。 但是,非级联块 RAM 的有效地址只能在引脚 14 到(15 - 地址宽度)上找到。 其余引脚,包括引脚 15,应绑高。

级联块 RAM

要使用级联块 RAM 功能:

- 必须例化两个 RAMB36E1 原语。

- 将一个RAMB36E1 的RAM_EXTENSION_A 和RAM_EXTENSION_B 属性设置为UPPER,另一个设置为LOWER。

- 将上部RAMB36E1 CASCADEINA 和CASCADEINB 端口连接到下部RAMB36E1 的CASCADEOUTA 和CASCADEOUTB 端口。

- 上部 RAMB36E1 的 CASCADEOUT 端口不需要连接。 将下部 RAMB36E1 的 CASCADEIN 端口连接到逻辑高或低。

- 不使用低位RAMB36E1 的数据输出端口。 这些引脚未连接。

- 如果对两个 RAMB36E1 施加位置限制,它们必须相邻。 如果未指定位置约束,Xilinx 工具会自动管理 RAMB36E1 位置。

- 地址引脚ADDR[A|B] 必须为16 位宽。 读和写端口都必须是一位宽。

- 通过设置DO_REG = 1 属性可以使用可选的输出寄存器。

字节宽写使能

使用字节宽写使能功能时应考虑以下规则:

- 对于 RAMB36E1

- 在 x72 SDP 模式下,WEBWE< 7:0 > 用于连接写端口的八个 WE 输入。 WEA< 3:0 > 未使用。

- 在x36 模式下,WEA[3:0] 用于连接端口A 的四个WE 输入,WEBWE< 3:0 > 用于连接端口B 的四个WE 输入。未使用WEBWE< 7:4 >。

- 在x18 模式下,WEA[1:0] 用于连接端口A 的两个用户WE 输入,WEBWE< 1:0 > 用于连接端口B 的两个WE 输入。WEA< 3:2 > 和WEBWE < 7:2 > 未使用。

- 在 x9 或更小的端口宽度模式下,WEA[0] 用于连接端口 A 的单个用户 WE 输入,WEBWE<0> 用于连接端口 B 的单个 WE 输入。WEA< 3:1 > 和 WEBWE < 7:1 > 未使用。

- 对于 RAMB18E1

- 在 x36 SDP 模式下,WEBWE< 3:0 > 用于连接写入端口的四个 WE 输入。 WEA< 1:0 > 未使用。

- 在x18 模式下,WEA[1:0] 用于连接端口A 的两个WE 输入,WEBWE< 1:0 > 用于连接端口B 的两个WE 输入。未使用WEBWE< 3:2 >。

- 在 x9 或更小的端口宽度模式下,WEA[0] 用于连接端口 A 的单个用户 WE 输入,WEBWE<0> 用于连接端口 B 的单个 WE 输入。WEA<1> 和 WEBWE<3 :1> 未使用。

Block RAM 应用

创建更大的 RAM 结构

Block RAM 列具有特殊的布线(除了 64K x 1 级联),可以使用 36 Kb Block RAM 以最小的布线延迟创建更宽/更深的块。 与使用正常布线资源时相比,更宽或更深的 RAM 结构以更小的时序损失实现。

综合推理或赛灵思 CORE Generator 工具程序为您提供了一种使用多个 Block RAM 实例生成更宽、更深的存储器结构的简单方法。 该程序输出 VHDL 或 Verilog 实例化模板和仿真模型,以及用于包含在设计中的 EDIF 文件。

寄存器模式下的 Block RAM RSTREG

寄存器模式下的 Block RAM RSTREG 可用于将输出寄存器控制为独立于 Block RAM 的真正流水线寄存器。 如下图所示,Block RAM 可以独立于寄存器启用或设置/复位进行读写。

在寄存器模式下,RSTREG 将 DO 设置为 SRVAL,并且可以将数据从 Block RAM 读取到 DBRAM。 DBRAM 中的数据可以在下一个周期输出 (DO)。 图 1-12 到图 1-14 中的时序图显示了 RSTREG 操作的不同情况。

Block RAM 时序模型

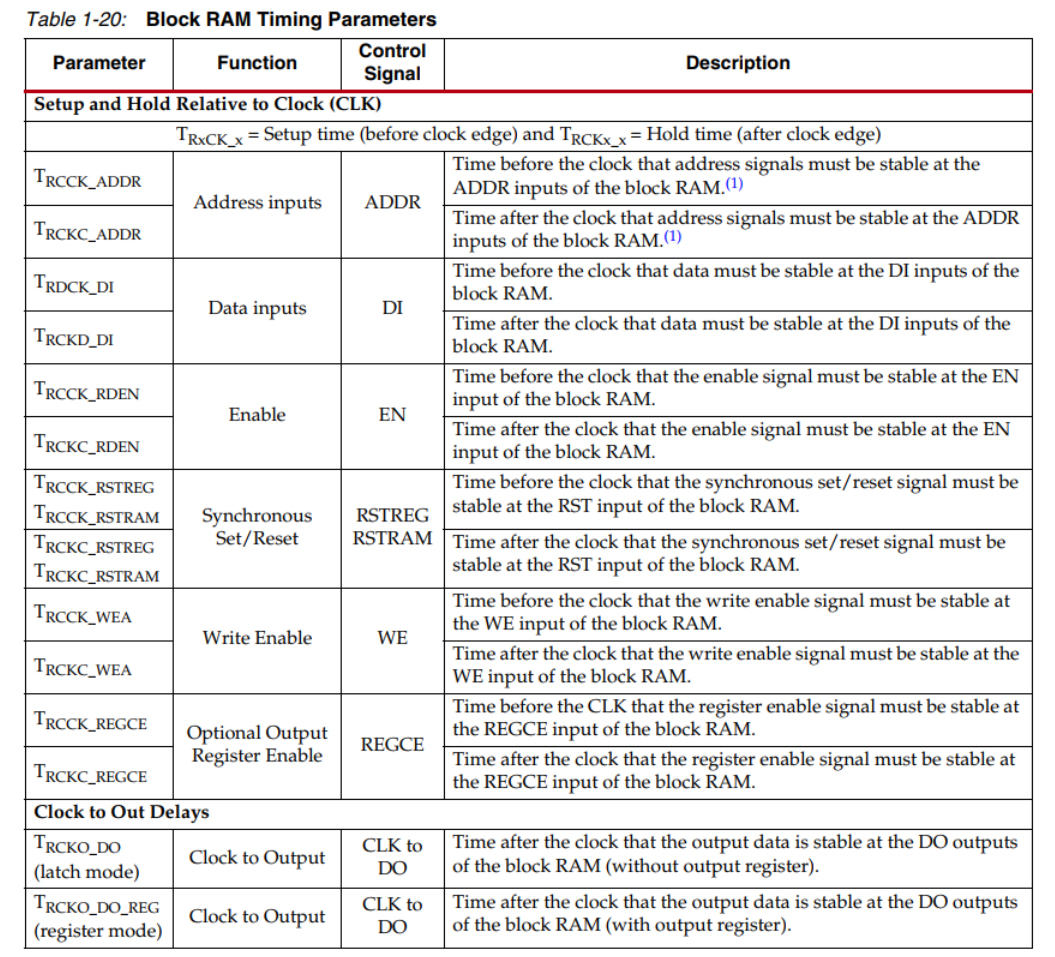

7 系列器件中的 Block RAM 相关的时序参数如下图所示。

Block RAM 时序参数

下表显示了 7 系列 FPGA 的 Block RAM 时序参数。

Block RAM 时序特性

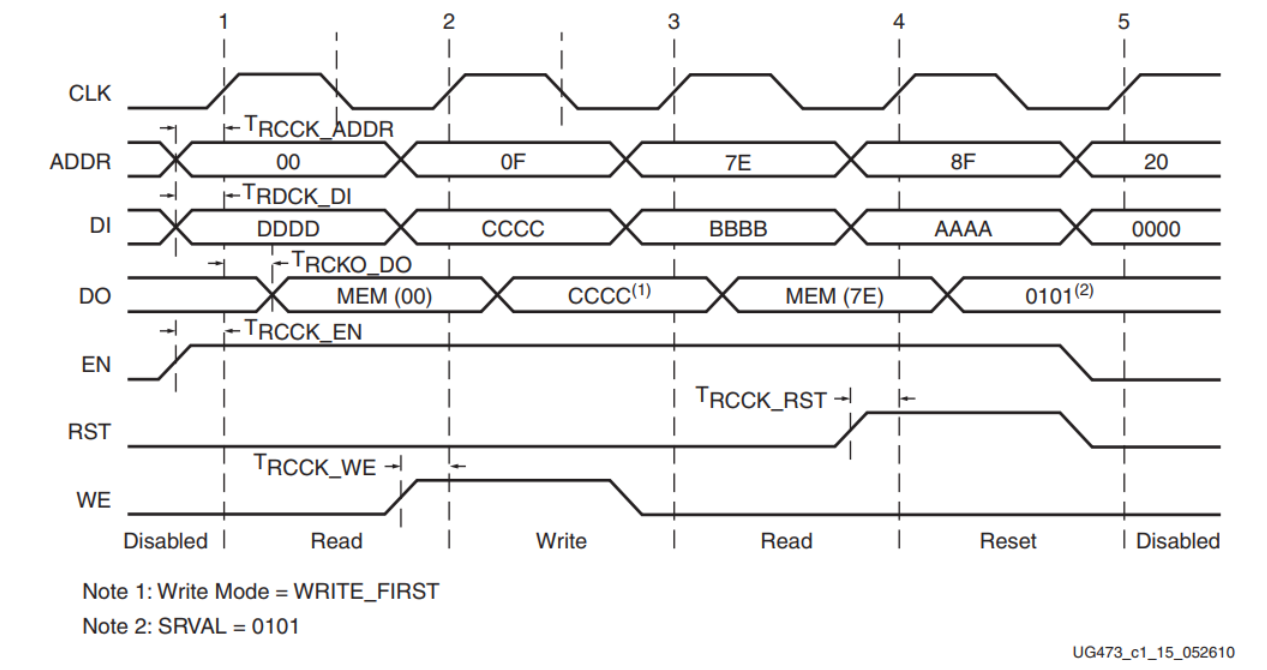

下图中的时序图描述了单端口 Block RAM 处于先写模式,没有可选的输出寄存器。 read-first 和 no-change 模式的时序是相似的。 对于使用可选输出寄存器的时序,DO 引脚会出现额外的时钟延迟。 当不使用可选输出流水线寄存器时,这些波形对应于锁存模式。

在时间 0,块 RAM 被禁用; EN(启用)为低电平。

时钟事件 1 读操作

在读操作期间,ADDR 输入地址处的存储器内容保持不变。

- T RCCK_ADDR 在时钟事件 1 之前,地址 00 在 Block RAM 的 ADDR 输入处变为有效。

- 在时钟事件1 之前的时间TRCCK_EN 处,使能在块RAM 的EN 输入处被置为高电平,从而为随后的读取操作启用存储器。

- 在时钟事件 1 之后的 TRCKO_DO 时间,地址 00 的存储器内容在 Block RAM 的 DO 引脚上变得稳定。

- 只要EN 被置位,所有地址更改都必须满足指定的建立和保持窗口。 异步地址更改会以不可预知的方式影响存储器内容和块 RAM 功能。

时钟事件 2 写操作

在写操作期间,由 ADDR 输入上的地址指定位置的存储器内容被 DI 引脚上的值替换,并立即反映在输出锁存器上(在 WRITE_FIRST 模式下); 当写使能(WE)为高。

- 在时钟事件 2 之前的时间 TRCCK_ADDR 处,地址 0F 在 Block RAM 的 ADDR 输入处变为有效。

- 在时钟事件2 之前的时间TRDCK_DI,数据CCCC 在块RAM 的DI 输入处变为有效。

- 在时钟事件2 之前的时间TRCCK_WE,写使能在块RAM 之后的WE 处变为有效。

- 在时钟事件2 之后的时间TRCKO_DO,数据CCCC 在块RAM 的DO 输出上变为有效。

时钟事件 4 RST(同步置位/复位)操作

在 RSTRAM 操作期间,初始化参数值 SRVAL 被加载到 Block RAM 的输出锁存器中。 RSTRAM 操作不会改变存储器的内容,并且独立于 ADDR 和 DI 输入。

- 在时钟事件4 之前的时间TRCCK_RST,同步置位/复位信号在Block RAM 的RSTRAM 输入处变为有效(高电平)。

- 在时钟事件 4 之后的 TRCKO_DO 时间,SRVAL 0101 在 Block RAM 的 DO 输出上变为有效。

时钟事件 5 禁用操作

置低启用信号 EN 会禁用任何写入、读取或 RST 操作。 禁用操作不会改变存储器的内容或输出锁存器的值。

- 在时钟事件5 之前的时间TRCCK_EN,使能信号在Block RAM 的EN 输入处变为无效(低)。

- 在时钟事件 5 之后,Block RAM 的 DO 输出上的数据保持不变。

Block RAM 时序模型

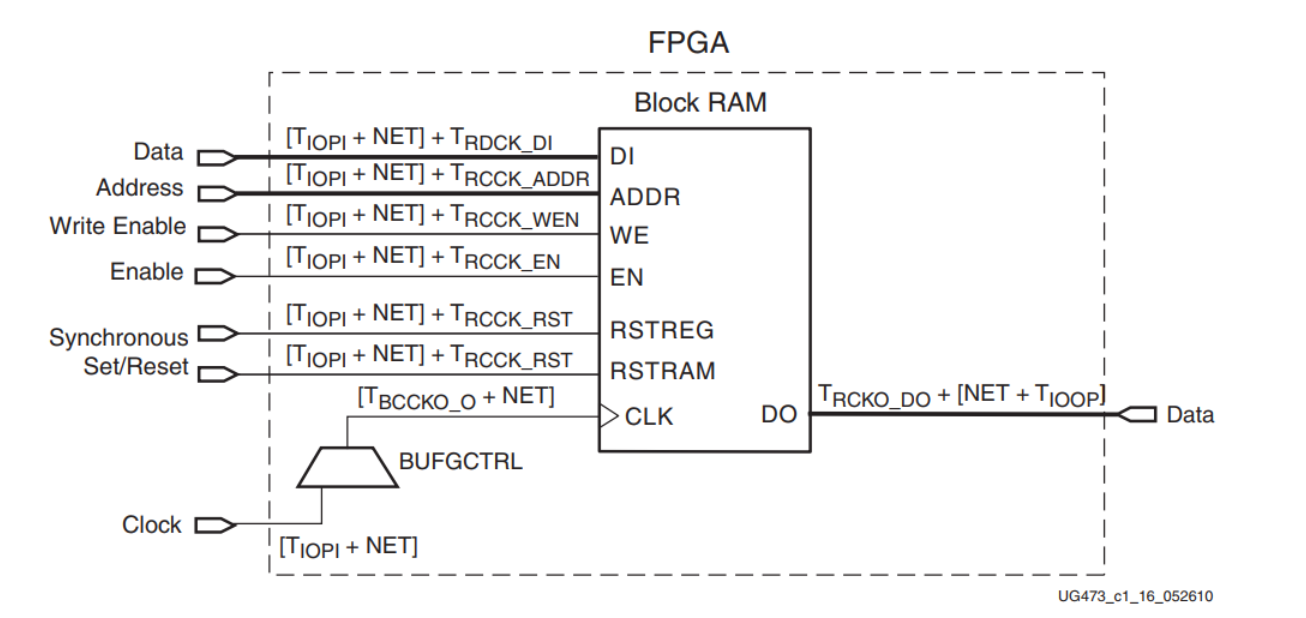

下图说明了与 Block RAM 实现相关的延迟路径。

此示例采用最简单的 FPGA 上和下路径(这些路径可能因设计而异)。 该时序模型演示了如何以及在何处使用 Block RAM 时序参数。

- NET = 可变互连延迟

- TIOPI = IOB 延迟的焊盘到 I 输出

- TIOOP = IOB 的 O-输入到焊盘延迟

- T BCCKO_O = BUFGCTRL 延迟

reference

- UG473

相关文章

- spring mvc:拦截器不拦截静态资源的三种处理方式

- K8s 资源全汇总 | K8s 大咖带你 31 堂课从零入门 K8s

- Android应用开发提高系列(5)——Android动态加载(下)——加载已安装APK中的类和资源

- 重学c#系列——c# 托管和非托管资源与代码相关(四)

- 干货分享 | 数据仓库如何应对资源不足?

- k8s kubebuilder系列开发 — 编写自定义资源和Reconciliation循环

- 【云原生 | Kubernetes 系列】Kubernetes 资源限制

- 博客内的百度网盘资源公开目录下载

- Atitit 艾提拉音频资源列表与统计 t6 六月份战果与7月份规划.docx 目录 1. 第一层次 原始资源类 采集资源类1 1.1. K歌类采集资源 整理1 1.2. K歌类资源初步分类

- 资源编排Instance Clone 实现详解

- Linux内核 下载外网资源 如何高速下载国外资源 快速下载Linux内核

- Kubernetes基础自学系列 | Kubernetes资源清单

- LabVIEW使用TDMS碎片整理VI会消耗RT目标所有的处理器资源

- FPGA - 7系列 FPGA内部结构之CLB -01- CLB资源概述

- FPGA - 7系列 FPGA内部结构之Clocking -02- 时钟布线资源

- FPGA - 7系列 FPGA内部结构之SelectIO -03- 逻辑资源之ILOGIC