RFSoC应用笔记 - RF数据转换器 -14- RFSoC自动增益控制与NCO跳频功能

应用概述

本文概述了如何在系统中使用RFSoC 射频数据转换器的自动增益控制和NCO跳频功能。

自动增益控制系统

自动增益控制 (AGC) 常用于 RF-ADC 应用中,其中输入的动态范围变化很大。 它提供了一种使用 RFADC 输入范围和最大化信噪比 (SNR) 的方法,同时提供了响应变化信号幅度的灵活性。

AGC 系统由以下组件组成:

- 可变增益放大器 (VGA)

- RF-ADC

- 信号幅度监控

- AGC 算法/决策逻辑

- 数字增益补偿

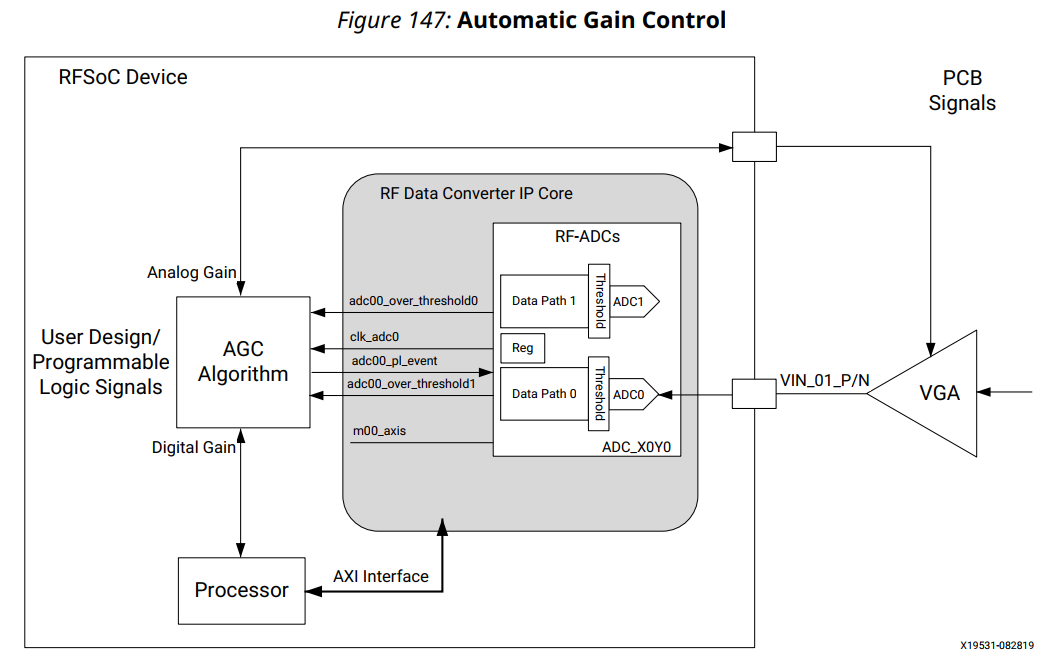

RFSoC RF-ADC 通道允许实施定制 AGC 解决方案 通过将信号幅度监测和补偿功能集成到 RFADC 块中。 这些功能可以与嵌入在 FPGA PL 中的外部 VGA 和 AGC 逻辑一起使用。RFSoC Gen 3 器件在每个 RF-ADC 块中集成了 DSA。 如下图所示。

此图显示了一个示例 AGC 应用程序。 使用阈值功能在每个 RF-ADC 通道内实施信号幅度监控。 此功能提供了两个可以对每个 RF-ADC 通道进行编程的阈值。 当违反阈值电平时,会直接在 PL 中指示,从而绕过数据路径中的任何延迟。AGC 的高级操作示例如下:

-

在系统初始化时,阈值电平和模式,包括从 PL 启用阈值清除功能,由 RFdc 驱动程序 API 设置。

-

如果违反阈值水平:

-

实时超过阈值输出标志置位。

-

基于 PL 的 AGC 算法做出决定并计算新的 VGA 增益和补偿增益。

-

增益值被编程到 VGA 和数字补偿逻辑。

-

adcXY_pl_event 由 AGC 逻辑断言。

-

阈值被清除。

数字增益补偿

当 VGA 调整模拟信号电平时,可能需要在 RF-ADC 之后进行数字补偿,以保持整体信号电平恒定。 为了最大限度地减少对接收信号的干扰,可以调整增益调整,以便在相对于所应用的模拟增益的相同时间点应用数字补偿。 这个应用时刻必须考虑到模拟增益变化通过 VGA、RF-ADC 和数字逻辑的传播之间的相对延迟。 有多种方法可以实现这种增益调整和同步应用。

使用 QMC 增益进行补偿

QMC 增益功能内置于 RF-ADC 块中,并提供 0 到 2.0 之间的可编程增益,具有 16 位输出分辨率。 使用它,可以放置 12 位 RF-ADC 输出信号,以通过数字数据路径提供灵活的动态范围。 QMC 模块中增益值的应用时刻可以由 adcXY_pl_event 信号控制。 该信号由 PL 中的用户设计直接控制,应延迟以考虑外部 VGA 调整和 RF-ADC 转换所需的延迟。 使用此选项时,可在应用增益时自动清除粘性阈值输出。

使用 PL 增益进行补偿

对于更宽的动态范围数字增益调整,可以使用 FPGA PL。 与 QMC 增益方法类似,应使用通过 VGA、RF-ADC 和数据路径的延迟来延迟 PL 中增益变化的应用。 PL 增益更改后,可以使用 RFdc 驱动程序 API 或发出 adcXY_pl_event 清除阈值。

确定增益变化延迟

为了在正确的时刻应用数字增益补偿,增益变化通过模拟路径的传播之间的相对延迟必须与数字增益更新代码通过数字路径的传播保持一致。 由于外部 VGA 通信和响应时间特定于用户应用程序,因此必须在系统中测量这些相对延迟。 对于数字路径,每个图块都有一个名为 adcXY_pl_event 的专用输入,可用于在确定的时间应用设置,例如增益。 为了确定数字和模拟路径之间的相对延迟,应在设计阶段应用恒定幅度的测试信号,并应用数字和模拟增益调整。 查看输出数据,可以将数字和模拟增益应用时刻之间的增量时间观察为输出信号幅度中的驼峰/直通。 该增量时间应通过计算 RF-ADC 输出时钟 (clk_adcX) 的周期添加到 adcXY_pl_event 断言中。

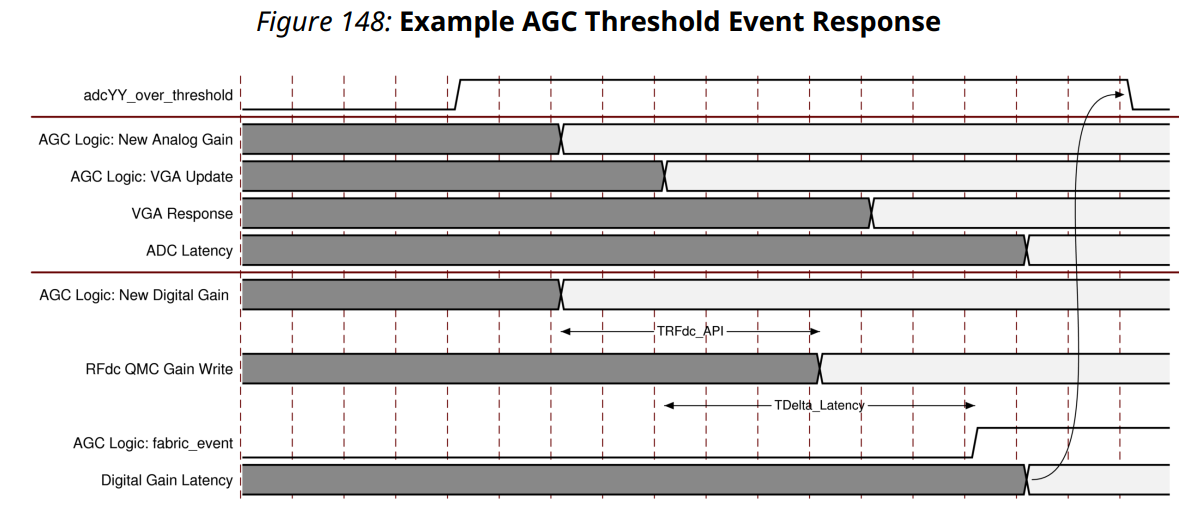

在设计的正常操作期间使用此预定延迟可确保对齐增益应用时刻。下图说明了响应示例 AGC 应用程序的阈值事件的阶段。 图的中间区域代表与模拟/VGA路径相关的信号,而下部区域代表与数字路径相关的信号。

如图所示,AGC 更新由阈值的断言启动。 作为对此的响应,PL 中的 AGC 算法计算要对模拟和数字路径进行的增益调整。 VGA 更新写入、VGA 稳定响应和 RF-ADC 延迟显示了延迟通过模拟路径的传播。 通过数字路径的传播延迟由 API 写入新增益值(用 TRFdc_API 表示)和 adcXY_pl_event 断言(用 TDelta_Latency 表示)来显示。 TDelta_Latency 由用户应用程序选择以匹配数字和模拟延迟。 应用数字增益更新后,如果启用了 Auto-Clear 功能,则可以自动取消断言阈值。

使用 RFdc 驱动程序 API 应用 QMC 增益可能会产生一些驱动程序开销。 在不希望出现这种延迟的应用中,可以使用 PL 数字增益补偿方法。

NCO 跳频

当使用带有数控振荡器的 RF-ADC 或 RF-DAC 混频器时,可以使用 RF-ADC 和 RF-DAC 实时 NCO 接口实时调整 NCO 的频率。 本节介绍这些接口的操作。

在执行跳频时,必须将有关 NCO 所需相位和频率的信息传送到 IP 内核。 NCO 频率由 48 位二进制补码有符号数 nco_freq 设置。 nco_freq 信号的范围为 -Fs/2 到 Fs/2。 最大正值 (0x7FFF_FFFF_FFFF) 产生 Fs/2 的 NCO 频率,而最大负值 (0x8000_0000_0000) 产生 -Fs/2 的 NCO 频率。 如下表所示。

| NCO Frequency | nco_freq |

|---|---|

| -Fs/2 | 0x8000_0000_0000 |

| -Fs/4 | 0xc000_0000_0000 |

| 0 | 0x0000_0000_0000 |

| Fs/4 | 0x3FFF_FFFF_FFFF |

| Fs/2 | 0x7FFF_FFFF_FFFF |

如果所需的 NCO 频率高于 Fs/2,则应根据需要通过减去采样频率将频率折叠到 -F s/2 到 Fs/2 范围内。 类似地,对于较大的负频率,将采样频率添加到所需的 NCO 频率,直到它在范围内。 对于偶数 Nyquist 区域中的 NCO 频率,结果频率应取反。对于选择校准模式 1 的 Gen 1 和 Gen 2 RF-ADC,混频器频率应降低 Fs/2。

相位信息由 nco_phase 携带。 这是添加到 NCO 累加器输出的相位偏移。 nco_phase 输入是一个 18 位二进制补码有符号数,范围为 -180 到 180 度。 最大正值 (0x1_FFFF) 给出 180 度的相移。 最大负值 (0x2_0000) 给出 -180 度的相移。 如下表所示。

| NCO Phase | nco_phase |

|---|---|

| -1800 | 0x2_0000 |

| -900 | 0x3_0000 |

| 00 | 0x0_0000 |

| 900 | 0x0_FFFF |

| 1800 | 0x1_FFFF |

nco_update_en 信号用于确定在更新事件中修改了哪些频率和相位字。 nco_update_en 向量中的位设置为高以修改频率和相位编号的以下位。

- Bit 5: Reset the phase offset to 0

- Bit 4: nco_phase[17:16]

- Bit 3: nco_phase[15:0]

- Bit 2: nco_freq[47:32]

- Bit 1: nco_freq[31:16]

- Bit 0: nco_freq[15:0]

例如,如果只有 nco_update_en 的位 2:0 设置为高,则只有频率值在更新事件上发生变化。

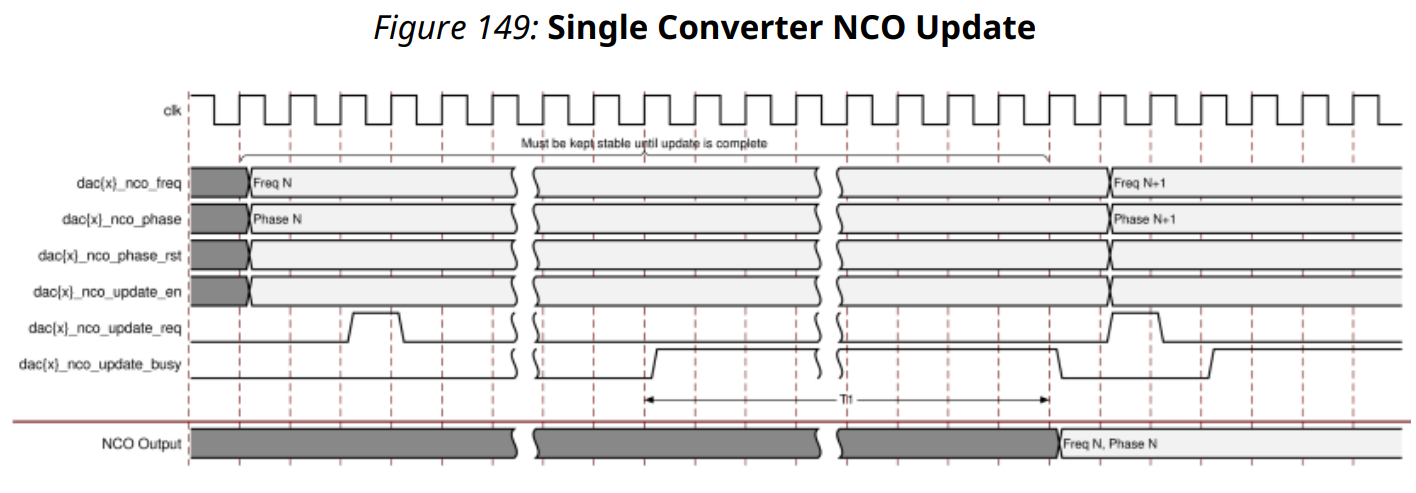

单转换器模式

当不支持多块同步 (MTS) 时,所有转换器都是独立的。 为每个转换器实例化一个 NCO 更新状态机。 在执行 NCO 更新之前,必须将事件源设置为 Tile。更新 NCO 设置的过程如下所示。

- 首先在实时 NCO 信号接口端口上设置所需的频率、相位和相位复位值。

- 设置更新使能端口以指示要更新哪些转换器寄存器值。需要更新的值越多,T1(将 NCO 值写入转换器寄存器的时间)就会增加。 在 RF-DAC 和 Quad RF-ADC 情况下,写入一个寄存器通常需要 29 个 s_axi_aclk 周期。 每增加一次寄存器写入,T1 就会增加三个 s_axi_aclk 周期。在 Dual RF-ADC 情况下,写入一个寄存器通常需要 45 个 s_axi_aclk 周期。 每个额外的寄存器写入都会将 T1 增加六个 s_axi_aclk 周期。

- 然后向更新请求端口发送一个脉冲。 如果 IP 状态机已完成启动过程,则开始访问所请求的 NCO 寄存器。

- 忙信号保持高电平,直到 NCO 更新过程完成。 频率、相位和相位复位值应保持到忙碌信号被取消断言为止。

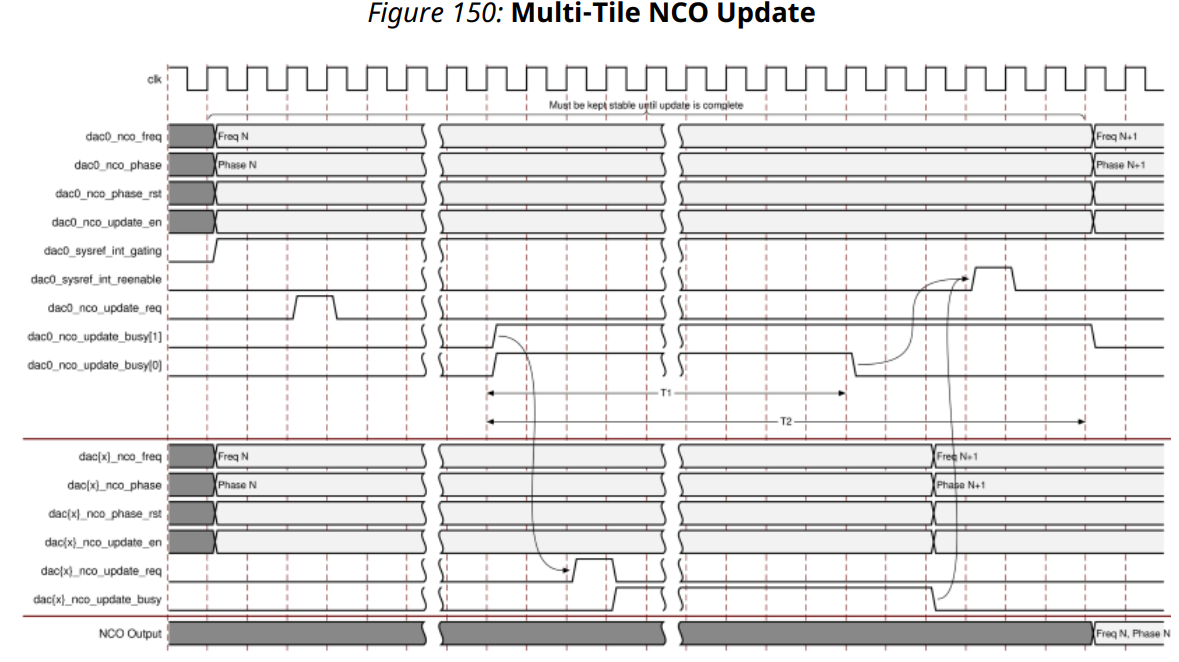

多片模式

选择多块同步时,SYSREF 用于更新 NCO 设置。 这确保了混频器更新在所有转换器之间同步。 在进行 NCO 更新之前,必须将事件源设置为 SYSREF。

因为 SYSREF 用于触发 NCO 更新,所以应该对其进行门控以确保在更新过程中边缘不会到达。 如果 SYSREF 在外部进行门控,则 IP 内核的工作方式与单转换器情况相同。 在第 3 代器件中,您可以通过置位 dac{x}_sysref_gate 实时输入来选择在 IP 内部对 SYSREF 进行门控。 在这种情况下,IP 内核也以与单转换器情况相同的方式工作。 SYSREF 应在 NCO 更新过程开始之前关闭,并在 IP 解除忙信号时重新启用。

如果上述两种 SYSREF 门控方法均未实现,则 IP 内核可以通过写入 RF-DAC tile 0 中的寄存器来内部门控 SYSREF 信号。在这种情况下,更新 NCO 设置的过程如下所示。

- 首先,在需要更新的所有NCO 通道的实时NCO 信号接口端口上设置所需的NCO 频率、相位和相位复位值。 同时更新使能端口 (dac0_update_en, dac{x} _ update_en) 应设置为指示要更新哪些寄存器值。

- 将 dac0_sysref_int_gating 驱动为高电平以向 IP 指示它应该在内部选通 SYSREF。

- 要启动 NCO 更新,请向 dac0_nco_update_req 端口发送一个脉冲。

- 当 IP 接收到更新请求时,它首先等待启动状态机完成,然后执行寄存器写入,以在 RFDAC tile 0 中选通 SYSREF。完成后,它驱动 dac0_nco_update_busy 输出的位 1 高的。

- 然后,您可以为多块同步组 (dac{x}_update_req) 中的其他转换器断言更新请求输入,以通过实时 NCO 信号接口请求它们的 NCO 更新。

- 当多块同步组中转换器的所有更新繁忙输出均为低时,除dac0_nco_update_busy[1] 外,NCO 寄存器写入已完成。 繁忙的输出可以彼此异步取消断言。

- 然后您应该向 dac0_sysref_int_reenable 端口发送一个脉冲,以指示可以重新启动 SYSREF。 当 dac0_nco_update_busy[1] 变为低电平时,该过程完成。

在访问请求的 NCO 寄存器之前,更新过程一直等到 IP 状态机完成启动过程。

需要更新的值越多,将 NCO 值写入寄存器的时间就越长。 这在上图中将 RF-DAC tile 0 显示为 T1。 在 RF-DAC 和 Quad RF-ADC 情况下,写入一个寄存器通常需要 29 个 s_axi_aclk 周期。 每增加一次寄存器写入,T1 就会增加三个 s_axi_aclk 周期。 在 Dual RF-ADC 情况下,写入一个寄存器通常需要 45 个 s_axi_aclk 周期。 每个额外的寄存器写入都会将 T1 增加 6 个 s_axi_aclk 周期。

在上图中,T2 表示从初始寄存器更新开始到该过程完成所用的时间。 该时间取决于 SYSREF 频率、要更新的寄存器值的数量以及 tile 同步组中的转换器数量。

reference

- PG269

相关文章

- 开发者成长激励计划-基于TencentOS Tiny 的隔空手势PAJ7620传感器智能家居控制应用

- Python基础语法-控制流程语句-break

- MySQL与PHP的基础与应用专题之数据控制

- 写控制Linux下CPU大小写控制的技巧(linuxcpu大小)

- 完美定时:Linux 实现精确控制(linux精确定时)

- 控制 Linux下目录权限控制管理(linux目录授权)

- 山东蓝翔不是传说!中国产手持扫描仪被发现携带恶意程序,控制端在山东蓝翔

- Airwheel平衡车开箱体验:用身体控制的代步神器

- Linux下的SMBus控制与应用(smbuslinux)

- GPIO在Linux中的应用:编写驱动程序实现控制(gpio驱动linux)

- Oracle 强制并发:控制复杂应用的威力(oracle强行并发)

- 使用Linux CF命令提高服务器性能控制和应用部署管理。(linuxcf命令)

- 无人机智能控制的前沿技术和产业的应用 | 雷锋网公开课

- Linux掌握Web应用发展之道(linux web 控制)

- Oracle 五种控制语句研究(oracle五种控制语句)

- Oracle事务控制语句示例解析(oracle事物语法示例)

- Oracle灵活使用循环语句控制(oracle中循环的语句)

- 控制研究Redis在权限控制上的应用(redis能不能做权限)

- javascript的键盘控制事件说明

- JS控制小数位数的实现代码

- jquery元素控制(追加元素/追加内容)介绍及应用