设计FIFO深度

设计 深度 FIFO

2023-09-14 09:10:03 时间

设计FIFO深度

假设FIFO的写时钟为100MHZ,读时钟为80MHZ。在FIFO输入侧写数据侧,每100个时钟,写入80个数据,FIFO读出侧每个时钟读出一个数据。设计合理的FIFO深度,使FIFO不会溢出。

如果读出侧每3个时钟读出1个数据,请问FIFO深度又是多少?

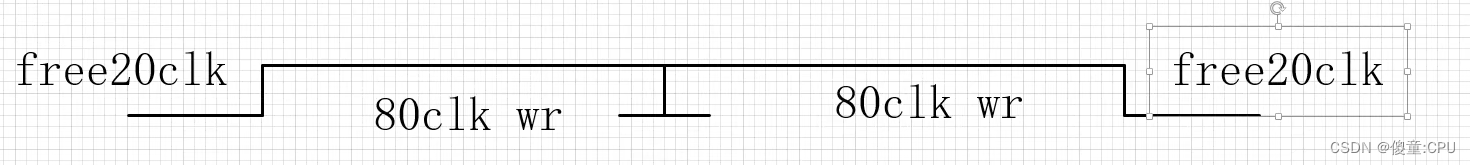

高电平代表写,低电平代表没有写

瞬时带宽最大:背靠背的时钟周期时,数据压力最大。此处就是前100时钟周期的后80个时钟周期写,后100个时钟周期的前80个时钟周期写。

令写和读都是同时启动,写完160个数据时刻,FIFO中剩余x个数据,实际读出的数据就是160-x。写完160数据的时间和读出160-x时间是一致的。(同时读写-就是同时读写)

160*10ns = (160 - x )*12.5ns

x= 32

如果读出侧每3个时钟读出1个数据,请问FIFO深度又是多少?

160*10ns = (160 - x )*12.5 *3/1

x=128

相关文章

- 计算机组成与设计(六)—— 乘法器[通俗易懂]

- 六西格玛设计(DFSS)是什么意思?

- 太酷了!同济大学设计创意学院用Unity3d搭建了一个“元宇宙”毕业展。

- [Nature Communications | 论文简读] ProtGPT2是一个用于蛋白质设计的深度无监督的语言模型

- JCIM丨DRlinker:深度强化学习优化片段连接设计

- 【Android 应用开发】AndroidUI设计之 布局管理器 - 详细解析布局实现

- 【FPGA 芯片设计】FPGA 简介 ( FPGA 芯片架构 | FPGA 芯片相对于传统芯片的优点 )

- navisworks是什么软件?三维设计模型Navisworks软件下载安装教程

- 数字化转型中,如何高效设计业务架构?

- Linux:优雅的设计与体验(linux设计)

- 深度学习Oracle高级数据库设计(高级oracle)

- Intel CPU 曝致命漏洞,Linux、Windows 面临重新设计,云计算厂商全受影响

- 数据库设计探索沈阳:从Oracle数据库设计开始(沈阳oracle)

- Redis乐观锁设计之道(怎么设计redis乐观锁)

- JavaScript面象对象设计