数字IC面试手撕代码(十三)

2023-09-14 09:10:01 时间

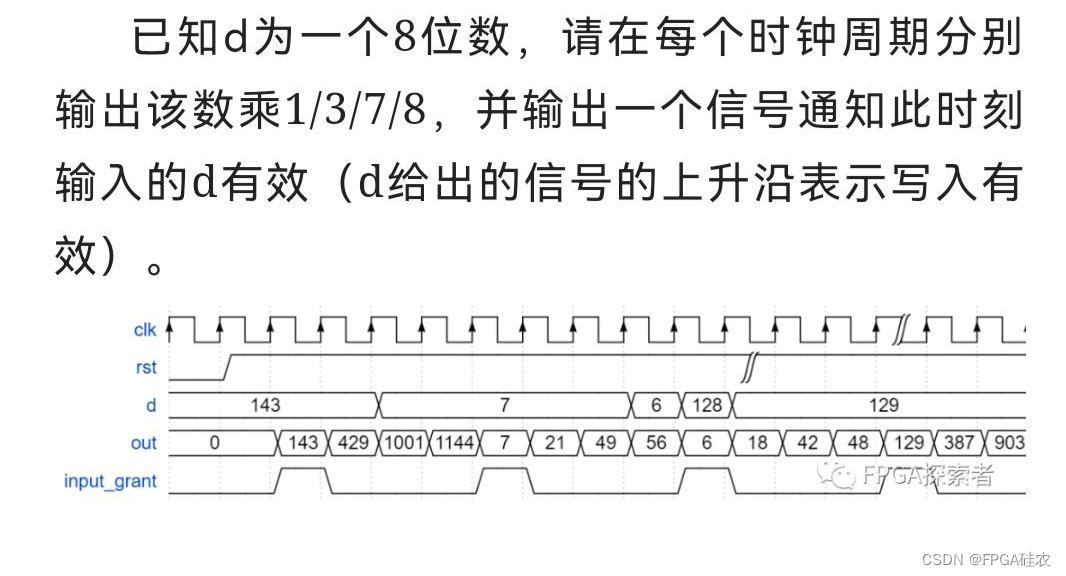

题目

设置一个计数器,从0开始计数,一直计数到3,然后回到0,根据计数器的值,来决定乘以多少,再设置一个valid信号,标志输入数据d有效,首先,复位时valid应该为1,其次,当计数器的值为3的时候,valid也应该为1,当valid为1时,我们还需要寄存输入数据d,即d_r<=d,同时拉高input_grant一个周期。

代码

module top(

input logic clk,

input logic rst,

input logic [7:0] d,

output logic [15:0] out,

output logic input_grant

);

logic [7:0] d_r;

logic valid;

logic [1:0] cnt;

//valid

always_ff@(posedge clk,posedge rst)

if(rst)

valid<=1;

else if(cnt==2)

valid<=1;

else

valid<=0;

//cnt

always_ff@(posedge clk,posedge rst)

if(rst)

cnt<=0;

else if(valid)

cnt<=0;

else if(cnt==4-1)

cnt<=0;

else

cnt<=cnt+1;

//d_r

always_ff@(posedge clk)

if(valid)

d_r<=d;

//out

always_comb

begin

if(rst)

out=0;

else

begin

case(cnt)

2'd0:out=d_r;

2'd1:out=(d_r<<1)+d_r; //x3

2'd2:out=(d_r<<2)+(d_r<<1)+d_r; //x7

2'd3:out=d_r<<3; //x8

endcase

end

end

//input_grant

always_ff@(posedge clk,posedge rst)

if(rst)

input_grant<=0;

else if(valid)

input_grant<=1;

else

input_grant<=0;

endmodule

测试平台

module test;

logic clk;

logic rst;

logic [7:0] d;

logic [15:0] out;

logic input_grant;

//

initial begin

clk=0;

forever begin

#5 clk=~clk;

end

end

//

initial begin

rst=1;

#100

rst=0;

end

//

always_ff@(posedge clk,posedge rst)

if(rst)

d<=0;

else

d<=$urandom%256;

//

initial

begin

$fsdbDumpfile("./top.fsdb");

$fsdbDumpvars(0);

end

//

initial

begin

#10000

$finish;

end

//

top U(.*);

endmodule

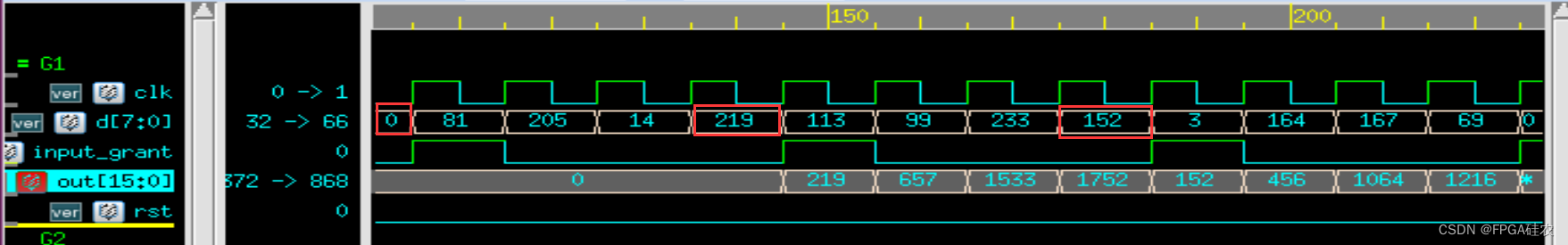

仿真结果

相关文章

- 【002】数字IC笔面试常见题

- 【006】数字IC笔面试常见题

- 【009】数字IC笔面试常见题

- 永嘉微单键多键智能开关触摸控制芯片(IC)-VK36Q4开关智能控制器IC

- 你知道吗?印度IC工程师费用这么低!

- 2023届数字IC面经 | 有流片经验就是“乱杀”?

- 沪漂日记 | 16. 做IC的到底算不算程序员

- 世微AP51656 60V高端电流采样降压恒流驱车灯IC

- HX4004A/HX4004/FS2115(电荷泵DC/DC升压转换IC)

- InCopy下载 Adobe InCopy 2023版本安装教程 ——IC技巧

- 超低功耗LCD液晶显示驱动芯片(IC)-VKL128-稳定性好,超低工作电流,低休眠电流-技术开发资料

- AP6317 同步3A锂电充电IC 带散热 便携式设备 充电器

- 探路者拟以3852万美元收购触控IC厂商G2 Touch 72.79%股权

- 锂电池3.7V升5V/5A内置MOS大电流升压IC型号推荐FS2116B

- AP3464 车充 适配器IC 4-30V 2.4A 同步降压恒压 恒流驱动器

- HM9230原厂升压IC规格书PDF资料

- AP3301 DC-DC降压IC 0.6-5.5V 高效率 低功耗 监控驱动应用