优先编码器

优先 编码器

2023-09-14 09:10:03 时间

优先编码器

题目描述

8-3优先编码器的功能表

`timescale 1ns/1ns

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

reg [2:0]Y_reg;

reg GS_reg;

reg EO_reg;

always@(*)

begin

if(EI == 1'b0)

begin

Y_reg = 3'b0;

GS_reg = 1'b0;

EO_reg = 1'b0;

end

else begin

casez(I) //casex(I)

8'b0000_0000:begin

Y_reg = 3'b0;

GS_reg = 1'b0;

EO_reg = 1'b1;

end

8'b1???_????:begin

Y_reg = 3'b111;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b01??_????:begin

Y_reg = 3'b110;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b001?_????:begin

Y_reg = 3'b101;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b0001_????:begin

Y_reg = 3'b100;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b0000_1???:begin

Y_reg = 3'b011;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b0000_01??:begin

Y_reg = 3'b010;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b0000_001?:begin

Y_reg = 3'b001;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

8'b0000_0001:begin

Y_reg = 3'b000;

GS_reg = 1'b1;

EO_reg = 1'b0;

end

default:begin

Y_reg = 3'b0;

GS_reg = 1'b0;

EO_reg = 1'b0;

end

endcase

end

end

assign Y = Y_reg;

assign GS = GS_reg;

assign EO = EO_reg;

endmodule

知识点

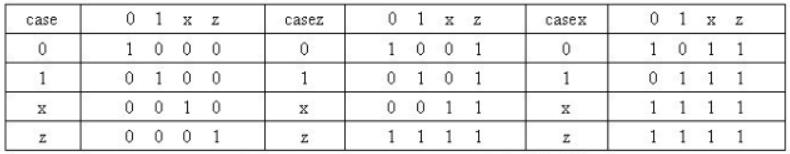

case,casex,casez的真值表

在case语句中,敏感表达式中与各项值之间的比较是一种全等比较,每一位都相同才认为匹配。

在casez语句中,如果分支表达式某些位的值为高阻z,那么对这些位的比较就会忽略,不予考虑,而只关注其他位的比较结果。

在casex语句中,则把这种处理方式进一步扩展到对x的处理,即如果比较双方有一方的某些位的值是z或x,那么这些位的比较就不予考虑。

1)一般经常使用到的是casez语句,最好少用casex

2)case/casez/casex其实都是可综合的

3)在电路中,可以用?来表示无关值的z

4)case的描述,匹配都是从上到下进行的