含有无关项的序列检测

序列 检测 含有 无关

2023-09-14 09:10:03 时间

含有无关项的序列检测

题目描述

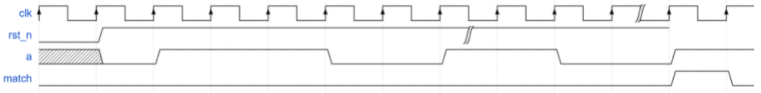

请编写一个序列检测模块,检测输入信号a是否满足011XXX110序列(长度为9位数据,前三位是011,后三位是110,中间三位不做要求),当信号满足该序列,给出指示信号match。

程序的接口信号图如下:

程序的功能时序图如下:

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

parameter idle = 8'b00000001;

parameter state1 = 8'b00000010;

parameter state2 = 8'b00000100;

parameter state3 = 8'b00001000;

parameter state4 = 8'b00010000;

parameter state5 = 8'b00100000;

parameter state6 = 8'b01000000;

parameter state7 = 8'b10000000;

reg [0:7] c_state,n_state;

reg [0:1] cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

c_state <= idle;

else

c_state <= n_state;

end

always@(*)

begin

case(c_state)

idle:begin

if(a == 0)

n_state = state1;

else

n_state = idle;

end

state1:begin

if(a == 1)

n_state = state2;

else

n_state = state1;

end

state2:begin

if(a == 1)

n_state = state3;

else

n_state = state1;

end

state3:begin

if(cnt == 2)

n_state = state4;

else

n_state = state3;

end

state4:begin

if(a == 1)

n_state = state5;

else

n_state = state1;

end

state5:begin

if(a == 1)

n_state = state6;

else

n_state = state1;

end

state6:begin

if(a == 0)

n_state = state7;

else

n_state = idle;

end

state7:begin

if(a == 1)

n_state = idle;

else

n_state = state1;

end

default:n_state = idle;

endcase

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 2'b0;

else if(c_state == state3 && cnt == 2'd3)

cnt <= 2'b0;

else if(c_state == state3)

cnt <= cnt + 1'b1;

else

cnt <= 2'b0;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

match <= 1'b0;

else if(c_state == state7)

match <= 1'b1;

else

match <= 1'b0;

end

endmodule

相关文章

- SIGIR'21 因果推断+序列推荐:反事实数据促进鲁棒用户表征生成

- PTA -7-51 两个有序链表序列的合并(C++)

- 经济学:动态模型平均(DMA)、动态模型选择(DMS)、ARIMA、TVP预测原油时间序列价格|附代码数据

- 召回和排序模型中的用户行为序列的建模

- 9个时间序列交叉验证方法的介绍和对比

- 极值分析:分块极大值BLOCK-MAXIMA、阈值超额法、广义帕累托分布GPD拟合降雨数据时间序列|附代码数据

- SQLServer 错误 17194 服务器无法加载登录所需的 SSL 提供程序库;连接已关闭。 可以用 SSL 对登录序列或所有通信进行加密,具体取决于管理员配置服务器的方式。 有关以下错误消息的信息,请参阅联机丛书:0xXXXX。 [客户端:11.11.11.11] 故障 处理 修复 支持远程

- postgresql 实现更新序列的起始值

- 值Oracle取序列值的简单操作(oracle取序列)

- Oracle主键序列生成自动唯一标识(oracle 主键 序列)

- Mysql 自创序列:自主调整更高效能(mysql 自定义序列)

- Oracle序列助您的数据更具唯一性(oracle关于序列说法)

- Oracle传递建立序列(oracle传建序列)

- 在Oracle中使用序列实现声明的功能(oracle中声明序列)

- perl指定长度并生成一个随机的DNA序列的脚本代码