状态机与时钟分频

时钟 状态机

2023-09-14 09:10:02 时间

状态机与时钟分频

题目描述

使用状态机实现时钟分频,要求对时钟进行四分频,占空比为0.25

信号示意图

题目解读

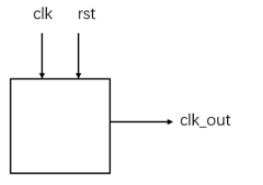

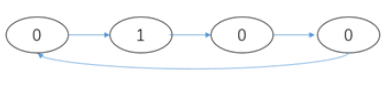

首先考虑输入输出,作为分频电路,有一个时钟输入端,clk,输出端div3,再加一个复位端(这里不加也可)所以输入 clk,rst输出 clk_out再考虑状态转换的问题。4分频占空比0.25,可以为0100或1000都行。

在时钟的作用下,应该不停的在这四种状态下转换,并且输出仅仅依赖于当前的状态,所有的整数分频器都可以按照次方法来实现。

`timescale 1ns/1ns

module huawei7(

input wire clk ,

input wire rst ,

output reg clk_out

);

parameter[1:0] S0=2'd0,

S1=2'd1,

S2=2'd2,

S3=2'd3;

reg[1:0] state,next_state;

always @ (posedge clk or negedge rst)

begin

if(!rst) state<=S0;

else state<= next_state;

end

always @ (state)

begin

相关文章

- CDC不考虑时钟关系可以吗?

- 京准PTP时钟同步服务器如何应用智能驾驶系统

- 年月日软件测试用例的设计,时钟——黑盒测试用例设计实例

- 电子时钟代码

- iOS锁屏时钟_ios时钟怎么调

- (九)51单片机——DS1302时钟

- 使用 Web Animations API 实现一个精确计时的时钟

- 【嵌入式开发】时钟初始化 ( 时钟相关概念 | 嵌入式时钟体系 | Lock Time | 分频参数设置 | CPU 异步模式设置 | APLL MPLL 时钟频率设置 )

- Linux下的时钟同步服务的实施(linux时钟同步服务)

- Linux系统时钟频率解析(系统时钟频率linux)

- Linux时钟管理:简易、精准、方便(linux时钟管理)

- TextView显示系统时间(时钟功能带秒针变化