关键路径的分析

分析 路径 关键

2023-09-14 09:10:02 时间

关键路径的分析

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计起决定性影响的时序路径。

对关键路径进行时序优化,可以直接提高设计设计性能。对同步逻辑来说,常用的时序优化方法包括Pipeline、Retiming、逻辑复制、加法/乘法树、关键信号后移、消除优先级等解决。

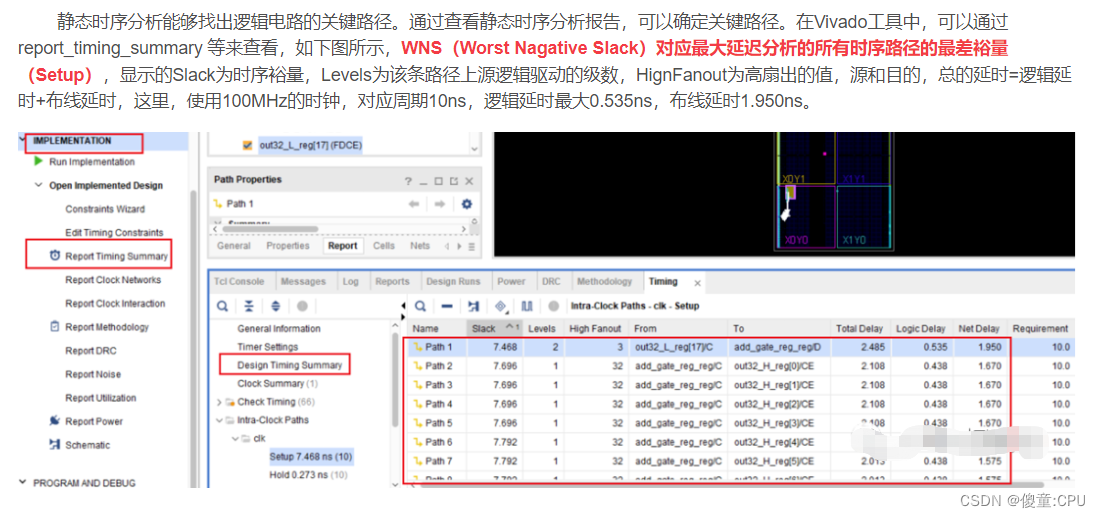

静态时序分析能够找出逻辑电路的关键路径。通过查看静态时序分析报告,可以确定关键路径。

1、组合逻辑中插入寄存器(插入流水线)

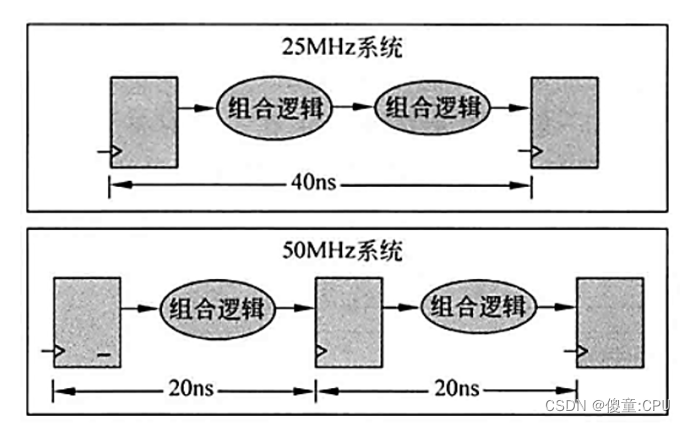

组合逻辑的延时过长,就会成为关键路径,这时可以考虑在该路径上插入额外的寄存器,这种方法也称为插入流水线,多用于高度流水的设计中,因为这种设计中额外插入寄存器增加的时钟周期延时并不会违反整个设计的规范要求,从而不会影响设计的总体功能性实现,也即额外插入的寄存器在保持吞吐量不变的情况下改善了设计的时序性能。当然,其不可避免地会带来部分面积的加。

在插入寄存器时,要在组合逻辑中选择合适的位置进行插入,使得插入寄存器后被分割出的几块小的组合逻辑延时基本一致。

相当于下图所示的先加入寄存器,再对寄存器进行重定时Retiming。

相关文章

- 基于基站定位的商圈分析

- 软件测试缺陷报告_软件测试缺陷分析

- 【经验科普】实战分析C工程代码可能遇到的编译问题及其解决思路

- 基于求解器的路径规划算法实现及性能分析

- R语言有极值(EVT)依赖结构的马尔可夫链(MC)对洪水极值分析|附代码数据

- 【Android 安装包优化】资源混淆 ( resources.arsc 资源映射表混淆 | resources.arsc 资源映射表二进制格式分析 | 混淆全局字符串池和资源名称字符串池 )

- 【Java 并发编程】线程池机制 ( 线程池执行任务细节分析 | 线程池执行 execute 源码分析 | 先创建核心线程 | 再放入阻塞队列 | 最后创建非核心线程 )

- 【Linux 内核 内存管理】物理分配页 ④ ( __alloc_pages_nodemask 函数源码分析 | 快速路径 | 慢速路径 | get_page_from_freelist 源码 )

- 【Android Gradle 插件】Gradle 依赖管理 ⑥ ( dependencies 依赖查找路径 | dependencies 依赖冲突 | dependencies 依赖库层级分析 )

- 网站日志分析:ip地址出现次数统计

- 分析Linux服务器日志分析:实现优化运维效率(linux服务器日志)

- 特斯拉再曝摄像头高清画面:一举一动都在“被分析”

- ELK实时日志分析平台部署搭建详细实现过程

- 分析Linux消息队列:从实例分析学习(linux消息队列实例)

- MySQL测试数据库:简单快捷的稳定性分析(mysql 测试数据库)

- phpSQLite学习笔记与常见问题分析