数字IC面试手撕代码(十四)

2023-09-14 09:10:01 时间

题目描述

设计一个自动贩售机,输入货币有三种,为0.5/1/2元,饮料价格是1.5元,要求进行找零,找零只会支付0.5元。

注意rst为低电平复位,下面是该设计的相关信号及其含义:

本题和文章最大的不同是,之前的文章采用米勒状态机进行设计,而本文则通过摩尔状态机进行设计。采用摩尔状态机时,状态数应该为

S0_0:已投入0元

S0_5:已投入0.5元

S1_0:已投入1元

S1_5:已投入1.5元

S2_0:已投入2元

S2_5:已投入2.5元

S3_0:已投入3元(2+1=3)

这里和米勒状态机最大的区别就是,米勒状态机最大的值为max(投入钱数%1.5),而摩尔状态机的最大值为最大投入钱数(2+1=3)。

代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/05/24 18:52:03

// Design Name:

// Module Name: top_moore

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module seller_moore(

input wire clk ,

input wire rst ,

input wire d1 ,

input wire d2 ,

input wire d3 ,

output reg out1,

output reg [1:0]out2

);

localparam S0_0=0;

localparam S0_5=1;

localparam S1_0=2;

localparam S1_5=3;

localparam S2_0=4;

localparam S2_5=5;

localparam S3_0=6; //1+2=3

reg [3:0] cs,ns;

//fsm1

always@(posedge clk,negedge rst)

if(~rst)

cs<=S0_0;

else

cs<=ns;

//fsm2

always@(*)

case(cs)

S0_0:if(d1)

ns=S0_5;

else if(d2)

ns=S1_0;

else if(d3)

ns=S2_0;

else

ns=S0_0;

S0_5:if(d1)

ns=S1_0;

else if(d2)

ns=S1_5;

else if(d3)

ns=S2_5;

else

ns=S0_5;

S1_0:if(d1)

ns=S1_5;

else if(d2)

ns=S2_0;

else if(d3)

ns=S3_0;

else

ns=S1_0;

S1_5,S2_0,S2_5,S3_0:if(d1)

ns=S0_5;

else if(d2)

ns=S1_0;

else if(d3)

ns=S2_0;

else

ns=S0_0;

default:ns=S0_0;

endcase

//out1

always@(posedge clk,negedge rst)

if(~rst)

out1<=0;

else if(ns==S1_5||ns==S2_0||ns==S2_5||ns==S3_0)

out1<=1;

else

out1<=0;

//out2

always@(posedge clk,negedge rst)

if(~rst)

out2<=2'b00;

else

case(ns)

S1_5:out2<=0;

S2_0:out2<=1;

S2_5:out2<=2;

S3_0:out2<=3;

default:out2<=0;

endcase

endmodule

仿真平台如下

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/05/24 12:32:00

// Design Name:

// Module Name: test_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test_tb;

reg clk;

reg rst;

reg d1,d2,d3;

wire out1;

wire [1:0] out2;

//

initial

begin

clk=0;

forever

#5 clk=~clk;

end

initial

begin

{d1,d2,d3}=3'b000;

rst=0;

#10

rst=1;

#20

@(posedge clk); {d1,d2,d3}<=3'b100;

@(posedge clk); {d1,d2,d3}<=3'b000;

#50

@(posedge clk); {d1,d2,d3}<=3'b010;

@(posedge clk); {d1,d2,d3}<=3'b000;

#30

@(posedge clk); {d1,d2,d3}<=3'b100;

@(posedge clk); {d1,d2,d3}<=3'b000;

#60

@(posedge clk); {d1,d2,d3}<=3'b100;

@(posedge clk); {d1,d2,d3}<=3'b000;

#50

@(posedge clk); {d1,d2,d3}<=3'b001;

@(posedge clk); {d1,d2,d3}<=3'b000;

#50

@(posedge clk); {d1,d2,d3}<=3'b001;

@(posedge clk); {d1,d2,d3}<=3'b000;

#30

@(posedge clk); {d1,d2,d3}<=3'b100;

@(posedge clk); {d1,d2,d3}<=3'b000;

#60

@(posedge clk); {d1,d2,d3}<=3'b001;

@(posedge clk); {d1,d2,d3}<=3'b000;

#50

@(posedge clk); {d1,d2,d3}<=3'b010;

@(posedge clk); {d1,d2,d3}<=3'b000;

#60

@(posedge clk); {d1,d2,d3}<=3'b010;

@(posedge clk); {d1,d2,d3}<=3'b000;

#40

@(posedge clk); {d1,d2,d3}<=3'b100; //投0.5

@(posedge clk); {d1,d2,d3}<=3'b000;

#10

@(posedge clk); {d1,d2,d3}<=3'b010; //投1.0

@(posedge clk); {d1,d2,d3}<=3'b001; //紧接着投2.0

@(posedge clk); {d1,d2,d3}<=3'b000;

#20 $finish;

end

//

//`timescale 1ns/1ns

seller_moore U(

.clk(clk) ,

.rst(rst) ,

.d1(d1) ,

.d2(d2) ,

.d3(d3) ,

.out1(out1),

.out2(out2)

);

endmodule

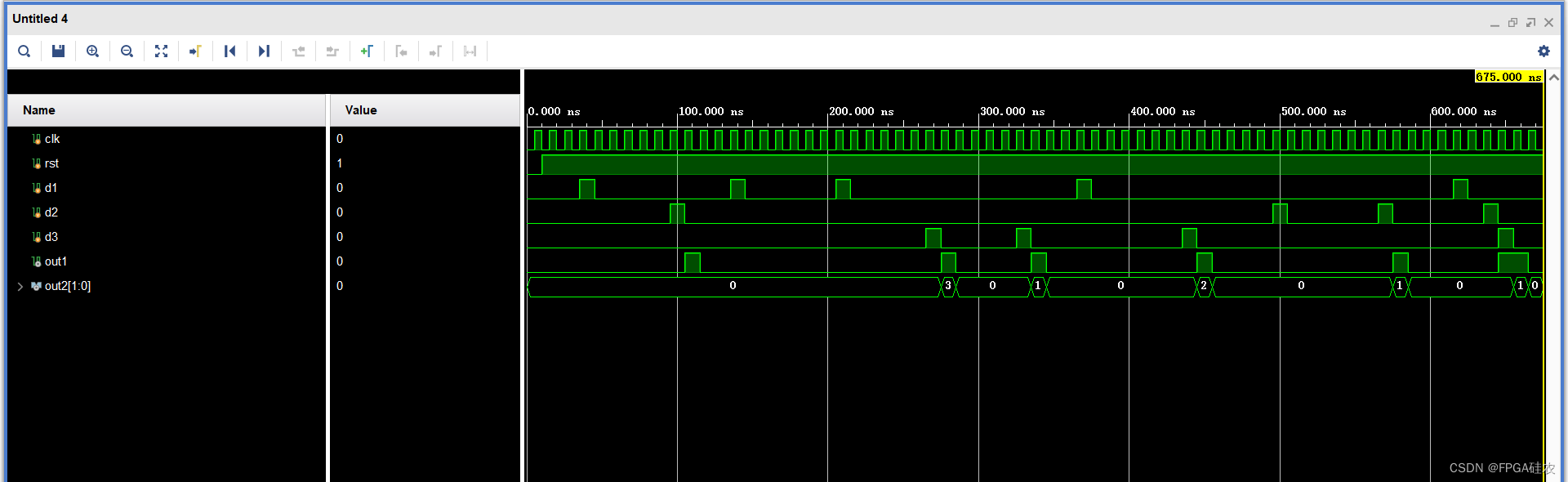

结果

仿真波形如下所示

相关文章

- IC设计基础 | 数字IC设计经典笔试题

- 你知道吗?印度IC工程师费用这么低!

- IC验证入门基础01-Vim的配置

- 从材料到IC验证,是逃难还是人生的机遇?

- 深圳世微补光灯 恒流调光IC调光深度0.1%无频闪

- IC面试:你很优秀,但是对不起

- 关于电源驱动ap8215升压IC的应用

- 世微宽电压 9-100V 2.6A 降压恒流驱动IC LED车灯方案

- 联电携手Cadence共同开发3D-IC混合键合参考流程

- FS2115A无电感锂电池升压IC输出3.3V和输出5V无需电感的升压芯片

- 元宇宙价值链上IC“起舞”,政策热情传至“区县”一级

- AP5160 LED 2.5-100V 7.5A 降压恒流驱动IC 效率高 省空间

- 超低功耗LCD液晶显示驱动芯片(IC)-VKL128-稳定性好,超低工作电流,低休眠电流-技术开发资料

- HM9230原厂升压IC规格书PDF资料