野火A7学习第六次(计数器相关)

学习 相关 计数器

2023-09-14 09:09:12 时间

1 基础概念

2 实战指南

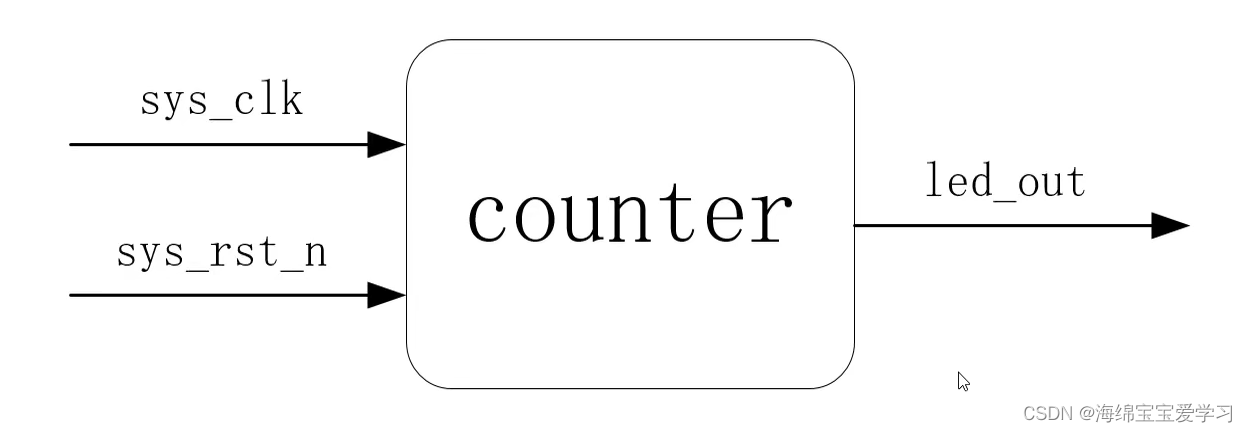

2.1 设计规划

1 设计要求

2 基础规划

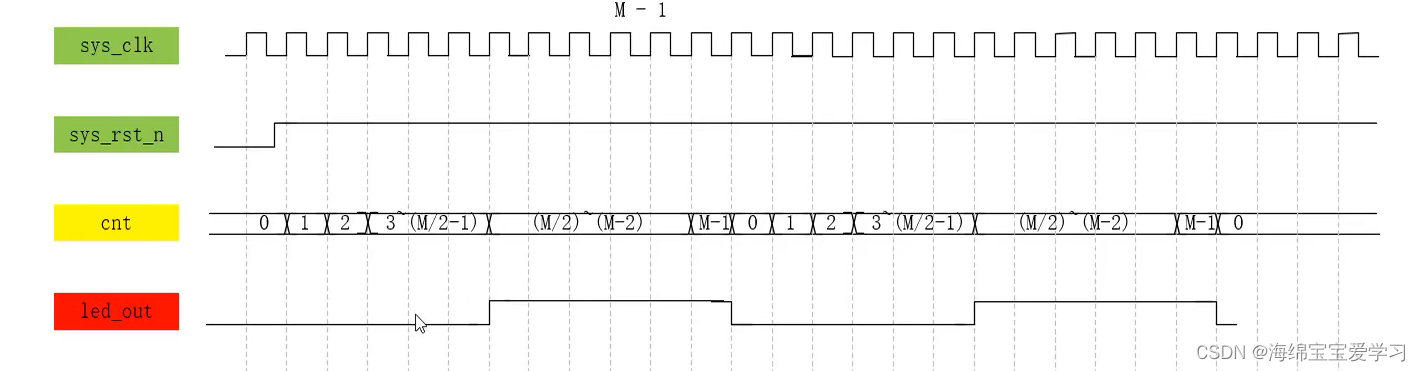

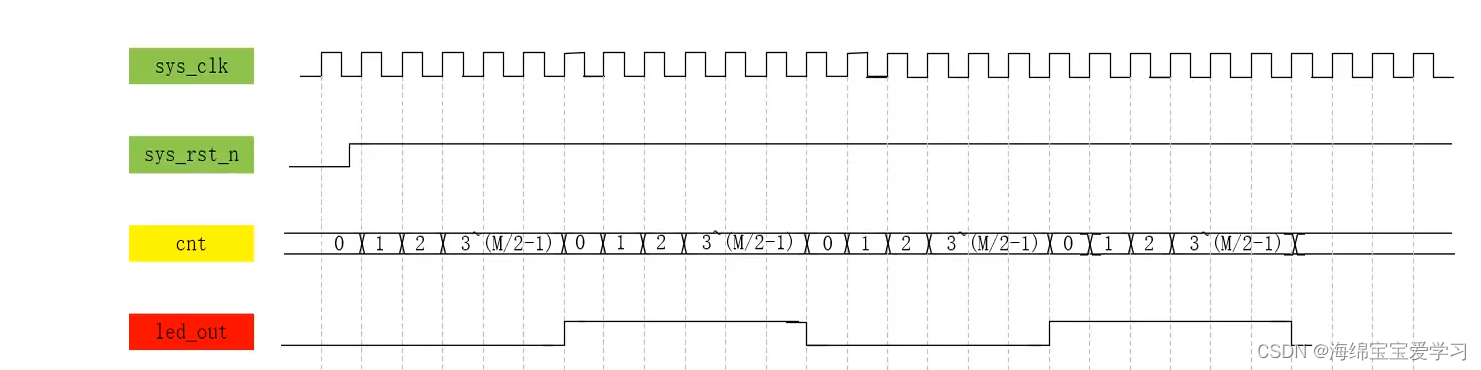

2.2 波形绘制

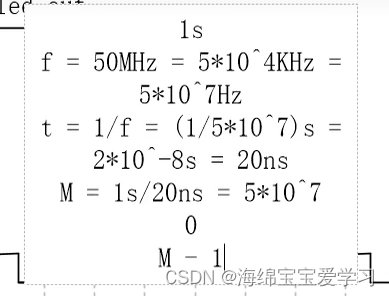

计算

方法1:计数器位宽26

方法二:计数器位宽25

2.3 代码编写和调试

module counter

(

input wire sys_clk,

input wire sys_rst_n,

output wire led_out

);

parameter CNT_MAX = 25'd 24_999_999; // localparam 只能用于 模块内部使用。parameter 可以从module中入口修改参数,使用#(CNT=1000)counter 例化

reg [24:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 25'd0;

else if(cnt == CNT_MAX)

cnt <= 25'd0;

else

cnt <= cnt + 1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

led_out <= 1'b0;

else if(cnt == CNT_MAX)

led_out <= ~ led_out;

else // 如果无效 保持原来的电平

led_out <= led_out;

endmodule

`timescale 1ns/1ns

module tb_counter();

reg sys_clk;

reg sys_rst_n;

wire led_out;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk =~sys_clk;

counter

#(

.CNT_MAX(24)

) counter_inst

(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.led_out(led_out)

);

endmodule

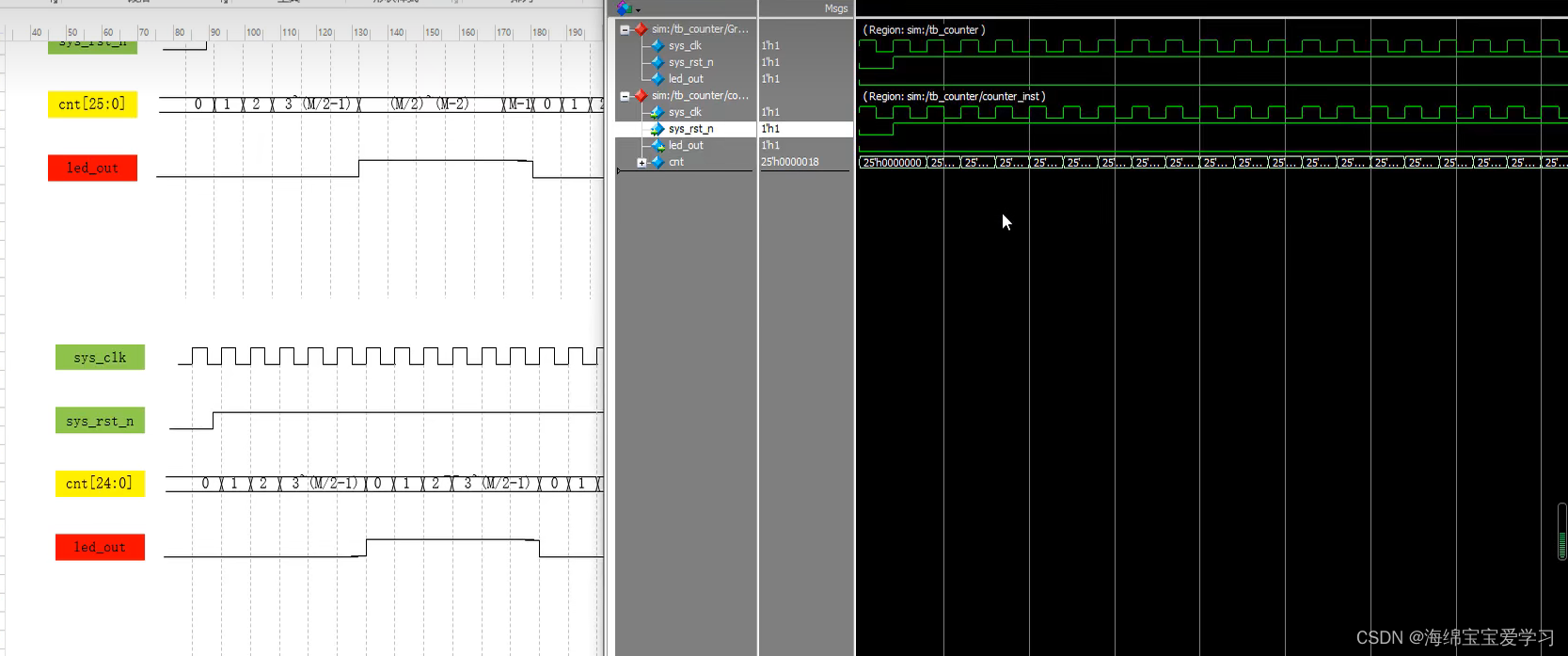

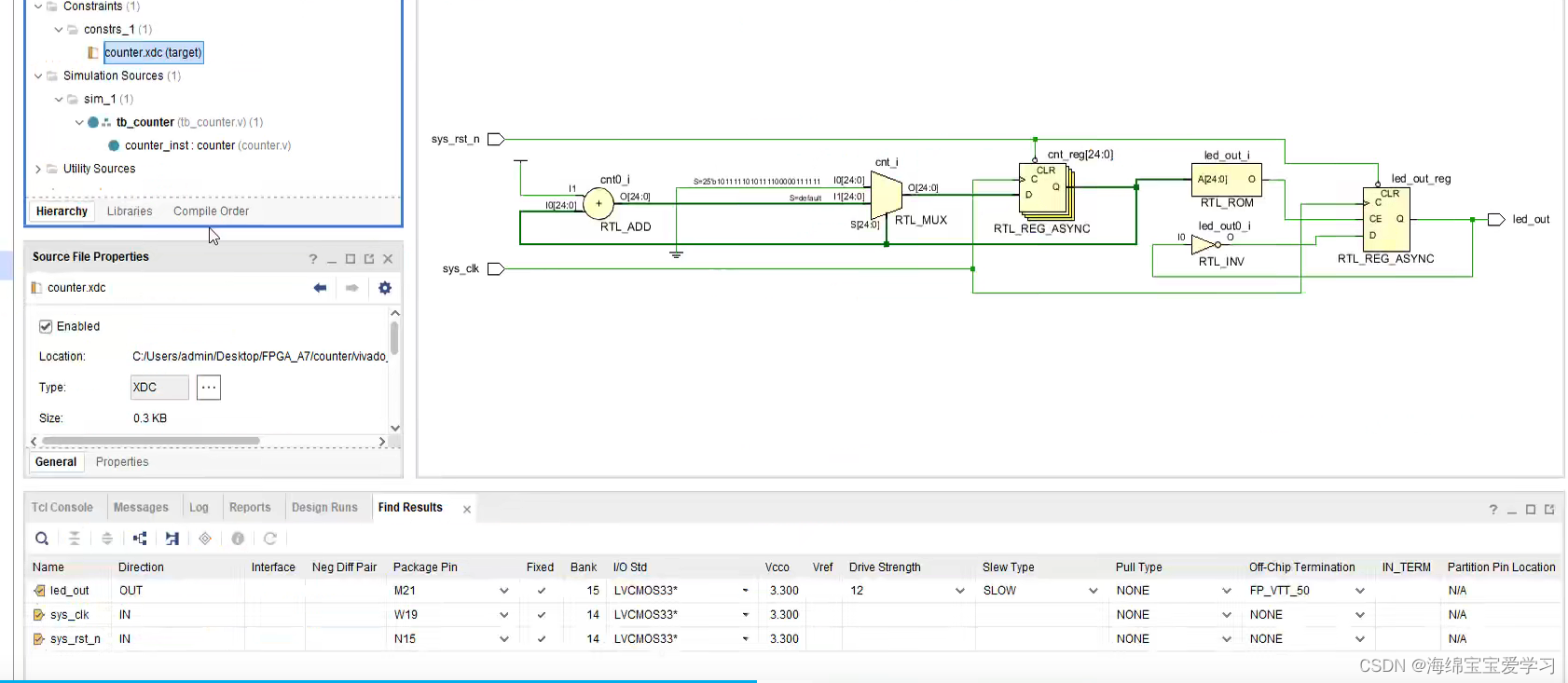

2.4 逻辑仿真和波形对比

2.5 锁定管脚和上板测试

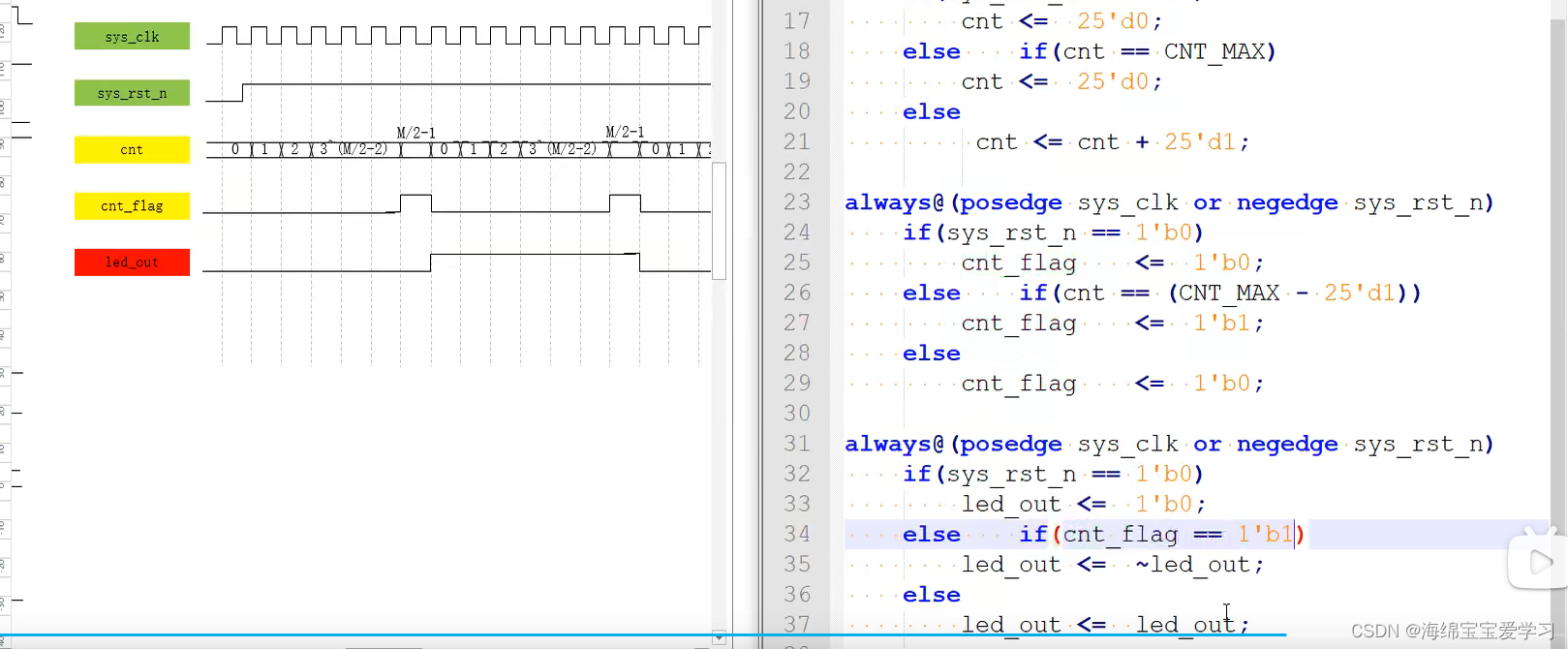

2.6 修改一下,添加一个合理的 脉冲标志信号

相关文章

- 《Head First Servlet JSP》学习笔记

- java struts2入门学习实例--使用struts2快速实现上传

- 【学习总结】Git学习-参考廖雪峰老师教程三-创建版本库

- H3CNE学习---dhcp、telnet、ssh、ftp

- 机器学习笔记 - 大数据定义及相关工具

- 【目录】数据挖掘与机器学习相关算法文章总目录

- Python语言学习:Python语言学习之硬件交互应用(arduino、树莓派等)相关的简介、案例应用之详细攻略

- AI之DS/CV/NLP:Python与人工智能相关的库/框架(机器学习常用库、数据科学常用库、深度学习常用库、计算机视觉常用库、自然语言处理常用库)的简介、案例应用之详细攻略

- Python学习64:ThreadLocal

- Java学习路线-57:静态代理和动态代理

- 设计模式学习笔记-简单工厂模式

- 深度学习中的互信息:无监督提取特征

- 野火A7学习第十次(状态机相关)

- 野火A7学习第九次(流水灯和呼吸灯相关)

- 野火A7学习第五次(时序逻辑相关)

- K近邻算法学习

- cocos2dx游戏开发——微信打飞机学习笔记(二)——游戏框架

- springMVC学习笔记

- 【文献学习】利用DeepLearning实现OFDM信号解调相关文献及源码汇总

- Arduino-学习笔记及相关实验例程

- 【ML吴恩达】2 Python的机器学习相关库libraries

- Android JNI学习-线程相关操作

- 电力系统强大的CVX学习(Matlab&Python)

- 机器学习入门(四)逻辑回归