Vitis嵌入式入门-------输出“hello world“(一)

欢迎━(`∀´)ノ亻!关注公众号,获取更多资料,以及有什么问题都可以通过公众号来问我

在开始vitis中进行嵌入式编程的时候,我们需要在Vivado里面进行硬件的配置,配置后,会成对应的硬件信息,然后再到vitis里面进行程序的编写,程序的编写是基于此硬件信息来的, 硬件信息的不同,程序的编写也会不同**(特定部分**),例如硬件生成的头文件中会多出来一些变量和宏定义。

一. 创建Vivado工程

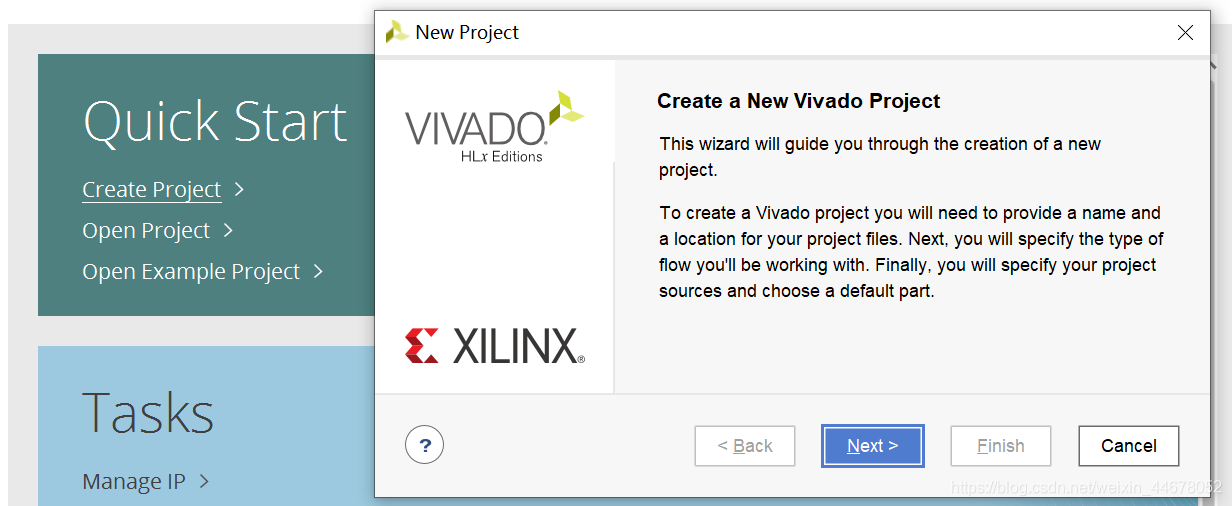

1.打开vivado软件,点击create project,然后点击next

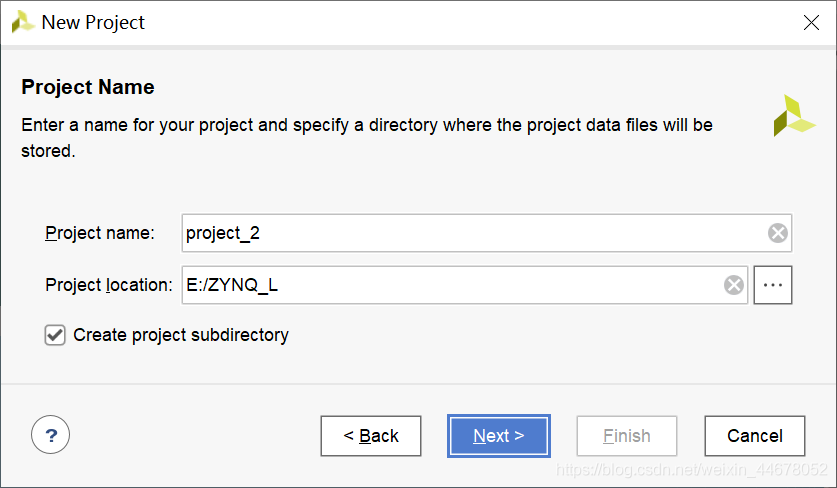

2. 输入工程的名字和选择工程存放的路径

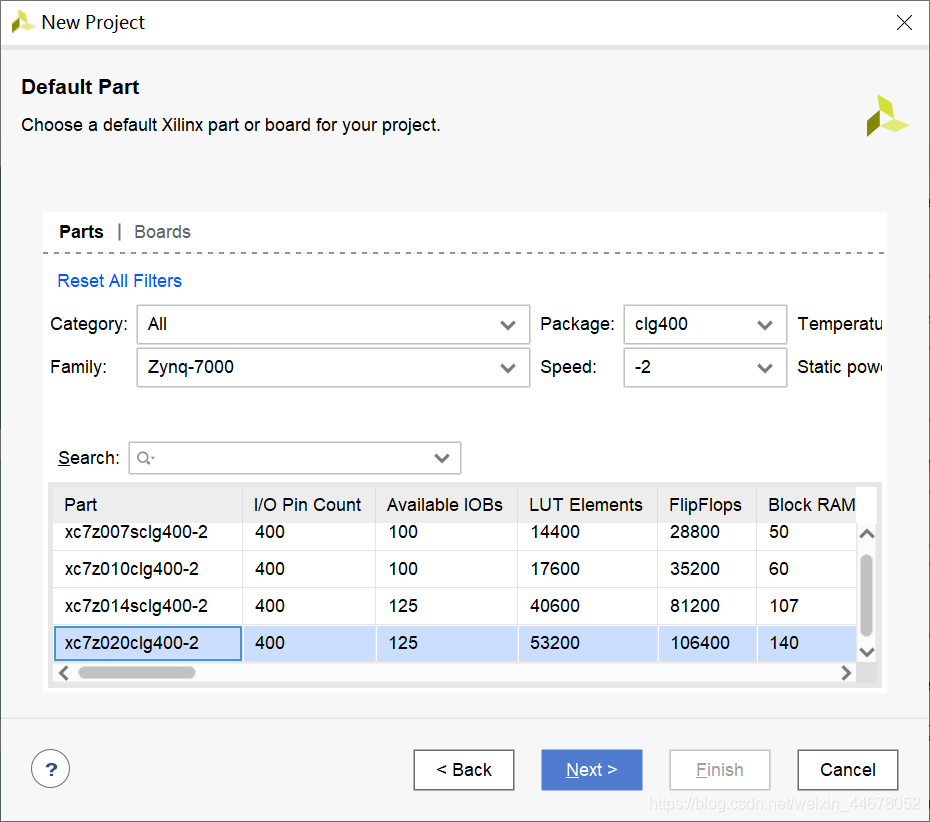

3. 一直点击到如下界面,选择自己开发板上所对应的型号,图中是ZYNQ7020,所family选择zynq-7000,package选择 clg400 ,speed选择-2,这是我的芯片型号,选择这几项的话,会缩小查找的范围,最后点击next

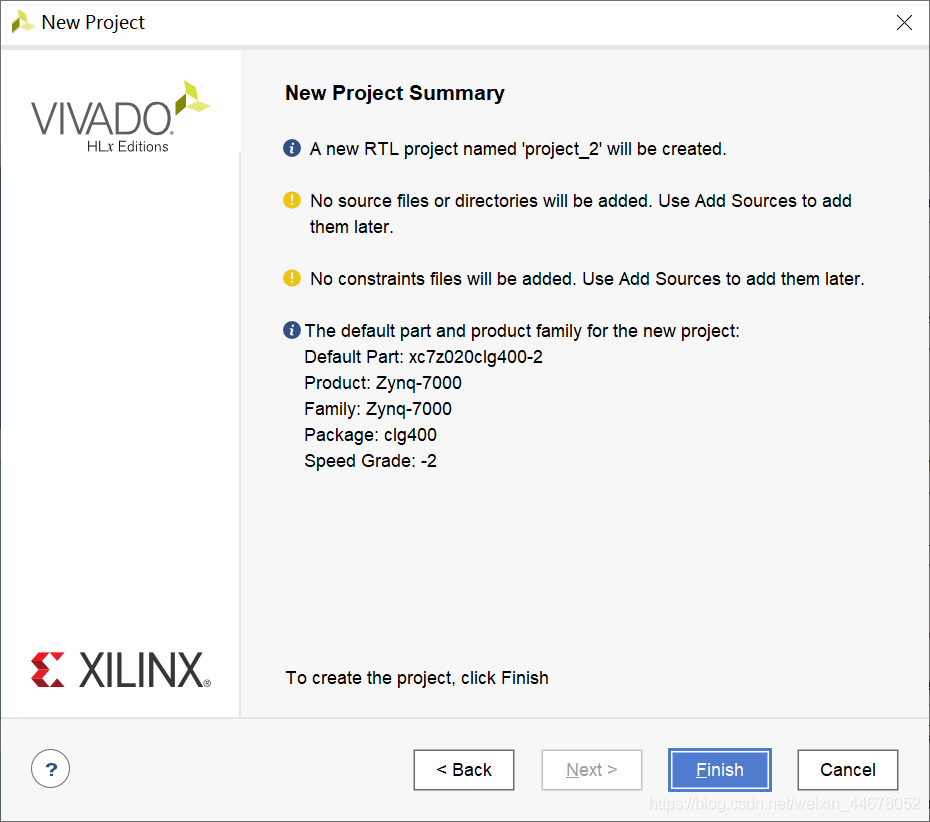

4. 创建成功,点击finish即可

二.配置硬件环境

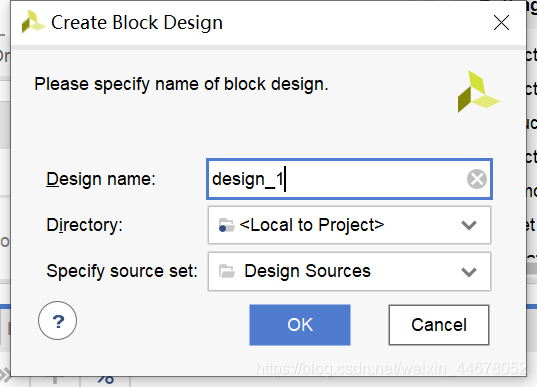

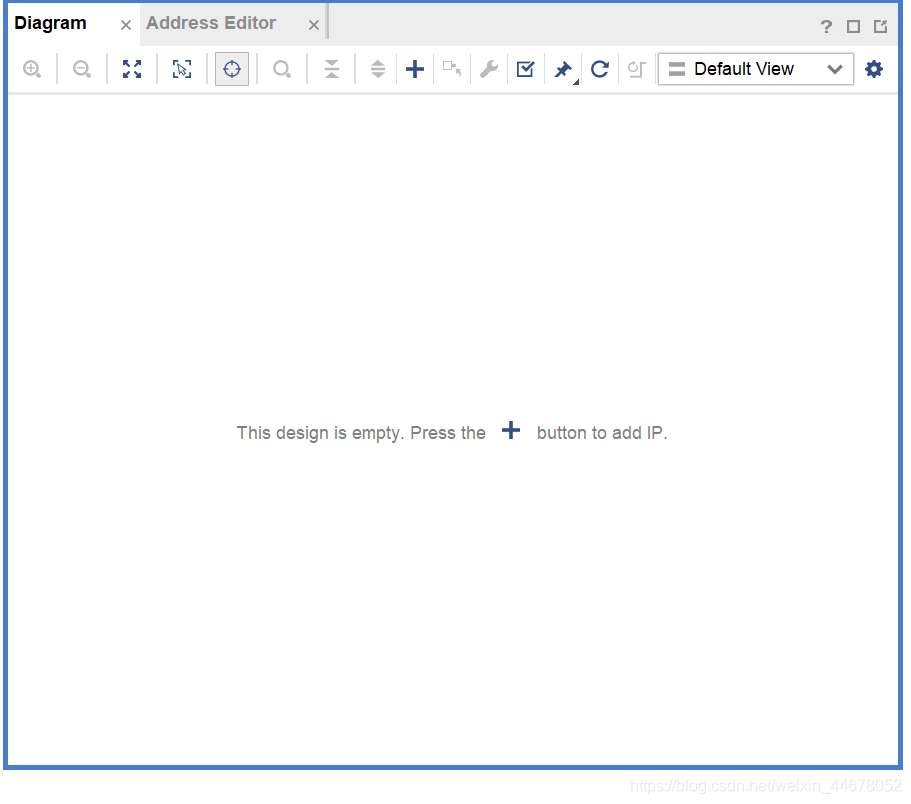

- 创建block,点击create block design,然后输入block的名字,确认后,就可以看到Diagram的窗口了

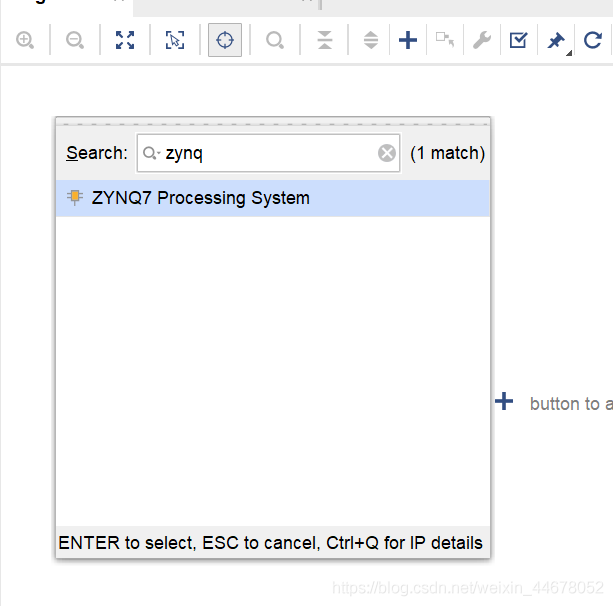

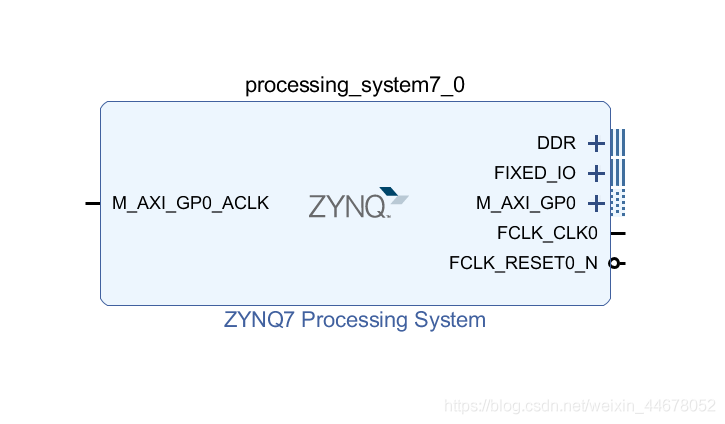

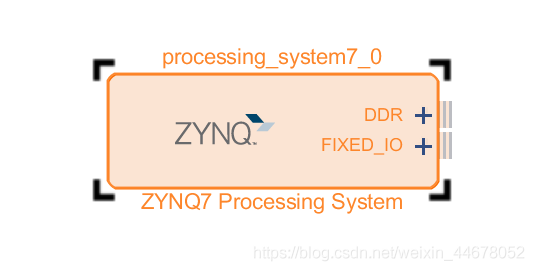

- 然后点击+号,输入zynq,选择ZYNQ7,然后会在窗口中央出现zynq7处理器,可以看到上面有些端口,这些是默认的端口。

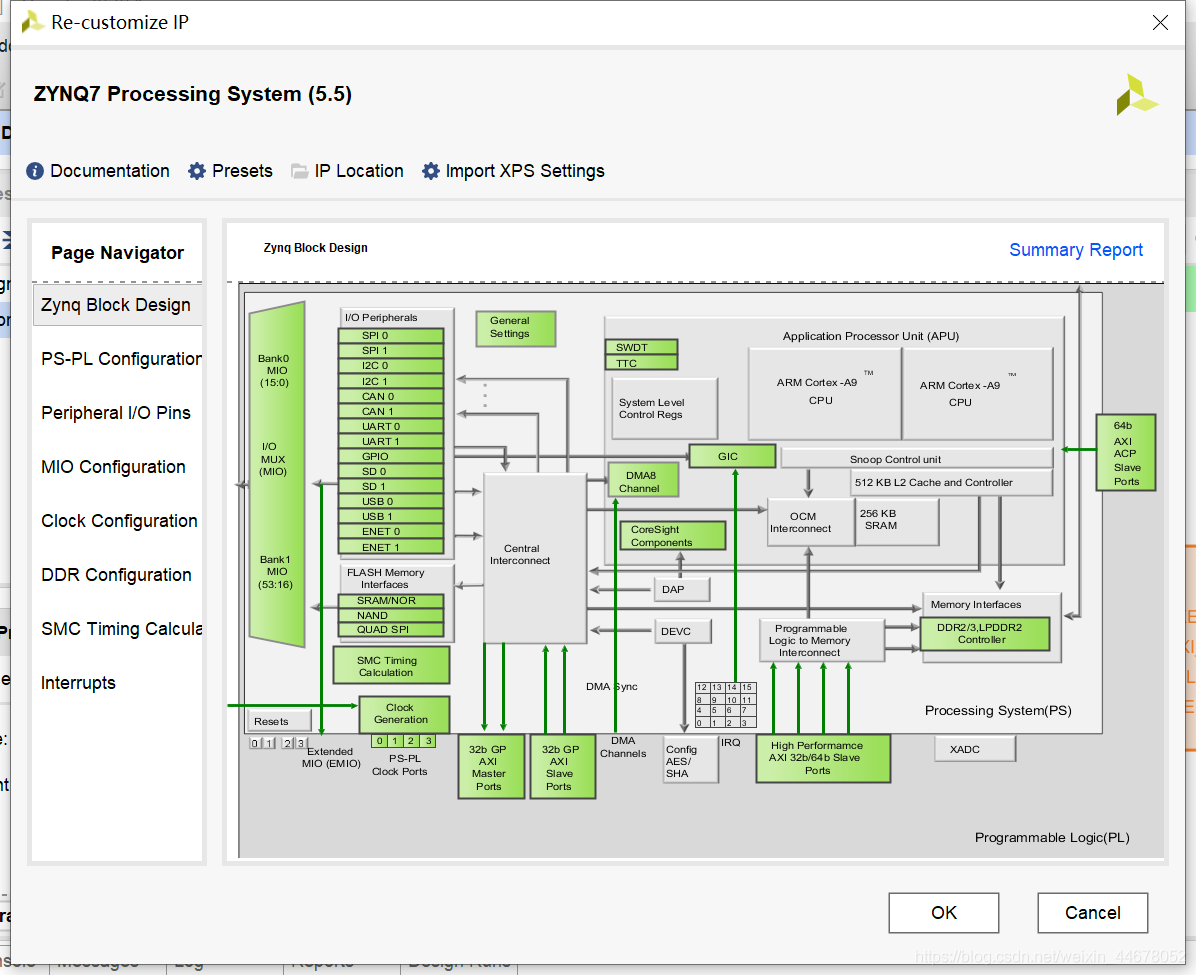

3. 双击刚刚生成的block,然后对其进行配置,从zynq block design中可以看到我们的zynq的架构长上面样子,还是挺复杂的。在输出"hello world"实验中,我们只需要配置ddr和uart即可,ddr程序运行的空间,uart用来通讯。

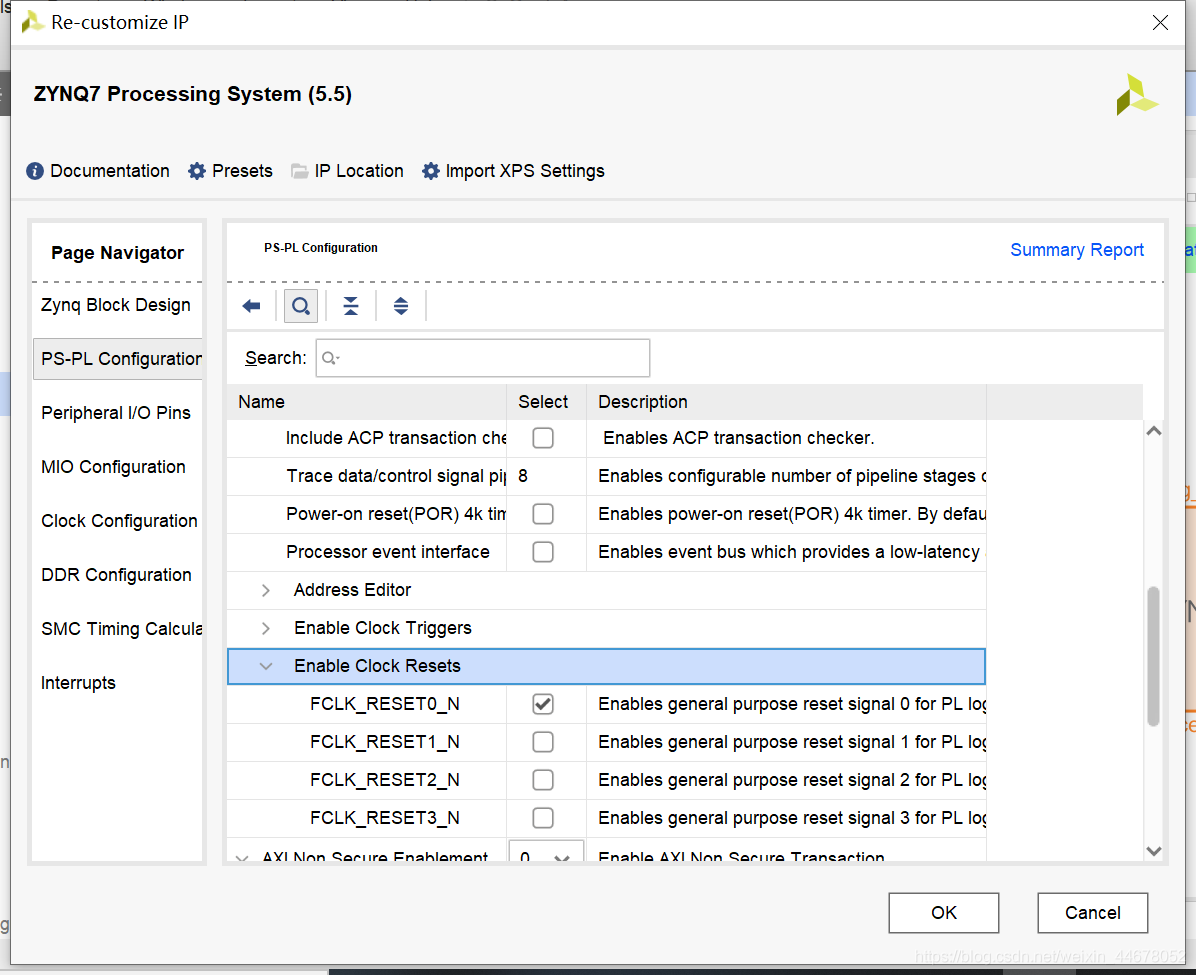

4. 将默认的多余的配置移除掉,依次取消下面的勾选项,然后点击ok,可以看到block中只剩下两个端口了,ddr和fixed_io(也就是ps端的固定io口)

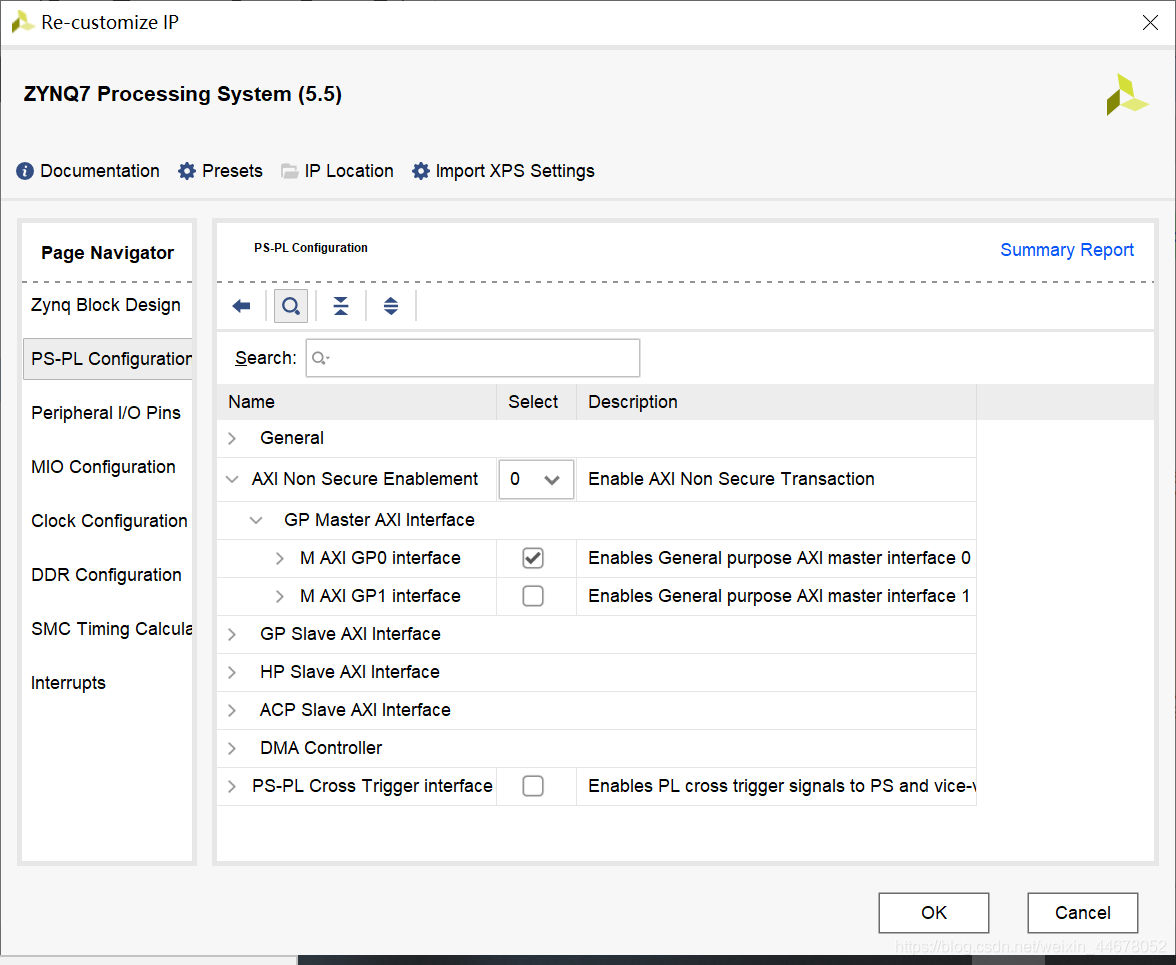

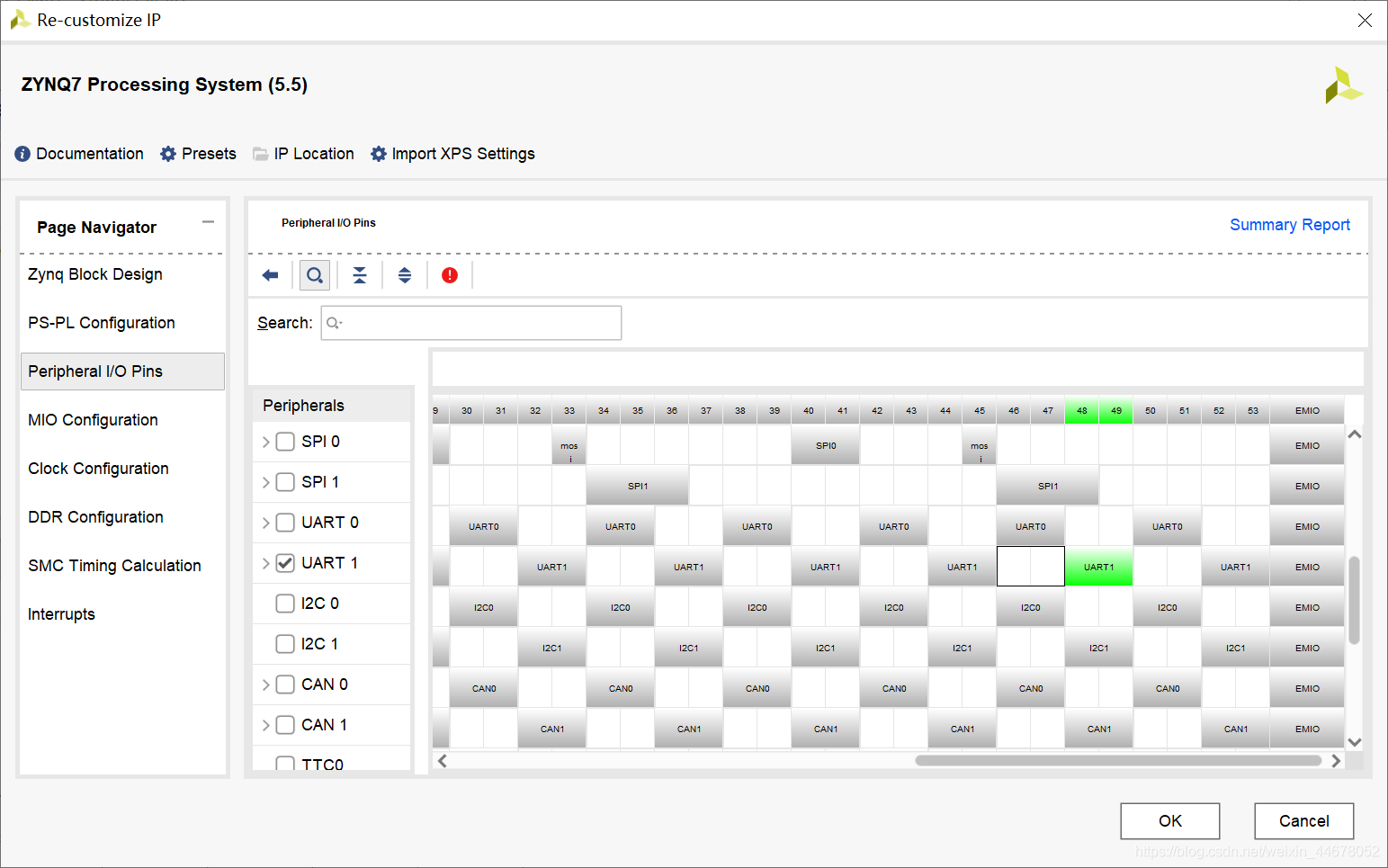

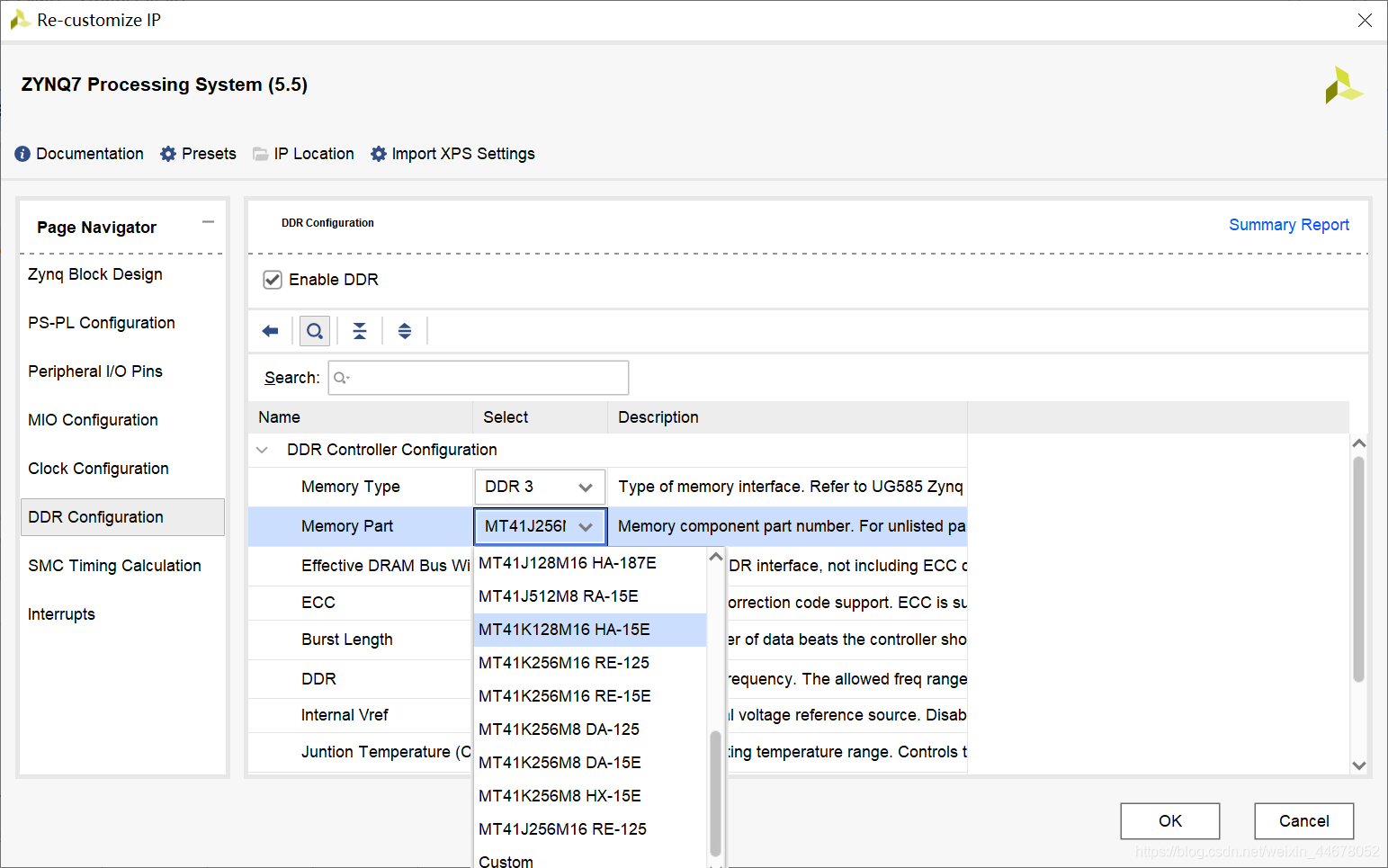

5. 再次双击block,来配置uart和ddr,勾选uart0还是uart1,已经io口号的选择,得根据原理图来,然后ddr型号选择的时候也得根据开发板上的ddr芯片的型号来。最后点击ok。

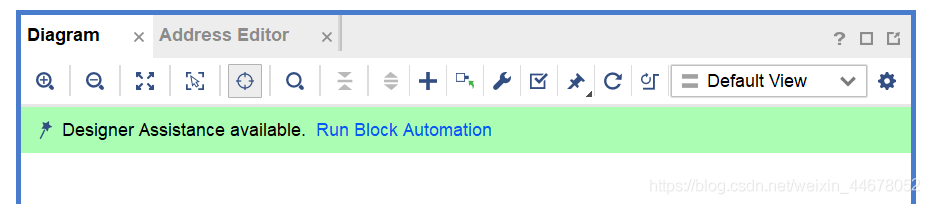

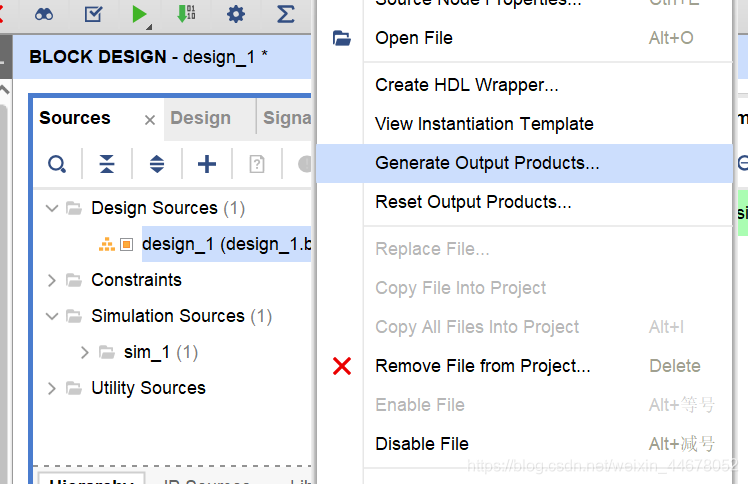

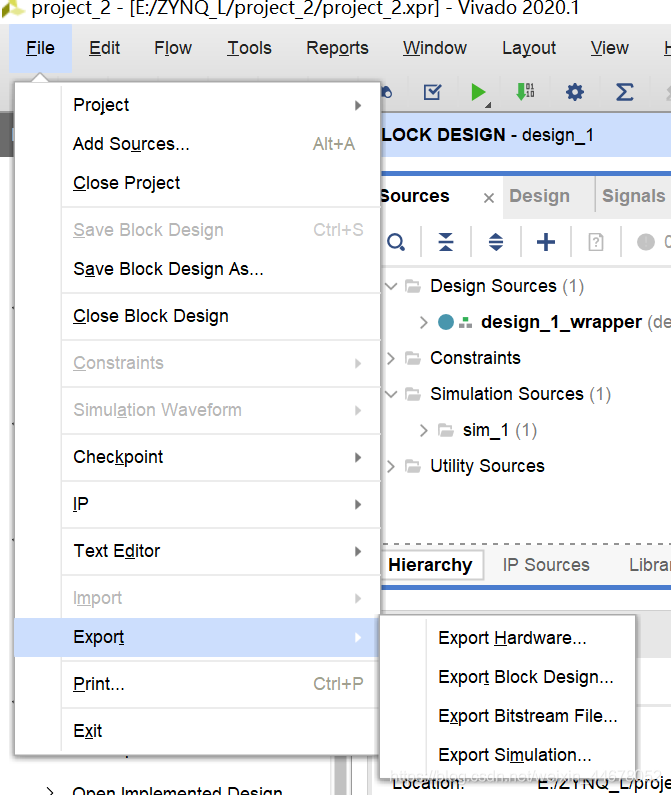

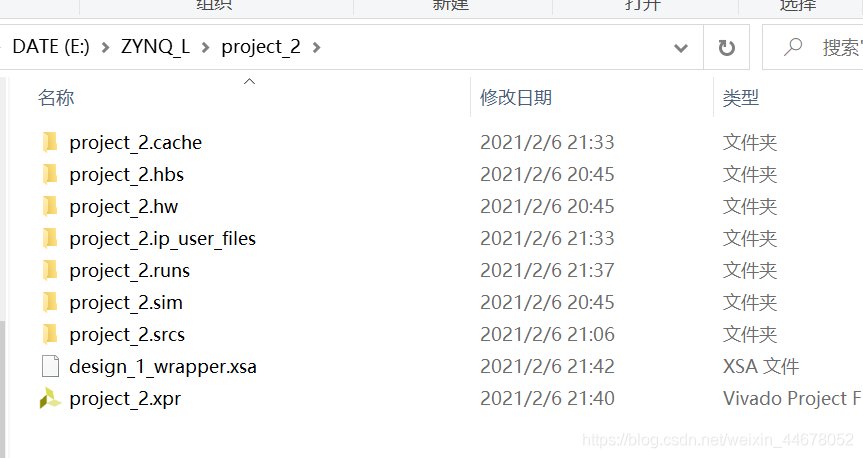

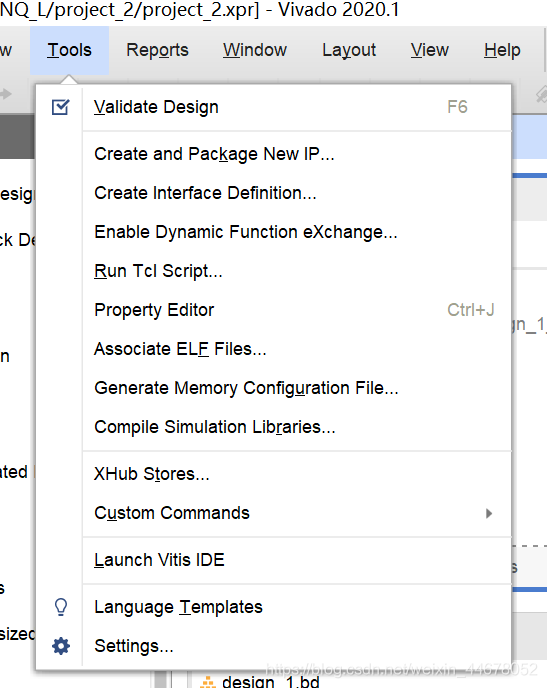

6. 点击run block automation让软件自动帮我们连线。然后,根据下面的图,先点击generate out product,然后点击Create HDL Wrapper生成top文件,完成后,直接点击generate bitstream。完成后,点击export hadrware,导出硬件信息(中途直接点击next即可),完成后,会在选择的路径中看到xsa文件了,这就是包含硬件的文件了。最后选择tool,点击launch vitis启动软件

公众号:FPGA之旅

相关文章

- 在 Go 里用 CGO?这 7 个问题你要关注!

- 9款优秀的去中心化通讯软件 Matrix 的客户端

- 求职数据分析,项目经验该怎么写

- 在OKR中,我看到了数据驱动业务的未来

- 火山引擎云原生大数据在金融行业的实践

- OpenHarmony富设备移植指南(二)—从postmarketOS获取移植资源

- 《数据成熟度指数》报告:64%的企业领袖认为大多数员工“不懂数据”

- OpenHarmony 小型系统兼容性测试指南

- 肯睿中国(Cloudera):2023年企业数字战略三大趋势预测

- 适用于 Linux 的十大命令行游戏

- GNOME 截图工具的新旧截图方式

- System76 即将推出的 COSMIC 桌面正在酝酿大变化

- 2GB 内存 8GB 存储即可流畅运行,Windows 11 极致精简版系统 Tiny11 发布

- 迎接 ecode:一个即将推出的具有全新图形用户界面框架的现代、轻量级代码编辑器

- loongarch架构介绍(三)—地址翻译

- Go 语言怎么解决编译器错误“err is shadowed during return”?

- 敏捷:可能被开发人员遗忘的部分

- Denodo预测2023年数据管理和分析的未来

- 利用数据推动可持续发展

- 在 Vue3 中实现 React 原生 Hooks(useState、useEffect),深入理解 React Hooks 的