FPGA采集DHT11温湿度

一. 简介

在温湿度传感器中,dht11是使用的最多的一个,在很多课设,毕设中是首选。仅需要一个IO口,就可以完成温湿度采集。在这里分享利用FPGA来完成DHT11温湿度采集的一个demo分享。

需要完整代码的可以关注微信公众号 FPGA之旅回复 DHT11-FPGA 获取

二. 温湿度采集

数据传输过程包括以下三个部分 : 采集开始,采集数据,采集结束。

采集开始,FPGA拉低数据线,然后释放,等待dht11响应。

采集数据为40bit,分别为(高到底) 8bit湿度整数位,8bit湿度小数位,8bit温度整数位,8bit温度小数位,8bit校验和。

校验和为温湿度数据之合的后8位。

采集结束,从机拉低数据线。

数据传输过程还是比较容易的,下面来详细说明一下各个部分的持续情况。

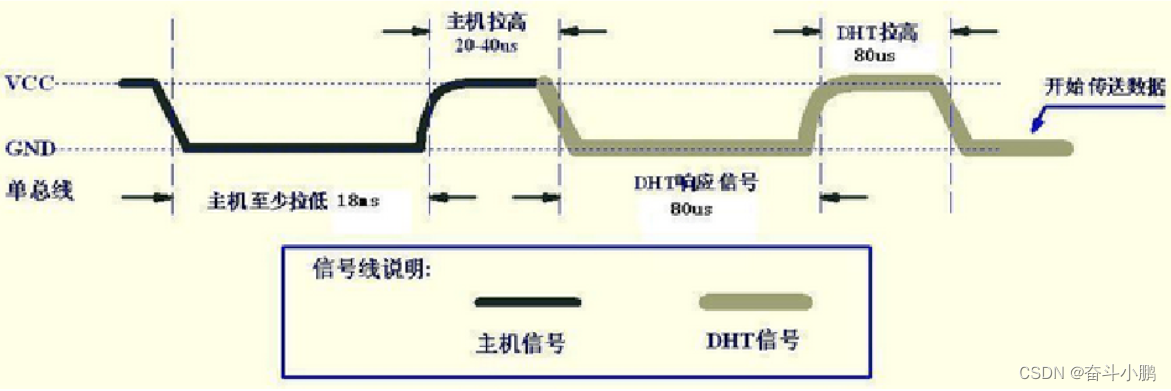

(1) 采集开始

FPGA拉低数据线最少18ms,推荐20ms。释放总线,等待从机拉低总线响应。响应接收后,总线被释放。详细过程如下。

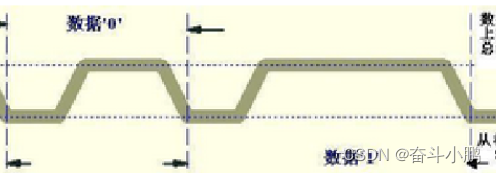

(2) 采集数据

数据表示:数据0 : 50us的低电平加26us~28us的高电平 。数据1:50us的低电平加70us的高电平

(3) 采集结束

从机拉低总线50us。

这里的时间可以根据实际测试的结果进行调整。这很重要,不然可能会出现采集到的数据不准确的情况。

三. 代码实现

需要完整代码的可以关注微信公众号 FPGA之旅回复 DHT11-FPGA 获取

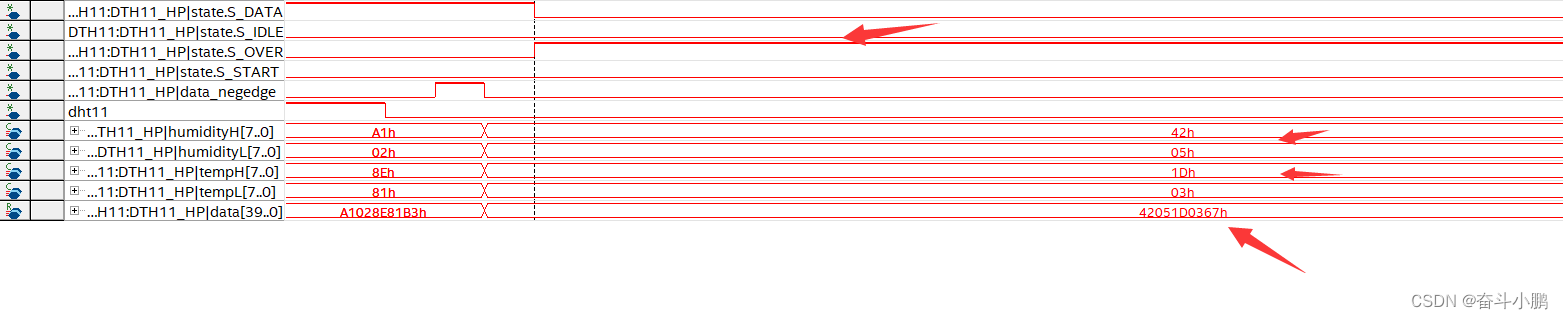

这里采用三段式状态机来实现,比较方便。由传输过程可以轻松确定整个采集过程由四个状态确定。

下面是用逻辑分析仪得到的采集结果,可以看到在S_OVER中,已经采集到了一次完整的数据。

通过计算42 + 05 + 1D + 03 = 67 (十六进制)可以确定采集到的数据是完全正确的。

module DTH11( input clk, input rst, inout dht11, input dht11_req, //数据采集请求 output dht11_down, //数据采集完成 output[7:0] tempH, //温度数据整数 output[7:0] tempL, //温度数据小数 output[7:0] humidityH, //温度数据整数 output[7:0] humidityL //温度数据小数 );

localparam S_IDLE = 'd0; //空闲状态 localparam S_START = 'd1; //开始采集数据 localparam S_DATA = 'd2; //接收采集到的数据 localparam S_OVER = 'd3; //数据采集完成

状态转移过程

S_START: 采集请求过来的时候,就进入到开始状态

S_DATA:step表示start状态中的四个部分,分别为主机拉低,从机响应开始和结束以及数据传输开始。

S_OVER:step表示接收到数据的个数,当接收到数据为40的时候,进入S_OVER状态

S_IDLE : timeCount 拉低时间结束进入S_IDLE状态。

always@(*)

always@(*) begin case(state) S_IDLE: if(dht11_req == 1'b1) next_state <= S_START; else next_state <= S_IDLE; S_START: if(step == 'd4) next_state <= S_DATA; else next_state <= S_START; S_DATA: if(step == 'd40) next_state <= S_OVER; else next_state <= S_DATA; S_OVER: if(timeCount == Time50us) next_state <= S_IDLE; else next_state <= S_OVER; default: next_state <= S_IDLE; endcase end

公众号:FPGA之旅

相关文章

- 在 Linux 下用 mkdir 命令来创建目录和子目录

- 如何在 Linux 下执行 bin 文件

- 互联网企业安全高级指南2.2 如何建立一支安全团队

- 互联网企业安全高级指南3.1 从零开始

- 互联网企业安全指南3.2 不同阶段的安全建设重点

- 互联网企业安全高级指南3.3 如何推动安全策略

- 跨越终端中多个vim实例访问剪切板内容

- 互联网企业安全高级指南3.4 安全需要向业务妥协吗

- 互联网企业安全高级指南3.5 选择在不同的维度做防御

- Ubuntu 14.04/13.10 用户怎样安装 Ubuntu Touch 核心应用

- 互联网企业安全高级指南3.6 需要自己发明安全机制吗

- Linux 系统实时监控的瑞士军刀 —— Glances

- 互联网企业安全高级指南3.7 如何看待SDL

- 戴文的Linux内核专题:19 配置内核 (15)

- 互联网企业安全高级指南3.7.1 攻防驱动修改

- 互联网企业安全高级指南3.7.2 SDL落地率低的原因

- 霍金启动太空项目:数千个邮票大小的纳米小型太空飞船起航在即...

- 互联网企业安全高级指南3.7.3 因地制宜的SDL实践

- 3D打印技术在医疗领域能做些什么?帮助精确完成手术

- 互联网企业安全高级指南3.7.4 SDL在互联网企业的发展