串行通信协议(I2C、SPI、UART、SCCB)

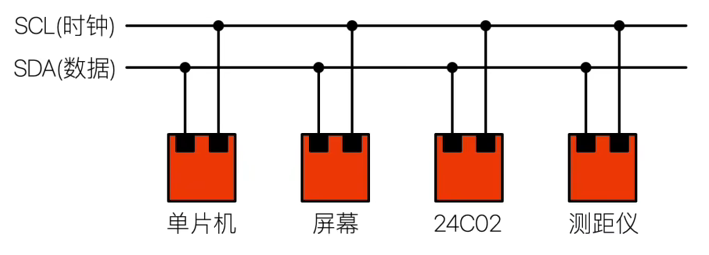

I2C(Inter-Integrated Circuit)

1.简单的双向两线制总线协议标准、半双工通信

2.双向串行数据线(SDA)用来表示数据,串行时钟线(SCL)用于数据收发同步

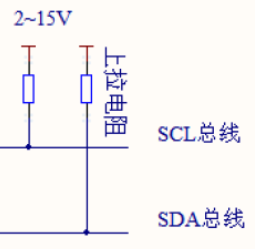

3.总线通过上拉电阻接到电源。当I2C 设备空闲时,会输出高阻态,而当所有设备都空闲,都输出高阻态时,由上拉电阻把总线拉成高电平。

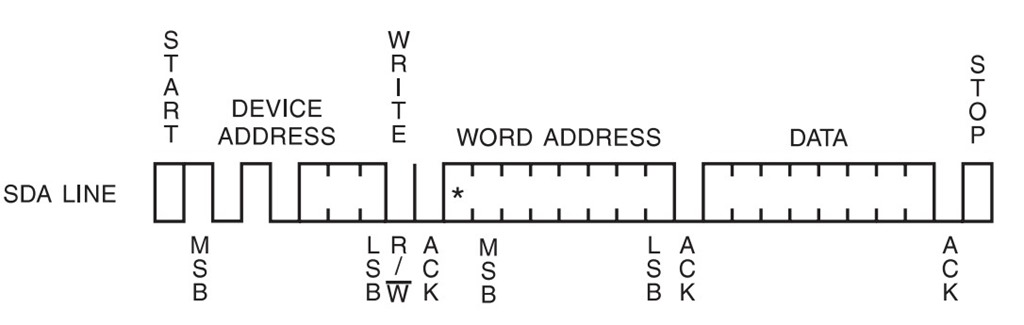

写数据

- 开始数据传输后,先发送一个起始位(S),主设备发送一个地址数据(由7bit的从设备地址,和最低位的

写标志位组成的8bit字节数据,该读写标志位决定数据的传输方向),然后,主设备释放SDA线,并等待从设备的应答信号(ACK)。- 从设备应答主设备后(表示有这个从设备存在),主设备再发送要读取的寄存器地址,从设备应答主设备(ACK),表示设备内有这个地址。

- 当写数据的时候,Master每发送完8个数据位,Slave设备如果还有空间接受下一个字节应该回答“ACK”,Slave设备如果没有空间接受更多的字节应该回答“NACK”,Master当收到“NACK”或者一定时间之后没收到任何数据将视为超时,此时Master放弃数据传送,发送“Stop”。

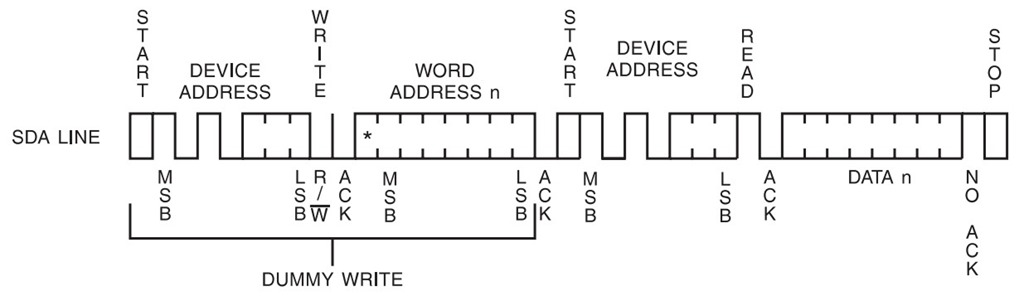

读数据

- 开始通讯时,主设备先发送一个起始信号(S),主设备发送一个地址数据(由7bit的从设备地址,和最低位的

写标志位组成的8bit字节数据),然后,主设备释放SDA线,并等待从设备的应答信号(ACK)。- 从设备应答主设备后(表示有这个从设备存在),主设备再发送要读取的寄存器地址,从设备应答主设备(ACK),表示设备内有这个地址。

- 主设备再次发送起始信号(S),主设备发送设备地址(包含

读标志),从设备应答主设备,并将该寄存器的值发送给主设备。- Slave设备每发送完8个数据位,如果Master希望继续读下一个字节,Master应该回答“ACK”以提示Slave准备下一个数据,如果Master不希望读取更多字节,Master应该回答“NACK”以提示Slave设备准备接收Stop信号。

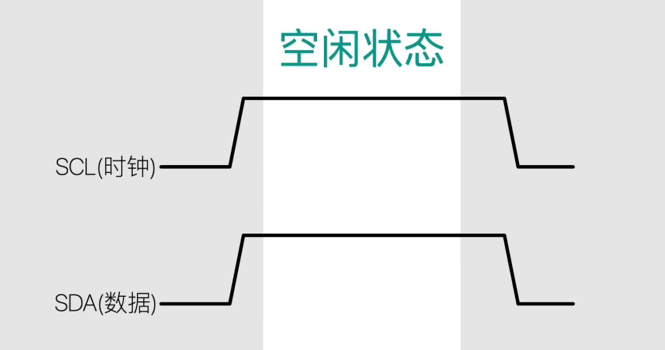

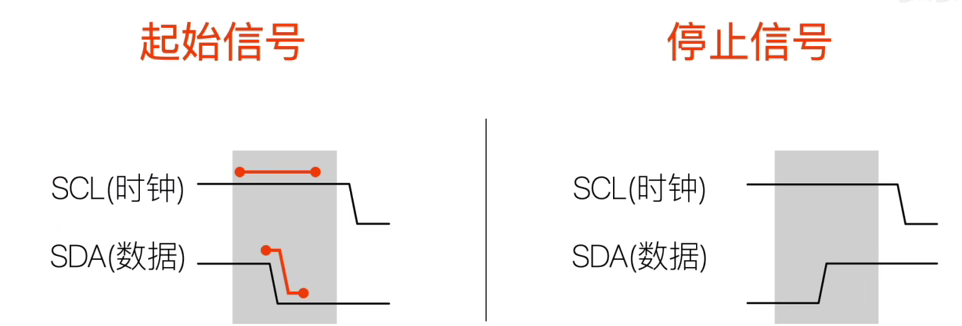

起始信号和停止信号

SCL处于高电平时,SDA由高到低变化,这种信号是起始信号

SCL处于高电平,SDA由低到高变化,这种信号是停止信号

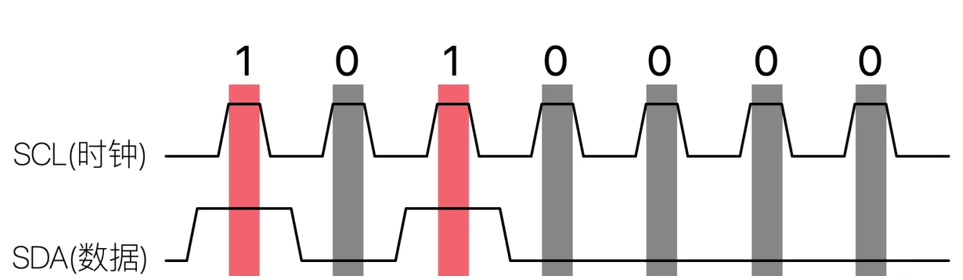

数据的有效性

在数据传输期间(不包括起始信号和停止信号),I2C协议对数据的采样发生在SCL高电平期间。SCL为高电平时,SDA必须保持稳定,不允许改变,在SCL低电平时才可以进行变化。

应答信号

I2C数据以字节(即8bits)为单位传输,每个字节传输完后都会有一个ACK应答信号。应答信号的时钟是由主设备产生的。主机需要释放SDA总线,把总线控制权交给从机,由于上拉电阻的作用,此时为高电平。

- 应答(ACK):拉低SDA线,并在SCL为高电平期间保持SDA线为低电平

- 非应答(NOACK):不要拉低SDA线(此时SDA线为高电平),并在SCL为高电平期间保持SDA线为高电平

速率

- 标准模式(Standard):100kbps

- 快速模式(Fast):400kbps

- 快速模式+(Fast-Plus):1Mbps

- 高速模式(High-speed):3.4Mbps

- 超快模式(Ultra-Fast):5Mbps(单向传输)

实现

- I2C总线协议的软件模拟实现方法–单片机

- Linux内核中I2C模块的实现方法

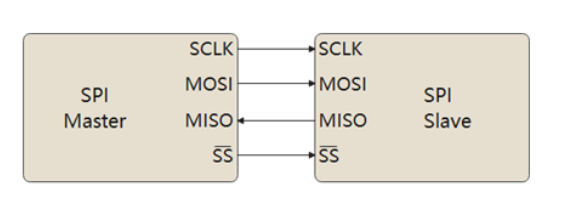

SPI(Serial Peripheral interface)

全双工数据传输、没有规定最大传输速率、没有地址方案、也没规定通信应答机制

- MISO(Master input slave output): 主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。

- MOSI(Master output slave input): 主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。

- SCLK(Serial Clock):串行时钟信号,由主设备产生。

- CS/SS(Chip Select / Slave Select):从设备片选信号,由主设备控制。它的功能是用来作为“片选引脚”,也就是选择指定的从设备,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

SPI数据发送接收

对主设备的SPI模式进行配置,通过配置时钟极性和相位设置主设备的通信模式,决定读取数据的方式,比如信号上升沿读取数据还是信号下降沿读取数据;

时钟极性 CKP/Clock Polarity/CPOL

- CPOL=0:时钟空闲SCLK=0;

- CPOL=1:时钟空闲SCLK=1;

时钟相位 CKE /Clock Phase (Edge)/CPHA

CPHA=0:在时钟的第1个跳变沿(上升沿或下降沿)进行数据采样,在第2个跳变沿(上升沿或下降沿)数据发送CPHA=1:在时钟的第1个跳变沿(上升沿或下降沿)进行数据发送,在第2个跳变沿(上升沿或下降沿)数据采样

4种模式

-

CPOL=0,CPHA=0:此时空闲态时,SCLK处于低电平,数据采样是在第1个边沿,也就是SCLK由低电平到高电平的跳变,即数据采样在上升沿,数据发送是在下降沿。 -

CPOL=0,CPHA=1:此时空闲态时,SCLK处于低电平,数据发送是在第1个边沿,也就是SCLK由低电平到高电平的跳变,即数据发送是在上升沿,数据采样是在下降沿。 -

CPOL=1,CPHA=0:此时空闲态时,SCLK处于高电平,数据采样是在第1个边沿,也就是SCLK由高电平到低电平的跳变,即数据采样在下降沿,数据发送在上升沿。 -

CPOL=1,CPHA=1:此时空闲态时,SCLK处于高电平,数据发送是在第1个边沿,也就是SCLK由高电平到低电平的跳变,即数据发送是在下降沿,数据采样在上升沿。

通信过程

- 拉低对应SS信号线,表示与该设备进行通信

- 主机(Master)将要发送的数据写到发送数据缓存区,缓存区经过移位寄存器(0~7),串行移位寄存器通过MOSI信号线将字节一位一位的移出去传送给从机,从机的MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区。

- 从机(Slave)也将自己的串行移位寄存器(0~7)中的内容通过MISO信号线返回给主机。

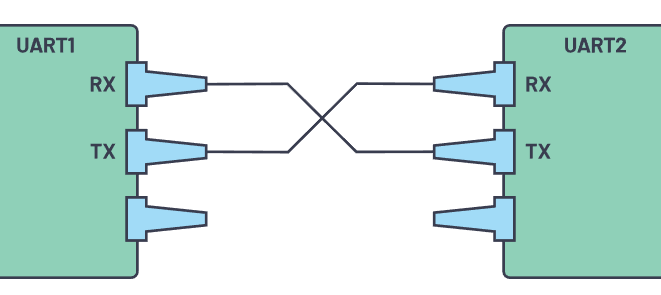

UART

通用异步收发器(Universal Asynchronous Receiver/Transmitter),通常称作UART,是一种串行、异步、全双工的通信协议。

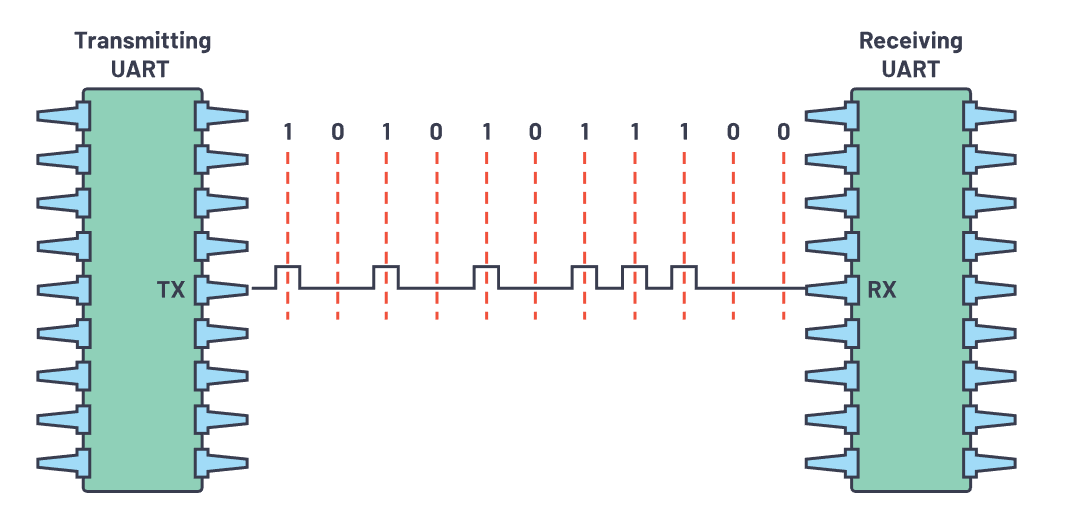

通信协议

数据包由起始位、数据帧、奇偶校验位和停止位组成。

起始位

当不传输数据时,UART数据传输线通常保持高电压电平。

若要开始数据传输,发送UART会将传输线从高电平拉到低电平并保持1个时钟周期。当接收UART检测到高到低电压跃迁时,便开始以波特率对应的频率读取数据帧中的位。

数据帧

数据帧包含所传输的实际数据。

如果使用奇偶校验位,数据帧长度可以是5位到8位。

如果不使用奇偶校验位,数据帧长度可以是9位。

在大多数情况下,数据以最低有效位优先方式发送。

奇偶校验

- 奇校验(odd parity):如果数据位中’1’的数目是偶数,则校验位为’1’,如果’1’的数目是奇数,校验位为’0’。

- 偶校验(even parity):如果数据为中’1’的数目是偶数,则校验位为’0’,如果为奇数,校验位为’1’。

停止位

为了表示数据包结束,发送UART将数据传输线从低电压驱动到高电压并保持1到2位时间。

波特率

数据传输速率使用波特率来表示,单位bps(bits per second)。

9600bps:传输一个比特需要的时间是1/9600≈104.2us。

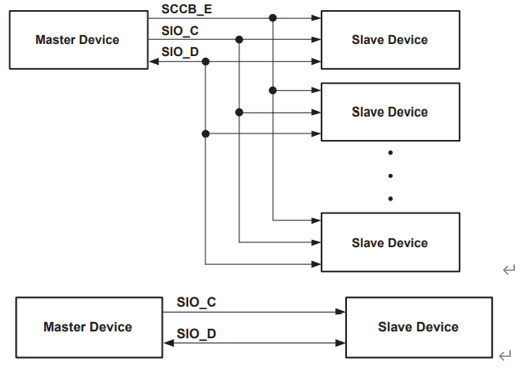

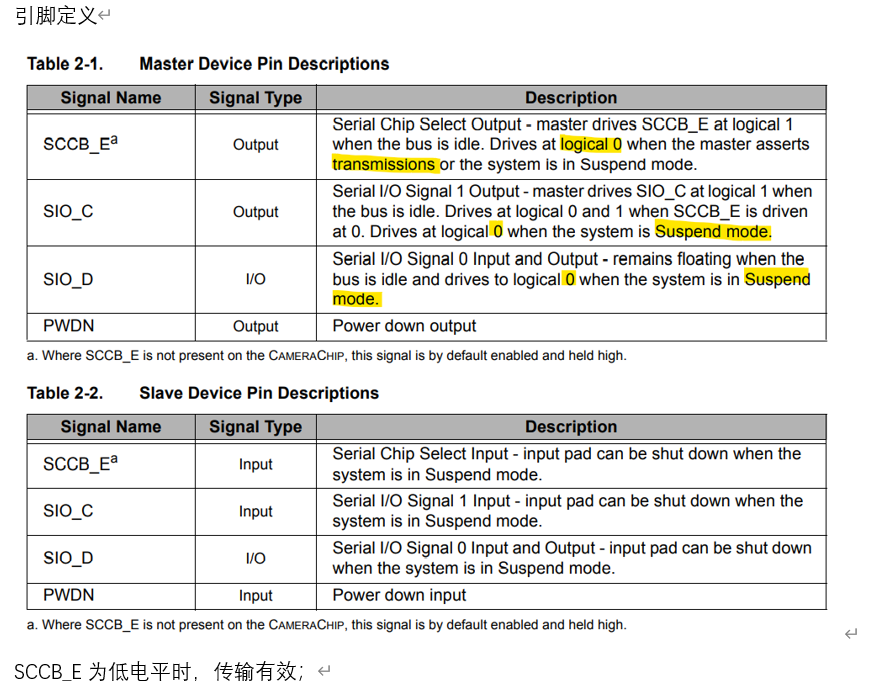

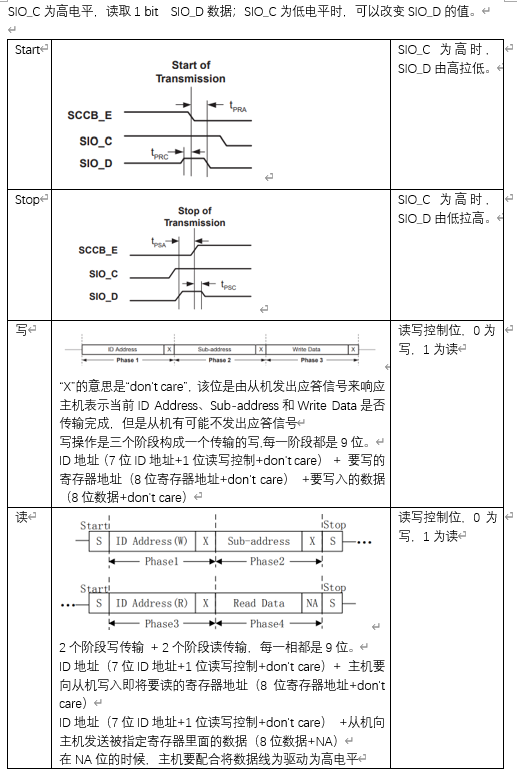

SCCB

Serial Camera Control Bus,串行摄像头控制总线,有两种工作模式,一主多从,一主一从模式。一主多从,即3线操作;一主一从,即2线操作。

通信协议

相关文章

- 直接在代码里面对list集合进行分页

- .NET Framework 4.5新特性详解

- 大数据的简要介绍

- 大数据的由来

- 高斯混合模型的自然梯度变量推理

- timing-wheel 仿Kafka实现的时间轮算法

- 使用Navicat软件连接自建数据库(Linux系统)

- 那一天,我被Redis主从架构支配的恐惧

- Redis 深入了解键的过期时间

- C#使用委托调用实现用户端等待闪屏

- 基于流计算 Oceanus 和 Elasticsearch Service 构建百亿级实时监控系统

- GRAND | 转录调控网络预测数据库

- JFreeChart API中文文档

- 临床相关突变查询数据库

- TIGER | 人类胰岛基因变化查询数据库

- 视频边缘计算网关EasyNVR在视频整体监控解决方案中的应用分析

- Apache Arrow - 大数据在数据湖后的下一个风向标

- 常见的电商数据指标体系

- AKShare-艺人数据-艺人流量价值

- MySQL中多表联合查询与子查询的这些区别,你可能不知道!